简化E203处理器的结构设计

处理器/DSP

描述

胡振波老师的E203处理器让小编受益匪浅,十分感激!E203 CPU的设计非常经典且精简,大量逻辑复用,追求极低功耗、极小面积。

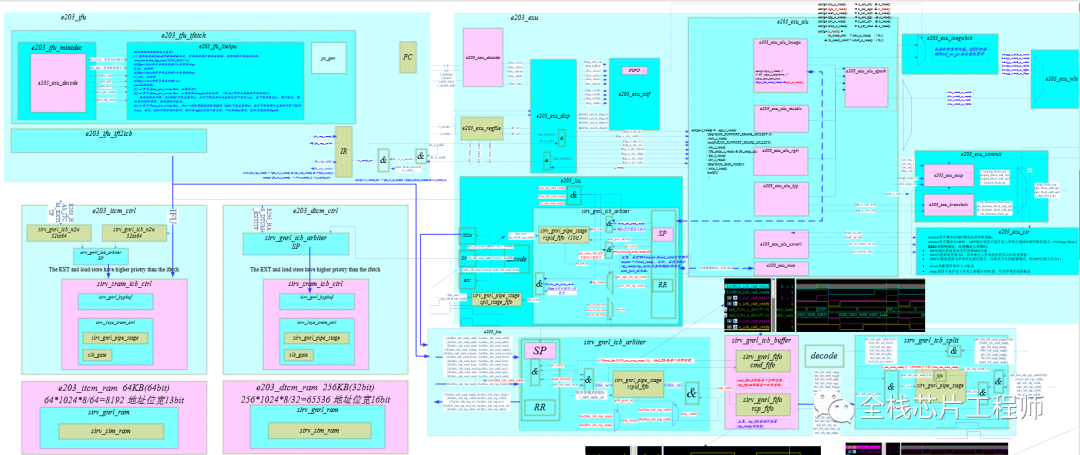

小编基于胡振波老师的E203处理器,进一步简化了CPU处理器的功能设计,分享一下小编的简化的设计架构,如下:

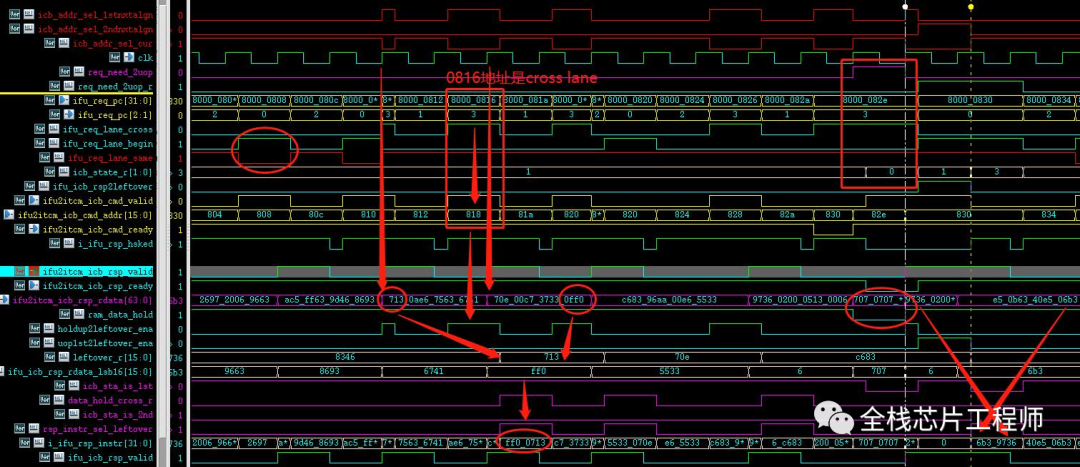

为了提高代码密度,处理器选择支持16位的压缩指令集,因此程序会出现32bit和16bit同时出现的场景,32bit指令可能存在与32位地址边界不对齐的情况,E203采用剩余缓存技术(Leftover Buffer)。

ITCM小编采用SMIC的64bit SRAM实现,读一次有64bit数据即2条指令,SRAM有读保持功能,不用外部再次寄存从而节省64bit寄存器。注意,每8个byte为一个lane。

以下波形为例,从0x8000_0810开始读,也就是一个lane的开始点开始读,

Case1:当地址边界不对齐时:

0x8000_0816时,地址0816是和0810一个lane的,但是0x16需要下一个lane的2个byte来满足每次读取32bit数据给取指令模块(16bit指令则丢弃16bit,但读取还是统一读取32bit)。此时sram数据还是data_hold状态的,因此只需要再读一下0x818的地址数据拼接即可,即0x8000_0816转成0x8000_0818读取数据取低16bit为0x0ff0,与leftover buffer的数据0x0713拼接得到最终指令数据0xff0_0713。

Case2:当地址边界不对齐时:

Sram的数据没有保持住(其他模块访问了SRAM)

或指令跳转造成的lane cross则需要读取2次sram,第一次取读取数据的高16bit,第二次取读取数据的低16bit拼接成0x06b3_9736。

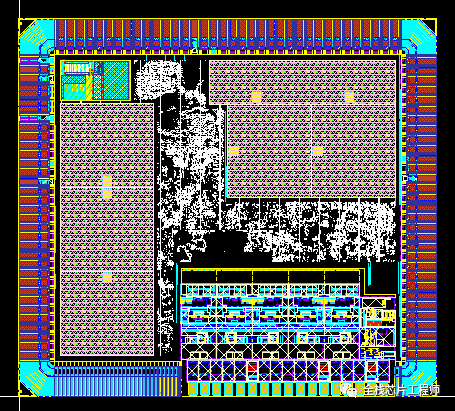

后端设计实现如下,E203 CPU的设计非常经典且精简,大量逻辑复用,追求极低功耗、极小面积。

审核编辑:汤梓红

-

浅谈产品结构设计特点2016-02-25 0

-

Cortex-M3处理器是什么2021-07-16 0

-

RK3399处理器与AR9201处理器有哪些不同之处呢2022-02-21 0

-

Sitara AM62处理器的资料分享2022-11-03 0

-

请问E203 Core和NICE协处理器的主频各是多少?2023-08-12 0

-

蜂鸟e203处理器开源代码中恶的Makefile编译脚本和测试脚本怎么修改?2023-08-12 0

-

求助,如何解决J-Link调试蜂鸟E203失败的问题?2023-08-16 0

-

嵌入式DSP处理器的体系结构设计2009-08-14 398

-

Intel 32位处理器 ,Intel 32位处理器结构原理2010-03-26 1986

-

Intel 64位处理器,Intel 64位处理器结构原理2010-03-26 3315

-

多核处理器及其对系统结构设计的影响2011-02-27 829

-

苹果a6处理器怎么样_a6处理器参数2012-09-13 25809

-

麒麟9000处理器和高通骁龙875处理器相比如何?2020-11-03 5909

-

开源Hummingbirdv2 E203 RISC-V处理器内核和SoC项目2022-03-17 1056

-

如何让HBird v2 E203跑起来?2023-05-05 971

全部0条评论

快来发表一下你的评论吧 !