浅谈UCIe对解决多芯片系统的设计

接口/总线/驱动

描述

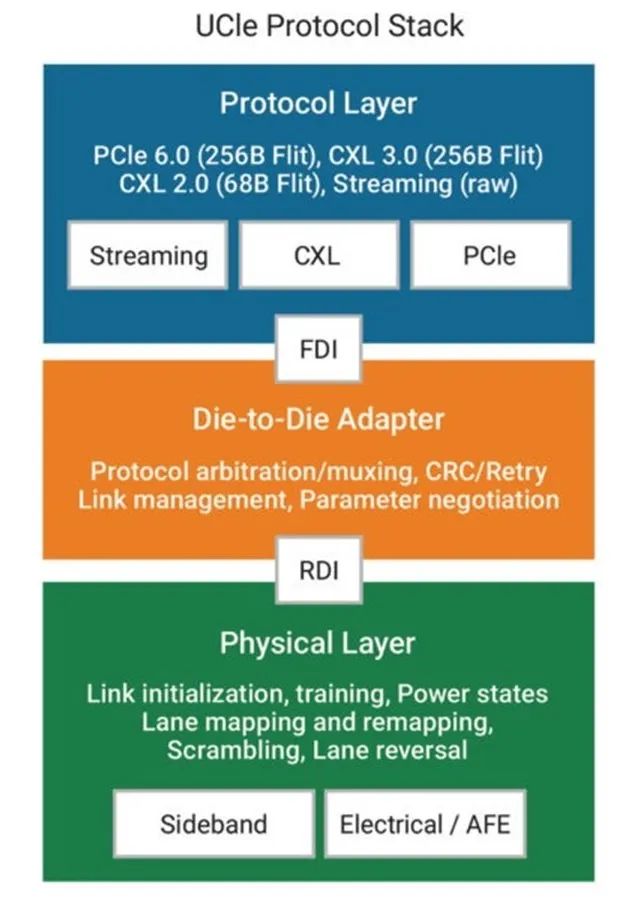

UCIe 是唯一为芯片到芯片接口定义完整堆栈的规范。

在过去几年中,专用 IC 以及高性能 CPU 和其他复杂 IC 的设计遇到四个问题。

第一,芯片尺寸变得如此之大,以至于它们可以填满整个掩模掩模版,这可能会限制未来的增长。第二,大芯片尺寸会影响制造良率,通常会导致大芯片的收益递减(制造良率降低)。第三,大型单片芯片的功耗也已达到临界水平,必须降低功耗以避免热问题。第四,需要将不同的技术与用于数字内核的先进工艺相结合——非易失性存储器、模拟和射频功能、高压驱动器、

为了应对这些挑战,设计人员已经开始分解他们的芯片设计,将大芯片拆分为现在称为小芯片的较小裸片。然而,其中存在另一个问题——在小芯片尺寸、接口和通信协议方面缺乏标准化。这反过来又限制了设计灵活性以及混合和匹配来自多个供应商的小芯片的能力。

Synopsys 产品营销经理 Manuel Mota 解释说,为了解决其中的一些问题,最近推出的通用 Chiplet Interconnect Express (UCIe) 规范大大简化了设计人员制作可定制的多芯片系统封装级集成的工作解决方案组。

Mota 预计该规范将有助于为 SoC 创新的新时代建立一个强大的生态系统。除了支持在不同工艺节点上制造的不同小芯片,每个小芯片都针对每个特定功能进行了优化,多芯片架构还允许集成来自数字、模拟或高频工艺的芯片。设计人员还可以将 3D 高密度存储器阵列(例如高带宽存储器 (HBM) 芯片堆栈)整合到 2D、2.5D 或 3D 封装配置中。

尽管 UCIe 规范刚刚推出,但在 UCIe 之前已经有几个不同的标准可以解决多芯片系统的挑战。OIF 超短距离 (XSR)、开放计算项目线束 (BOW) 和 OpenHBI (OHBI) 以及芯片联盟高级接口总线 (AIB) 是 2D 和 2.5D 封装类型的联盟和标准。这些标准提供了带宽与功率的权衡,主要侧重于提供小芯片之间的传输连接。

UCIe 是唯一为芯片到芯片接口定义完整堆栈的规范。其他标准仅关注特定层,并且与 UCIe 不同,不为协议栈的完整裸片到裸片接口提供全面的规范。正如 Mota 解释的那样,Synopsys 期待我们未来对 UCIe 规范的贡献。与促进成员 AMD、Arm、日月光、阿里巴巴、谷歌、英特尔、Meta、微软、NVIDIA、高通、三星和台积电一起,Synopsys 希望积极帮助促进 UCIe 的健康生态系统。

UCIe 不仅可以适应当今每引脚 8 Gbps 到 16 Gbps 的大部分设计,而且还可以适应从网络到超大规模数据中心的高带宽应用的每引脚 32 Gbps 的设计。UCIe 由两种封装变体组成:用于高级封装的 UCIe,例如硅中介层、硅桥或再分配层 (RDL) 扇出;和 UCIe 用于标准封装,例如有机基板或层压板。

UCIe 堆栈由三层组成。顶层协议层通过基于流控制单元(基于 FLIT)的协议实现确保最大效率并减少延迟,支持最流行的协议,包括 PCI Express (PCIe)、Compute Express Link (CXL) 和/或用户定义的流媒体协议。第二层是对协议进行仲裁和协商的地方,以及通过 die-to-die 适配器进行链路管理的地方。第三层,PHY,指定与封装媒体的电气接口。这是电气模拟前端 (AFE)、发射器和接收器以及边带通道允许两个裸片之间进行参数交换和协商的地方。逻辑 PHY 实现链路初始化、训练和校准算法以及测试和修复功能。

无论主要目标是高能效、高边缘使用效率、低延迟,还是以上所有目标,UCIe 规范都有极具竞争力的性能目标。为Synopsys 提供了完整的 UCIe 解决方案,允许设计人员通过 PHY、控制器和验证 IP (VIP)将规范付诸实践 。

PHY 接口支持标准和高级封装选项,可用于高级 FinFET 工艺,以实现高带宽、低功耗和低延迟的芯片对芯片连接。控制器 IP 支持 PCIe、CXL 和其他广泛使用的协议,用于通过流协议实现延迟优化的片上网络 (NoC) 到 NoC 链路,例如,桥接到 CXS 接口和 AXI 接口。最后,用于 UCIe 的 Synopsys 验证 IP (VIP) 在全堆栈的每一层都支持各种被测设计 (DUT)。VIP 包括带/不带 PCIe/CXL 协议栈的测试台接口、用于边带服务请求的应用程序编程接口 (API) 和用于流量生成的 API。协议检查和功能覆盖在每个堆栈层和信令接口。

Synopsys 解决方案可实现稳健且可靠的裸片到裸片链接,具有可测试性功能,用于已知良好裸片和 CRC 或奇偶校验以进行纠错。它使设计人员能够在裸片之间构建无缝互连,以实现最低延迟和最高能效。对于多芯片系统设计,由于多个流协议而导致的有效载荷增加可能需要数天甚至数月的时间进行模拟,从而限制了它的实用性。

为了验证多芯片系统,设计人员可以首先创建各种单节点和多节点模型,模拟这些极简系统以检查数据的完整性。一旦测试了这些场景,设计人员就可以使用 Synopsys ZeBu 仿真系统在具有多协议层的更高级别的系统场景中进行测试,然后使用Synopsys HAPS 原型系统进行原型设计。使用验证 IP 和其他协议验证解决方案,从模型到仿真再到仿真再到原型设计的流程,将确保芯片前的无缝互操作性。

多芯片系统设计是使系统超越摩尔定律限制的绝佳选择。有了它,设计人员可以实现更高水平的效率和性能,同时减少功耗和面积。UCIe 正在帮助快速跟踪这种为高级应用程序设计的新方法。

编辑:黄飞

-

使用UCIe IP确保多Die系统可靠性2023-11-16 657

-

新思科技发布40G UCIe IP,加速多芯片系统设计2024-09-11 615

-

Chiplet芯片互联再进一步,AMD、ARM、英特尔联手发布UCIe 1.0标准2022-03-04 2039

-

UCIe 1.0标准统一后对半导体行业有何影响2022-03-08 2085

-

芯原股份正式加入UCIe产业联盟2022-04-02 1330

-

一站式定制芯片及IP供应商灿芯半导体加入UCIe产业联盟2022-04-20 2764

-

一文解析UCIe技术细节2022-10-10 3033

-

为什么UCIe是多芯片系统的集成互连2023-05-05 1096

-

行业资讯 I 一文了解通用小芯片互联技术 (UCIe) 标准2022-10-18 1298

-

设计更简单,运行更稳健,UCIe标准如何“拿捏”Multi-Die系统?2023-07-14 1110

-

技术与计算负载如何驱动多芯片系统2023-09-18 579

-

英特尔展示全球首款基于UCIe连接的Chiplet CPU2023-09-20 1007

-

深度详解UCIe协议和技术2023-12-11 2770

-

新思科技与英特尔在UCIe互操作性测试进展2024-04-18 740

-

新思科技发布全球领先的40G UCIe IP,助力多芯片系统设计全面提速2024-09-10 416

全部0条评论

快来发表一下你的评论吧 !