C-PHY与MIPI D-PHYSM和M-PHY相比如何?

接口/总线/驱动

描述

权衡利弊,挑战和采纳

Ashraf Takla, Mixel, Inc., CEO

(2018年4月首次发布。于2022年3月更新。)

MIPI C-PHYSM于2014年10月面世,让人既兴奋又担忧。这个新的C-PHY与MIPI D-PHYSM和M-PHY相比如何?C-PHY有什么不同,它是否与D-PHY足够兼容,以便两者可以在一个混合子系统中共存?

多年后的今天,答案已经很清楚了。

本文将阐述这些答案,提供D-PHY和C-PHY架构的高层次概述,突出其相似性和差异性,确定每种PHY的优点和缺点,并提供在实施C-PHY时遇到的一些挑战的见解。最后,我们将研究Mixel对C-PHY/D-PHY组合IP的创新实现,从多个来源获得的硅结果,涵盖使用案例,并检查C-PHY/D-PHY组合解决方案在市场上的采用情况。

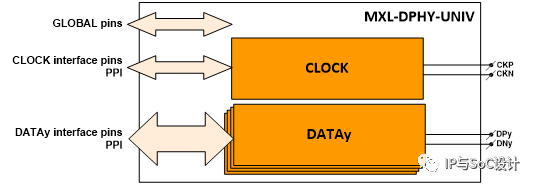

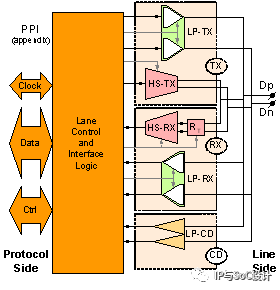

让我们首先仔细看看D-PHY,它自2009年以来就已经存在,因此得到了更好的理解和广泛应用。D-PHY是一种简单的源同步PHY,使用一个时钟通道和不同数量的数据通道。四个数据通道的D-PHY的框图如图1所示,每个通道的细节如图2所示。由于D-PHY在市场上已经存在了近十年,因此有丰富的文献涵盖了它的独特功能和使用情况(1)。

图 1:四数据通道 D-PHY 框图

图 2:D-PHY 数据通道的框图

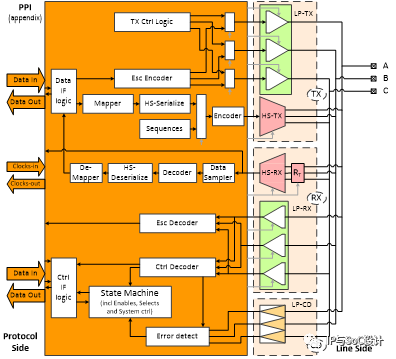

相比之下,C-PHY是一种更新、更复杂的PHY。它在三个信号上运行,三合一,时钟被嵌入到数据中,从而不需要单独的时钟通道。C-PHY的框图如图3所示。

图 3:C-PHY 框图

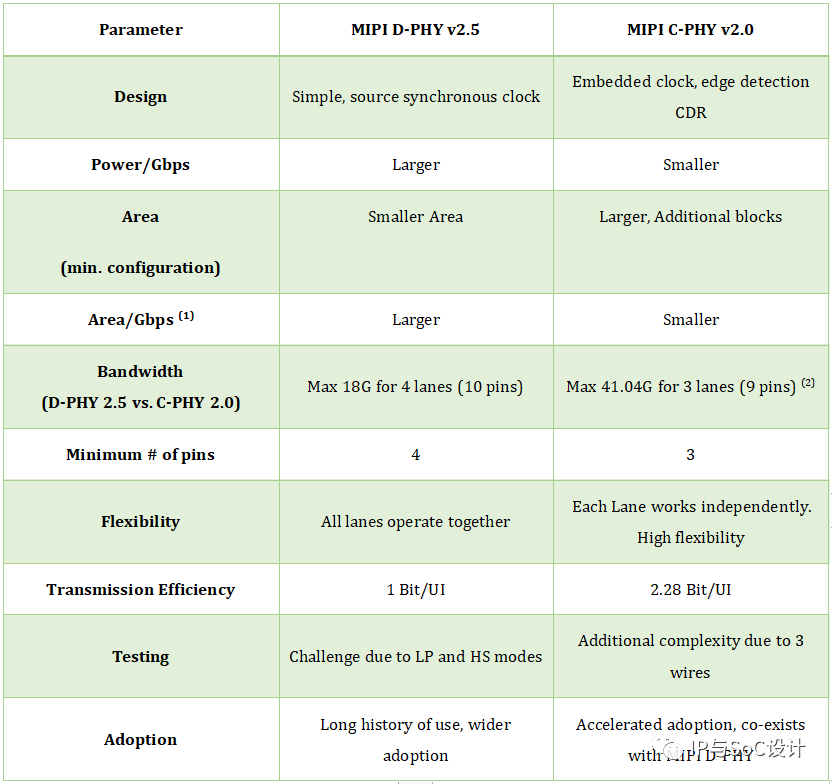

表1对D-PHY和C-PHY进行了比较。

Table 1: C-PHY vs. D-PHY parameters comparison

注释:

(1) 四个数据D-PHY通道与三个MIPI C-PHY三通道相比

(2) 编码带来的更高带宽

C-PHY使用编码数据来打包16/7≈2.28位/符号,而D-PHY不使用任何编码。正因为如此,与D-PHY相比,C-PHY可以实现更高的数据速率,同时以相同的转换或符号速率运行。

乍一看,C-PHY的工作原理,以及潜在的C-PHY/D-PHY组合似乎很神秘。C-PHY信令是多级的,但它的接收器不需要检测多级之间的差异!这是怎么回事?为什么C-PHY和D-PHY有明显的差异,但它们不仅可以共存,而且可以有效地结合成一个IP?D-PHY使用差分信号,而C-PHY使用三重信号。它们有可能一起工作吗?如何有效地实现C-PHY/D-PHY的组合,使用所有的D-PHY构建模块,而没有任何重复?每个符号的数据位数的比率16/7是怎么来的?有这么多的问题需要思考!

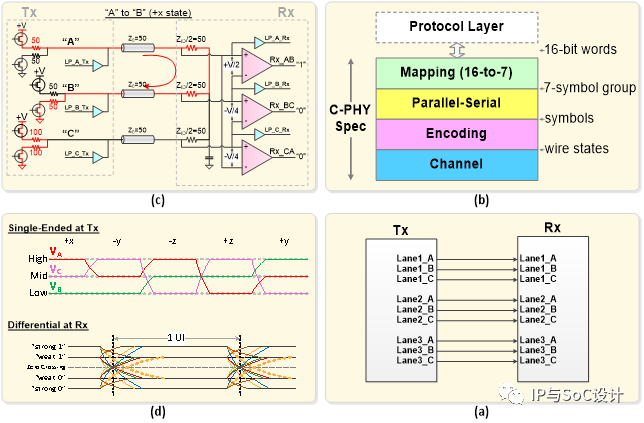

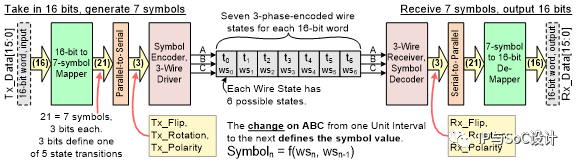

让我们尝试着回答这些问题,首先试着揭开C-PHY的神秘面纱。这并不是一件容易的事。在下面的图4中,我们提供了一个C-PHY的快速概述。图4(a)中的框图显示了一个三通道的C-PHY的TX和RX是如何连接的。图4(b)显示了C-PHY子系统的不同子块,即映射、并行/串行功能、编码和通道。图4(c)是TX和RX之间交互的更详细的图片,图4(d)说明了C-PHY的信令级别。

图 4:C-PHY (a) TX 和 RX 连接,(b) C-PHY 子系统中的不同功能,(c) 详细的 TX 和 RX 交互,(d) TX 和 RX 输出的 C-PHY 信号电平

一个C-PHY车道是由A、B、C三者组成的,如上图4(c)所示。C-PHY的接收器由3个差分RX组成,每个都是看3个信号中的2个的差分,即(A-B)、(B-C)和(C-A)。

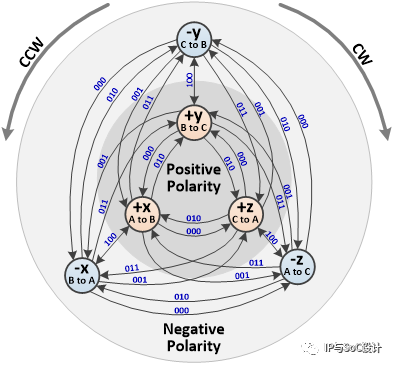

C-PHY的编码器保证(i)每个符号至少有一个边缘/转换,(ii)所有三个RX的差分输入都是非零,(iii)所有3个信号的共模是恒定的。上述(ii)和(iii)项是通过限制TX信号在任何单一单位间隔(UI)内的组合为高、中、低,以及保持三个信号中每个信号的电压水平不同来实现的。符合上述限制(i)的三个TX信号水平的组合,即高、中、低,可以得到6个不同的信号水平组合(线态)。线路状态的数量,6,是三个TX信号电平的排列组合,3! 此外,C-PHY编码器将翻转、旋转、极性符号编码为基于编码器规则的状态变化。

为了保证每个符号至少有一个边缘,上述第(i)项,C-PHY 在从一个符号移动到下一个符号时必须在不同的线路状态之间转换,并且不能在两个连续的符号中保持相同的线路状态。由于这一限制,在六个线态之间有五个不同的独特转换。这意味着编码数据有五种不同的可能性,即每个符号有五种可能的状态,使 C-PHY 成为五进制系统或四进制系统。这样我们就在二进制系统和四进制系统之间移动。这就是为什么需要C-PHY映射器的原因。现在我们使用的是五进制系统,比特/符号的最大理论数量是log2(5)=2.3219。 映射器功能的构建是为了使映射率尽可能接近而不超过该理论极限。此外,映射器必须在两个整数之间进行映射。选择比率16/7≈2.28是为了实现上述限制。

另一种描述方式是,映射器需要将16个二进制位映射到一定数量的C-PHY符号,但我们如何确定映射到多少个符号(S)?在并行接口上有2^16种组合,映射器输出端的组合是5^S => 2^16,所以S = 7。

图 5:C-PHY 编码和映射功能概述

要理解为什么C-PHY接收器只需要检测输入信号的极性,而不是多振幅信令的振幅,我们只需要记住,信号振幅中没有嵌入数据。多振幅信令仅用于增加可能的转换次数,并保证每个符号至少有一个转换。

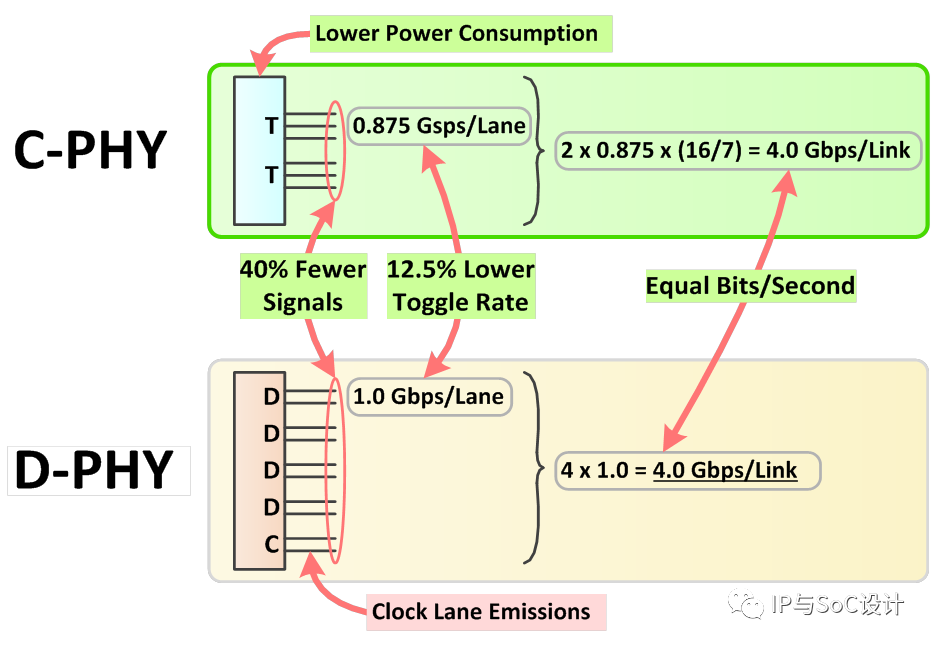

在C-PHY和D-PHY的性能之间做一个相似物比较的方法是,当它们支持4.0Gbps的总数据速率并以类似的转换速率运行时,对它们进行比较。对于D-PHY来说,这可以通过使用四通道D-PHY来实现,使用10条数据线,每个通道以1.0Gbps/通道运行。为了获得与C-PHY相同或更低的转换速率的总数据速率,我们可以使用具有6根线的双通道C-PHY,以0.875Gsps运行,低于D-PHY的1.0Gsps。在这种情况下,C-PHY的总数据速率是2 * 0.875 * 16/7 = 4Gbps。这种比较显示在下面的图6中。

图 6:支持 4Gbps 聚合数据速率并使用相同转换速率的 D-PHY 和 C-PHY 之间的比较

基于这种比较,C-PHY有更少的电线(最多减少40%),更低的切换率/通道(降低12.5%),更低的功耗(降低约20-50%),更少的通道数量,因此相同Gbps的面积更小,并且没有时钟通道的消耗。

因此,当比较C-PHY和D-PHY在相同的总数据速率下,C-PHY有很多优势;更少的引脚和焊球(由于每个引脚的性能更高)、灵活性,因为每个C-PHY通道是独立的,带有嵌入式时钟,可以将一条通道从一条链路借用到另一条链路,同时与MIPI D-PHY共存于同一引脚上。C-PHY还允许在更高的数据率应用中降低功率。此外,C-PHY的嵌入式时钟通道可以将应用处理器上的任何通道分配给任何链路,并消除了时钟杂散发射,这在多频段无线设备中尤为重要。

C-PHY的嵌入式控制代码还能够有效地支持新兴的功能,如快速总线周转(BTA)操作,对时间敏感链路的低延迟(LRTE),以及备用低功耗模式(ALP),这将通过消除单端LP模式实现更长的传输距离,从而减少面积。最后,C-PHY较低的切换率通常可以简化制造,降低低成本产品的成本,例如低端相机。

现在我们已经了解了C-PHY和D-PHY的各个属性,我们可以列举出C-PHY和D-PHY组合的一些优势。这包括能够共享串行接口引脚,重用LP(低功耗)模式,共享公共块,从而减少面积,降低功率/Gbps,在MIPI D-PHY和MIPI C-PHY之间平稳过渡,利用MIPI C-PHY的功率/性能/面积(PPA)改进,同时保持与MIPI D-PHY的兼容性。

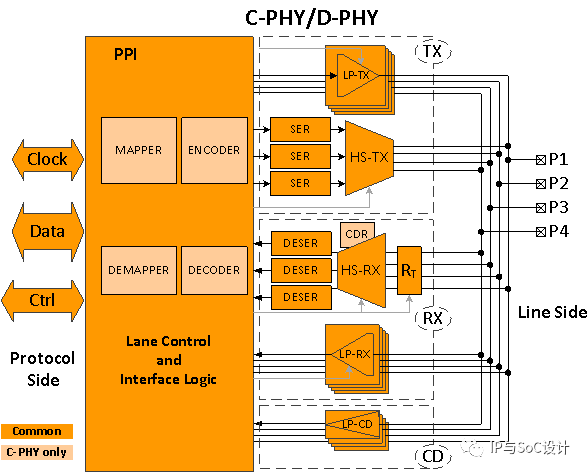

Mixel的C-PHY/D-PHY组合IP的实现是独一无二的。所有的D-PHY块都被重新用于C-PHY操作(HS-TX、HS-RX、SER、DESER、LP-TX、LP-RX和LP-CD),使支持C-PHY的面积开销最小化。虽然所有的块都被重复使用,但编码器、解码器、CDR、映射器和解映射器是C-PHY功能所需的附加模块。Mixel实现的框图如图7所示。

图 7:C-PHY/D-PHY 组合 IP 框图

Combo C-PHY/D-PHY已经由Mixel在许多不同的节点和代工厂实现。事实上,Mixel的MIPI IP已经在12个不同的节点和8个不同的代工厂进行了硅验证。

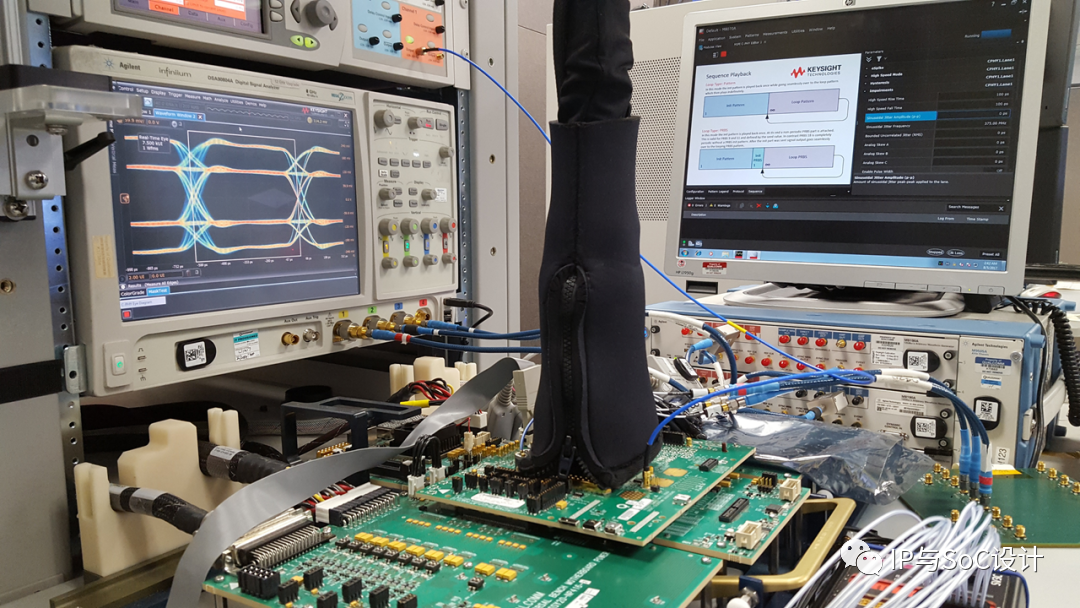

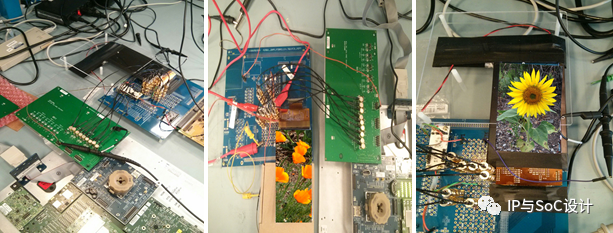

下面我们展示了C-PHY和D-PHY发射器的测试设置和芯片评估。

图 8:MIPI C-PHY 发射机测试设置

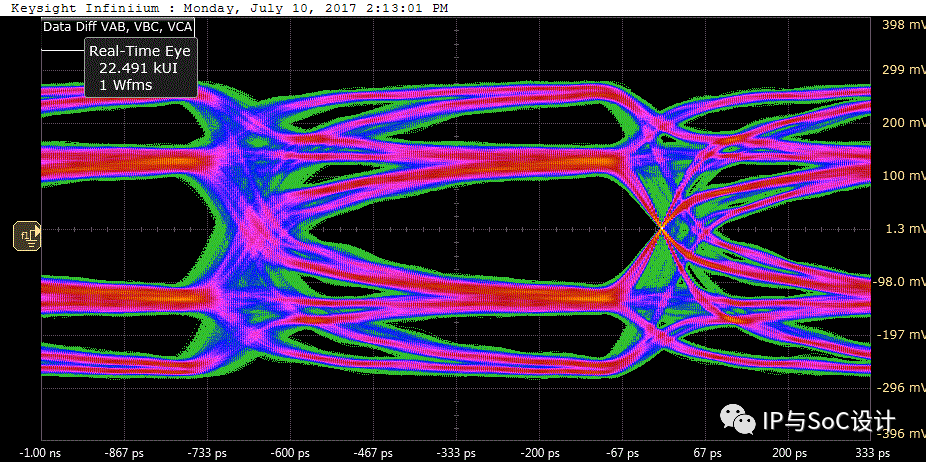

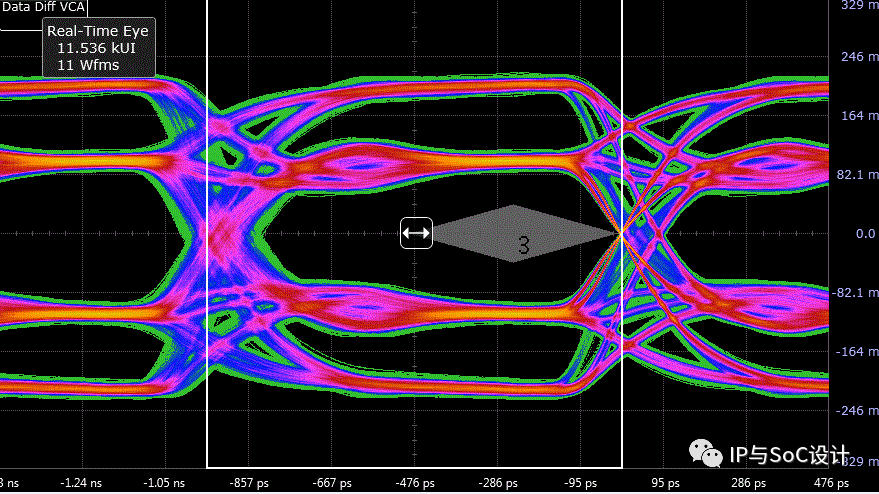

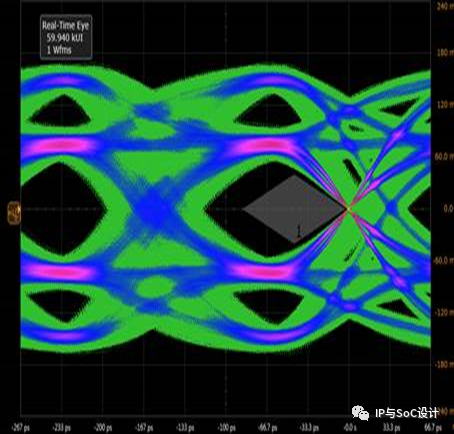

1.5Gsps

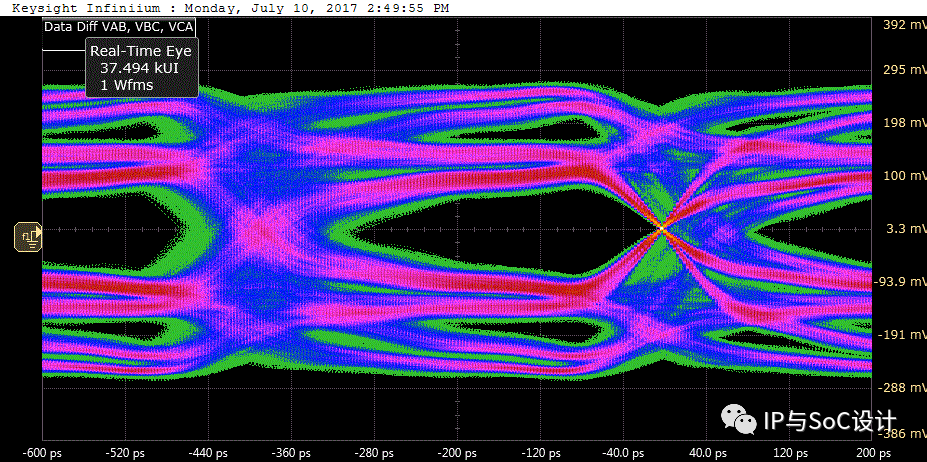

2.5Gsps

图 9:芯片结果:TX MIPI C-PHY – 眼图(Mixel)

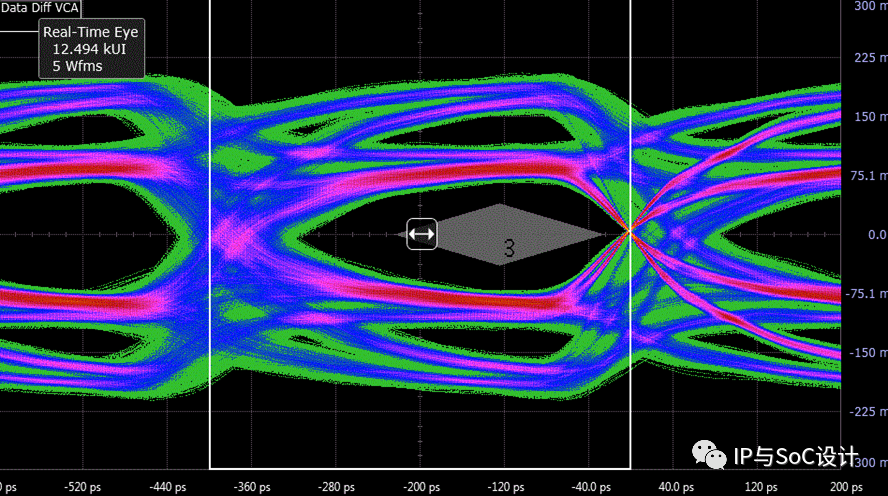

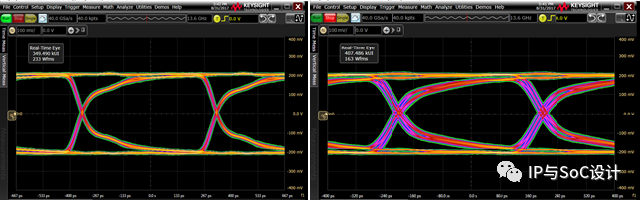

1.05Gsps @ std channel

2.5Gsps @ short channel

2.5Gsps @ std channel

图 10:芯片结果:TX MIPI C-PHY – 眼图(高通)

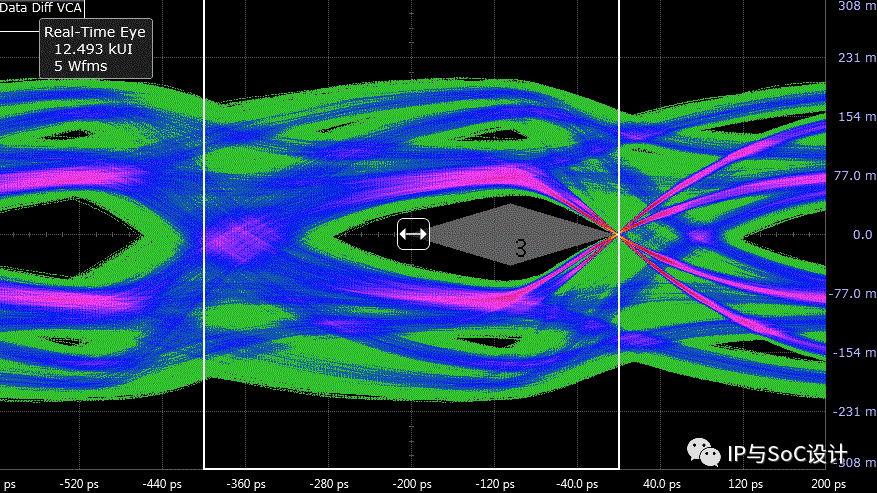

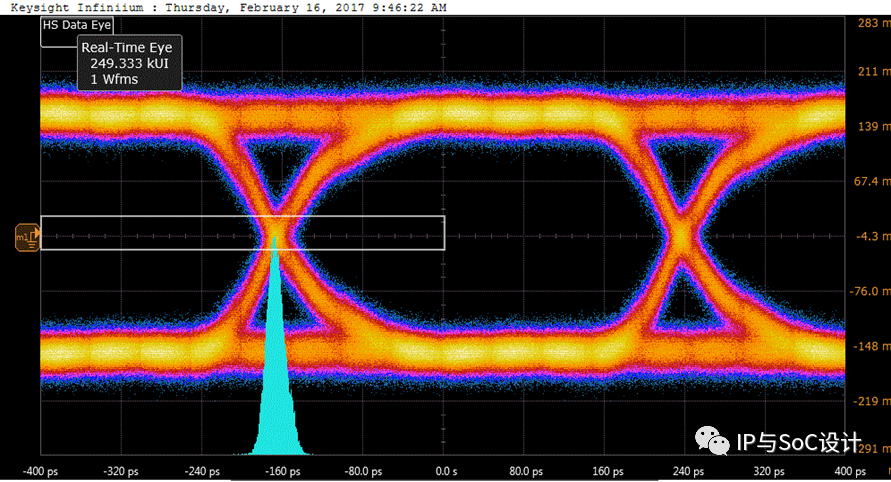

3.5Gsps @ standard channel

6.5Gsps @ short channel

图 11:芯片结果:TX MIPI C-PHY – 眼图(索尼)

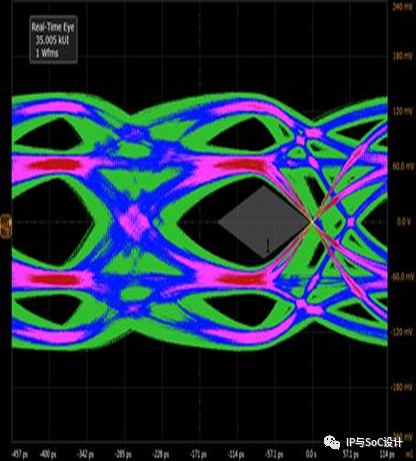

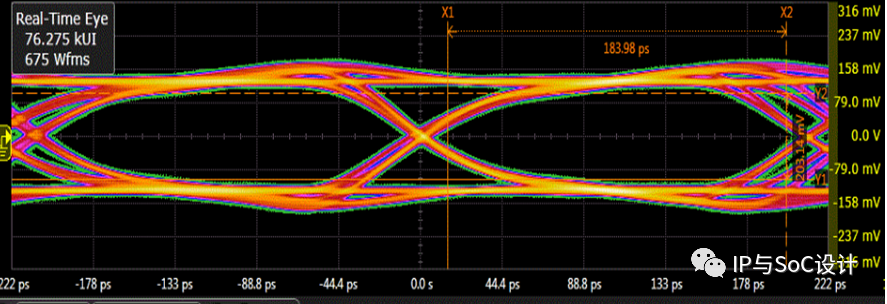

1.5Gbps 2.5Gbps

图 12:芯片结果:TX MIPI D-PHY – 眼图(Mixel)

2.5Gbps @ short channel

4.5Gbps @ short channel

图13:芯片结果:TX MIPI D-PHY - 眼图(高通)

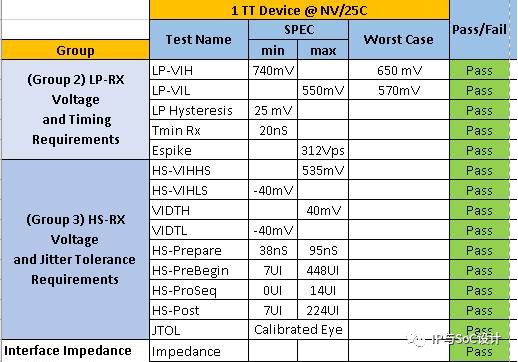

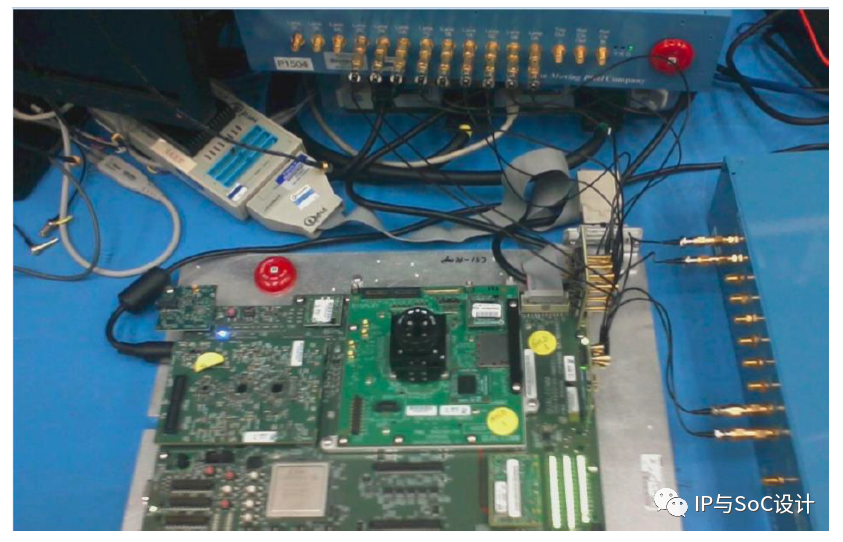

下面我们展示了C-PHY和D-PHY接收器的测试设置和硅评估。

图14:芯片结果:RX MIPI C-PHY-电气(高通公司)

图 15:芯片结果:RX MIPI C-PHY – 链路(高通)

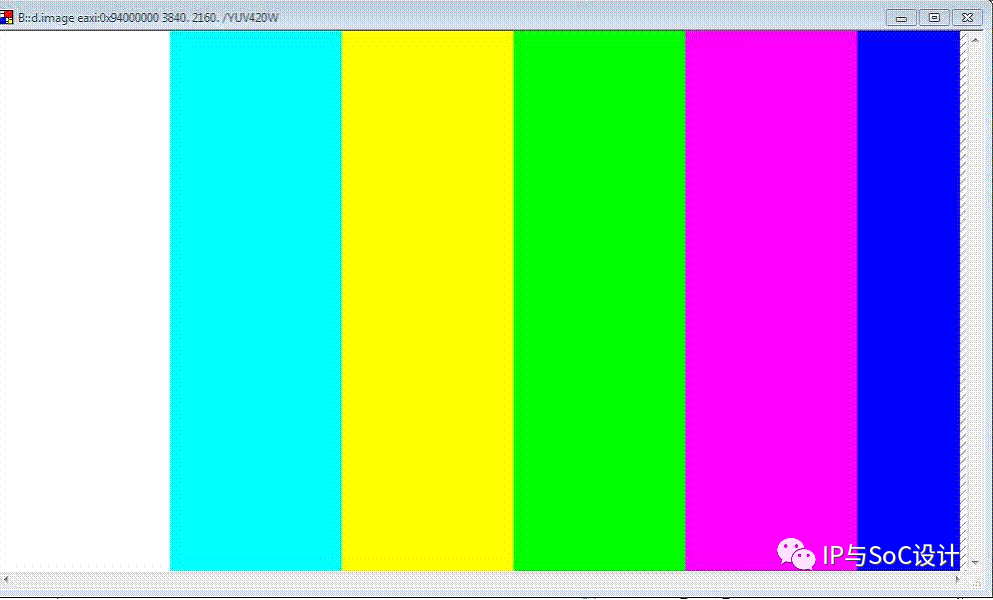

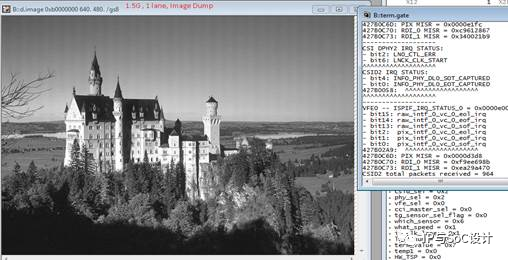

图 16:示例用例:摄像头调出

图 17:示例用例:显示调出

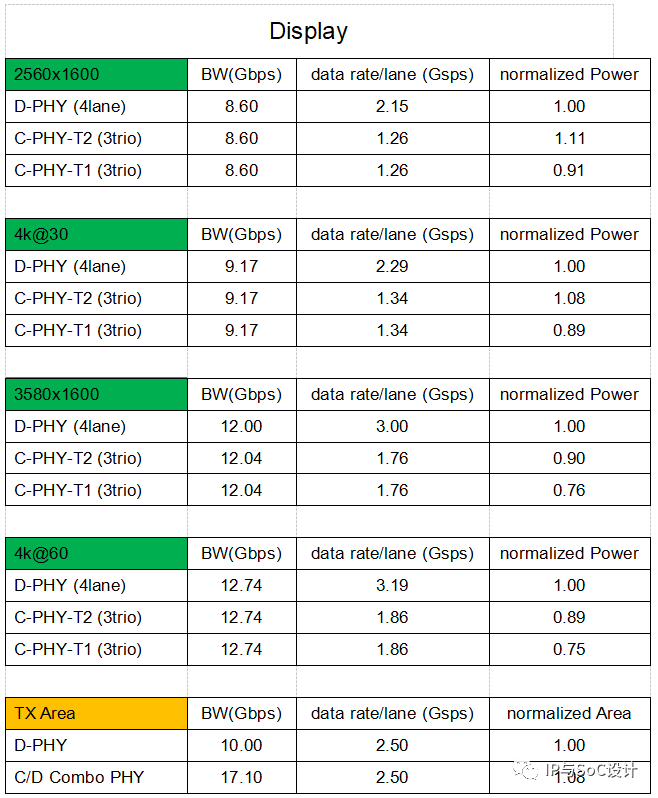

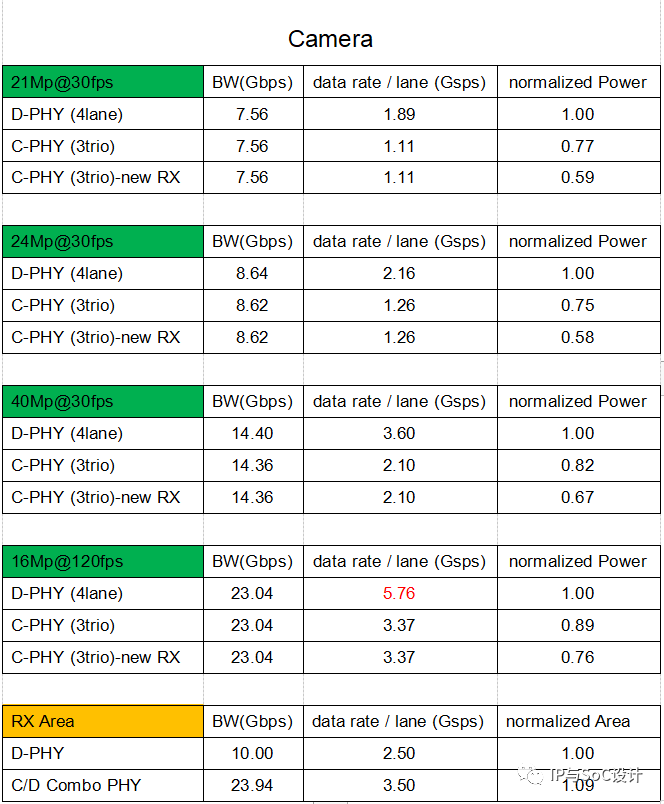

现在,让我们来看看当前显示器和照相机应用中不同使用情况的功率、性能和面积。这些都显示在表3中。

在相同的数据速率下,比较D-PHY和C-PHY/D-PHY组合时,面积增加很小。仅C-PHY模块的归一化功率,当在相同的Gbps下比较时是相当的。在相同的转换率下,C-PHY比D-PHY有明显的优势,可以实现更高的数据速率。

然而,功率增量组合PHY可以通过在C-PHY模式配置中启用多种设计选项来取消(此处未显示)。

Table 3: PPA of different use-cases for Display applications

Table 4: PPA of different use-cases for Camera applications

注意事项:

1.Combo PHY面积增量< 10%

2.Combo PHY 可以覆盖广泛的分辨率:80Mpbs – 10Gbps – 17.1Gbps – 18Gbps – 23.94Gbps

3.MIPI C-PHY 模式:由于频率低/偏置较小/通道数较少,功耗比 DPHY 模式低约 10-30%

4.由高通公司提供

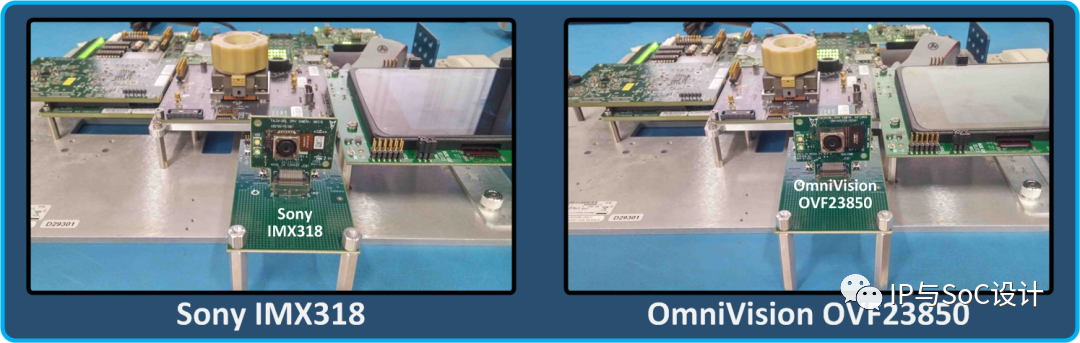

C-PHY/D-PHY组合已经在多个使用案例、许多不同的供应商和许多不同类型的产品中得到广泛采用,包括相机(索尼、OVT和其他)、显示器(与大多数主要DDIC公司完成互操作性测试)。该生态系统得到了广泛参与的支持,包括IP(Mixel)、AP/SOC(Snapdragon等)、测试仪(Keysight、Tektronix、Introspect、The Moving Pixel Company)和共模滤波器(Murata、Panasonic、TDK)。

然而,C-PHY的更高的性能并不是免费的;C-PHY带来了一些挑战,包括需要针对不同数据速率范围进行编程的独特 CDR、引入编码抖动的多级信号传输以及使 PCB 设计复杂化的独特的基于 trio 的信号传输。

总之,MIPI C-PHY是一个更复杂、更强大、更高效的PHY,而C-PHY/D-PHY组合在各方面更是如此。Mixel 创建并经过硅验证的双模 MIPI D-PHY/MIPI C-PHY,实现了两个 PHY 之间的平滑过渡。Mixel的双模MIPI D-PHY/MIPI C-PHY共享所有的通用模块,从而减少了面积,并降低了功率/Gbps。它具有MIPI C-PHY PPA改进的优点,同时保持与MIPI D-PHY的兼容性,并使用相同的串行接口引脚。此外,MIPI C-PHY/MIPI D-PHY组合已经在多个节点和代工厂进行了硅验证,并且已经被许多一级SOC、传感器和显示器供应商集成到几个终端产品中。自其首次亮相以来,我们看到MIPI C-PHY/MIPI D-PHY组合在各种应用中对摄像头和显示器的吸引力不断增强,包括移动和移动邻近应用,如VR/AR/MR、汽车、物联网等。

编辑:黄飞

-

jf_12682852

03-01

0 回复 举报原文链接:https://www.design-reuse.com/articles/43954/demystifying-mipi-c-phy-dphy-subsystem.html 收起回复

jf_12682852

03-01

0 回复 举报原文链接:https://www.design-reuse.com/articles/43954/demystifying-mipi-c-phy-dphy-subsystem.html 收起回复

-

Arasan推出超低功耗D-PHY IP2021-12-13 744

-

MIPI M-PHY 4.1 – 防止高速移动设备中的数据丢失2023-05-26 1645

-

U7249C和U7249D MIPI M-PHY,Infiniium示波器一致性测试软件技术资料2018-10-25 0

-

MIPI C-PHY的静噪的特点和MIPI C-PHY用的静噪对策元件2020-12-21 0

-

D-PHY接口、C-PHY接口和M-PHY接口的基本概念2021-07-29 0

-

泰克公司演示采用Synopsys硅验证HS-Gear3 M-PHY IP的M-PHY测试解决方案2013-03-29 1416

-

是德科技新款 MIPI® D-PHYSM 和 C-PHYSM 测试解决方案 加速移动技术和物联网技术开发2017-05-04 1554

-

MIPI C-PHY差分传输接口的静噪特点及相应对策2020-02-04 8383

-

基于3-Phase symbol编码技术的C-PHY详解2021-01-01 8059

-

一文详解MIPI物理层规范中的M-PHY2020-12-18 15332

-

MIPI C-Phy PCB空间优化设计2022-07-14 3916

-

采用TekScope PC进行MIPI D-PHY/ C-PHY解码的使用方法和步骤2023-07-13 2103

-

MIPI-D/C PHY的PCB布局布线要求2023-08-22 1450

-

支持智能手机高像素拍摄的MIPI C-PHY抗扰静噪对策2023-11-29 640

-

聚焦MIPI 系列之四:一文盘点D-PHY/C-PHY/M-PHY之架构与测试解决方案2024-08-02 859

全部0条评论

快来发表一下你的评论吧 !