非隔离IC控制器与主功率回路系统的PCB设计思路

PCB设计

描述

我们电子产品往往60%以上-可靠性方面的问题都出现在电子线路板的PCB设计上;工作及性能良好的PCB需要相关的理论及实践经验;我在产品的设计实践中经常碰到各种各样的问题;比如电子线路板不能通过系统EMS的测试标准,测试关键器件IC的功能引脚时出现高频噪声的问题,威廉希尔官方网站 功能IC引脚检测到干扰噪声进行异常保护等等。

通过理论与实践结合;用测试数据检验我们的理论和实践的差异点!优良的设计跟长期的经验总结是密不可分的!

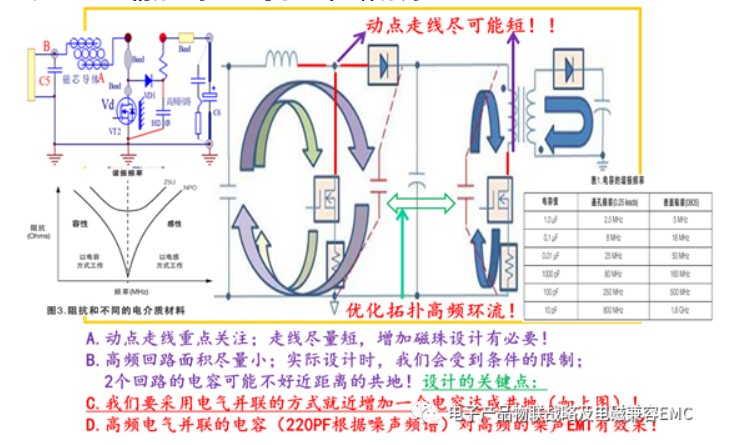

1.开关电源通过以下的原理示意图分享设计总体原则

图示为我们常用的两种开关电源的拓扑结构;

A.开关电源拓扑主电流回流路径面积最小化;驱动脉冲电流回路最小化。

B.对于隔离开关电源拓扑结构,电流回路被变压器隔离成两个或多个回路(原边和副边),电流回路要分开最小回流面积布局布线设计。

C.如果电流回路有多个接地点,那么接地点要与中心接地点重合。

D.实际设计时,我们会受到条件的限制;如果2个回路的电容可能不好近距离的共地!

设计的关键点:

我们就要采用电气并联的方式就近增加一个高频电容达成共地(如图红色虚线)!

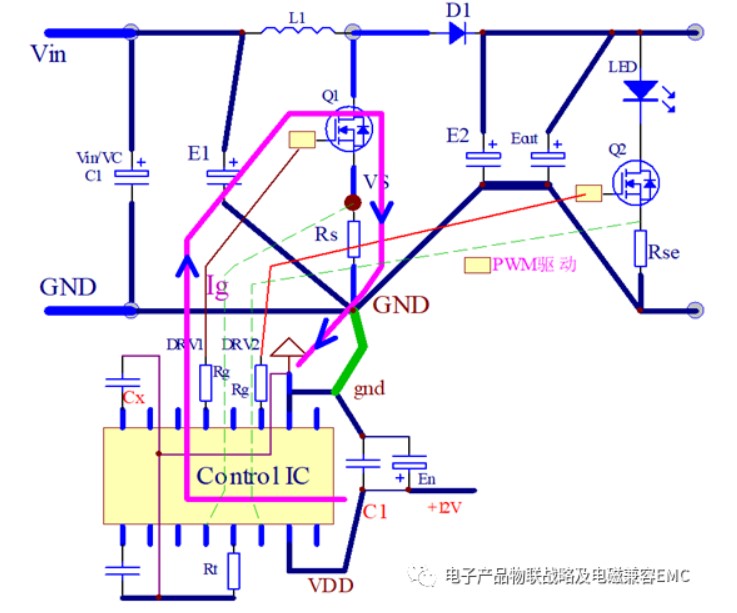

2.对于非隔离的IC控制器与主功率回路系统的PCB设计思路

如下图为-非隔离的电源给IC控制器供电,IC控制器控制LED的负载并进行调光及其它功能的控制应用。其控制器的供电及驱动回路的设计会影响系统的功能及可靠性。

通过图示IC控制器-PCB布局布线的设计思路如下:

A1.IC周边器件的地走线优先布局布线后连接到IC-gnd;

A2.IC-gnd再连接到滤波电容C1(高频电容-低容值)的接地端,如果是非隔离系统;存在主电源系统进行动态工作时,此地不再进行12V非隔离电源地连接。

A3.IC-控制中心的gnd要单点接地!C1电容靠近IC-gnd引脚,引脚地与C1电容-gnd最短连接。

关键环路

B.主电源回路路径的最小化设计原则

C.拓扑电流回路路径最小化设计原则

D.脉冲驱动回路路径最小化设计原则

注意条件受限时:电源的主回路与拓扑回路的电容可能不共地,我们可以采用电气并联的方式就近增加一个高频电容达成共地!

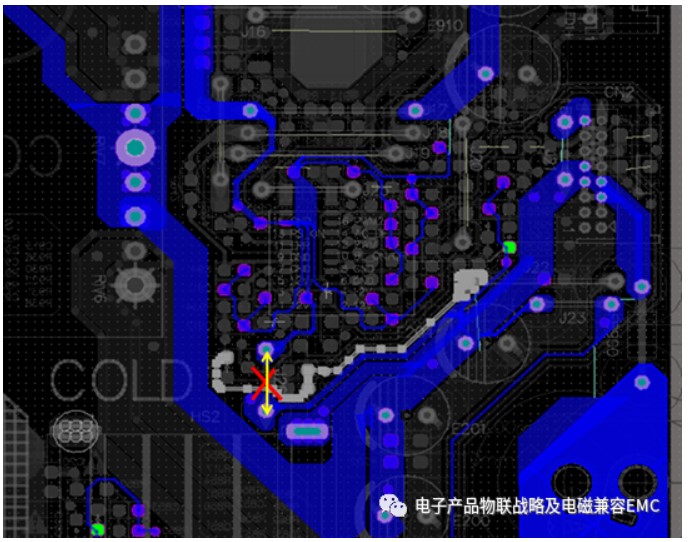

3.具体BOOST的LED驱动架构的PCB布局布线进行具体分析

设计基本思路如上所述;用下图进行设计分析

在图示中:黄色跳线(JX)有与12V回路地进行最小化环路面积的理论设计。

PCB蓝色高亮部分为系统GND走线,白色高亮部分为12V-IC供电电源正端走线。

通过实际的数据测试验证黄色跳线(JX)连接线接地对系统的影响:

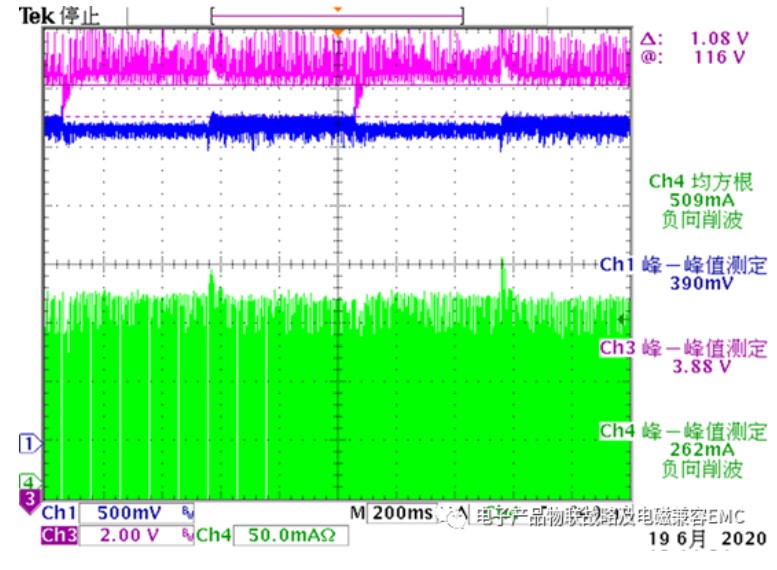

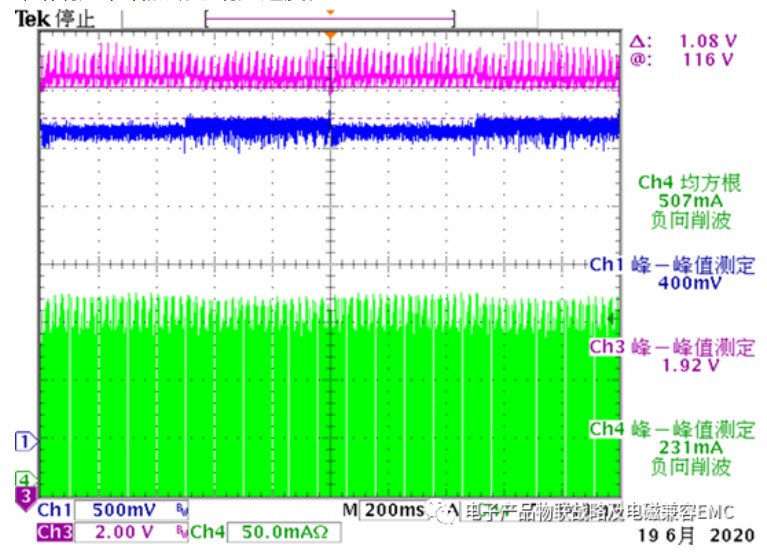

测试条件:12V-6A 115V/600mA (灯条)

测试项目:12V负载动态负载时间间隔500ms max load/minimum load6.6A/0.2A

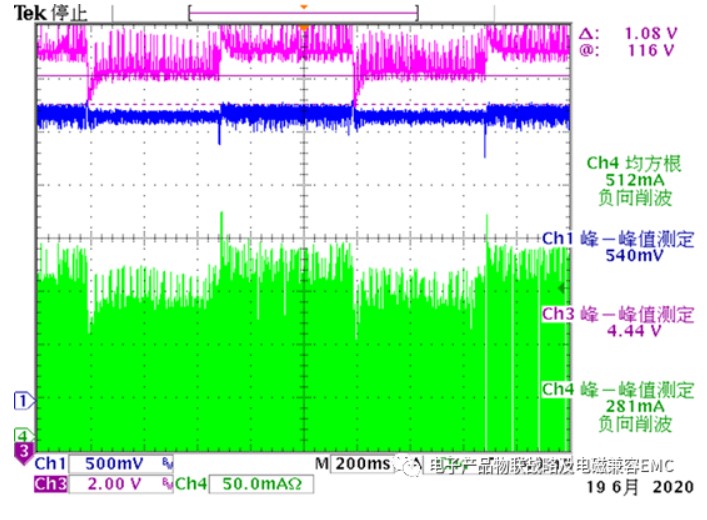

示波器设置

CH1:12V(偏置10V) CH3:115V(偏置100V) CH4:ILED(偏置500mA)

黄色跳线(JX)在回路中:

黄色跳线(JX)去除

通过优化环路响应,增加动态响应速度。

黄色跳线(JX)的系统回路影响:

由于12V同时给控制IC提供VDD,在进行差分信号走线时12V与GND布线时即电源与地的回流面积最小;当12V拉负载时,12V电解电容正到地回流;当12V负载电流增加时地走线阻抗不等于0,这时在公共地阻抗上就会产生电压差,导致地基准位的变化。

去掉黄色跳线(JX)后,控制回路变成单点接地。此时地电位基准的影响就不受多个回路电流的影响。在非隔离的系统中单点接地符合设计理论。

设计经验总结:

可能存在多种原因,IC供电电源有多种应用功能连接。

A.对于隔离的控制器IC威廉希尔官方网站 提供VDD,在进行差分信号走线时12V与GND布线时即电源与地的回流面积最小;

B.对于非隔离IC控制的GND要避免形成环路;IC同侧引脚的相同功能引脚的GND走线要连接在一起到IC-GND;IC-控制中心的gnd要求单点接地。

审核编辑:刘清

- 相关推荐

- 控制器

- PCB设计

- IC威廉希尔官方网站

- GND

-

SM7307非隔离T8 LED灯管电源IC方案2015-10-14 0

-

电源 电源管理 IC 反馈回路功率控制器 UC39012018-07-14 0

-

非隔离式开关电源的PCB布局详细攻略2018-10-15 0

-

理论与实践结合,开关电源应该这样进行PCB布局!2020-07-18 0

-

开关电源PCB设计如何做到最优?这些细节不容忽视……2020-08-27 0

-

干货!非隔离IC控制器系统的PCB设计分析汇总2020-09-23 0

-

开关电源与IC控制器PCB设计思路2020-12-24 0

-

具体BOOST的LED驱动架构的PCB如何布局布线?2021-03-11 0

-

电机控制系统的功率驱动主回路与控制回路之间为什么要采用浮地连接方式呢?2023-03-22 0

-

非接触式IC卡节水控制器的设计与实现2009-11-23 2073

-

如何设计非隔离IC控制器系统的PCB2020-11-25 412

-

非隔离IC控制器系统的PCB设计的分析2020-12-24 418

-

开关电源与IC控制器PCB设计思路资料下载2021-04-05 926

全部0条评论

快来发表一下你的评论吧 !