蔡司PROVE - 光掩膜量测解决方案

描述

继介绍了在光掩膜验证工艺中扮演重要角色的AIMS机台(点击回顾),以及光掩膜缺陷修复的主角PRT和MeRiT机台(点击回顾)后,本期我们迎来了蔡司光掩膜解决方案中针对量测和对准工艺的王牌:PROVE和ForTune。

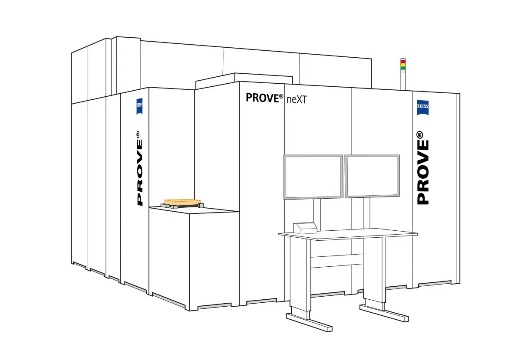

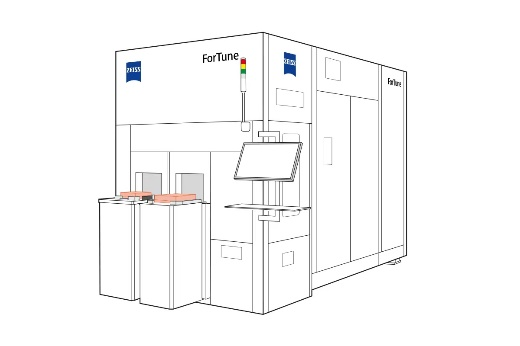

▲ 左:光掩膜量测解决方案PROVE, 右:光掩膜微调解决方案ForTune机台外观

在光掩膜技术指标中一个很重要的参数是放置误差(registration),它是指图形在光掩膜上实际位置相对于设计的对准偏差。显然,光掩膜的放置误差直接影响到晶圆上的套刻误差(overlay)。缩小光掩膜放置误差的工作主要集中在两个方面:一是必须能精确测量光掩膜之间的放置误差;二是根据测量的放置误差对曝光工艺做修正,使得修正后的放置误差大大减小[1]。蔡司提供的PROVE和ForTune解决方案即是针对这两个重要的工作流。

蔡司PROVE - 光掩膜量测解决方案

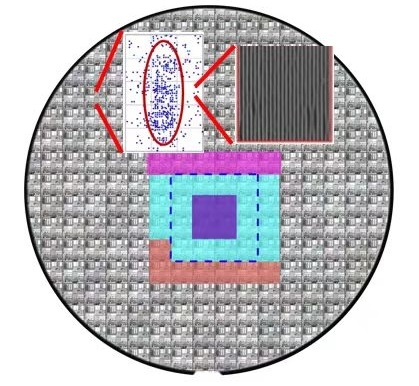

和晶圆制造工艺类似,图形放置位置是光掩膜量测中相当重要的一部份。完整的芯片设计不仅对每一层光掩膜的特征图形位置有严格的精准度要求,并且为了得到能正常运行的电子组件,一整套产品内不同层光掩膜的套刻有非常严格的技术需求。而随着多重图形曝光的导入,一些复杂图层将根据关键尺寸考量被拆分成不同的层,不同层之间要互相叠对。为了完成这些高精度任务,量测系统需要在图形放置位置量测中具备极高的分辨率及可靠的再现性和准确性。

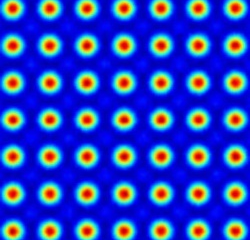

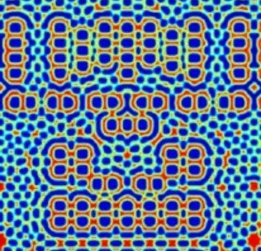

下图是一个典型案例,在曝光过程中,由于光掩膜上相邻图形之间存在干涉和衍射效应,投影到晶圆上的图形和光掩膜上的图形不完全相同。随着工艺制程的不断演进,光掩膜上图形尺寸不断缩小,这种相邻图形之间的干涉和衍射效应更加明显,曝光后图形的偏差更大。

▲ 两层版图叠对后形成的复杂图案(点击查看大图)

同时随着制程的提升,对于光掩膜上线宽的均匀性CD uniformity(CDU),图形在光掩膜上放置的误差(Registration),以及光掩膜间套刻标识的对准偏差Mask-to-Mask Overlay等的要求也不断提高(先进制程,大约数个纳米)。随之而来的是工艺成本的攀升,以及对机台性能要求的提高。蔡司 PROVE设备的关键部件是波长在193nm的高分辨率光学成像器件(仅受限于衍射极限),这与当前和未来大多数主流光掩膜应用的波长相对应,其量测的重复性和准确性可优于亚纳米。

蔡司ForTune - 光掩膜微调解决方案

晶圆代工厂对产线可预见性及可靠性有极高的依赖度。在其客户眼中高良率是晶圆代工厂能力的重要指标,任何导致良率下降的工艺偏差都将严重损害其客户对晶圆代工厂能力的信任。在此基础上,蔡司提供了一种创新解决方案,能够有效防止突发偏差,降低晶圆瑕疵,提高晶圆产品套刻精度和线宽均一性。

在市场其他可用解决方案的基础上,通过对光掩膜进行高分辨率和高自由度的调整,蔡司ForTune 能提高晶圆场内(intra-field)光刻参数。它适用于所有包括内存DRAM, 3D NAND, XPOINT及Logic在内的各级市场,并涵盖以下两个主要领域:

01

RegC应用方案:

改善晶圆套刻精度

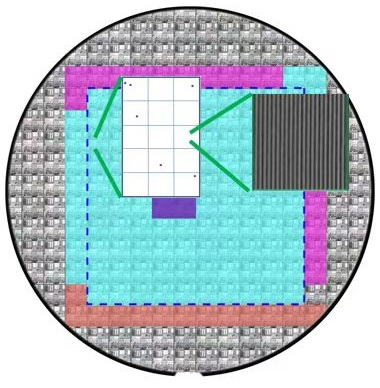

通过修正光掩膜本身的放置误差,蔡司ForTune 设备的RegC应用能增进产品刻套精度(OPO, on product overlay)。除此之外,根据光刻机的透镜特征(Lens fingerprint)或者晶圆场内刻套误差残值(Overlay residual),RegC应用亦可通过对光掩膜的调整来改善OPO。

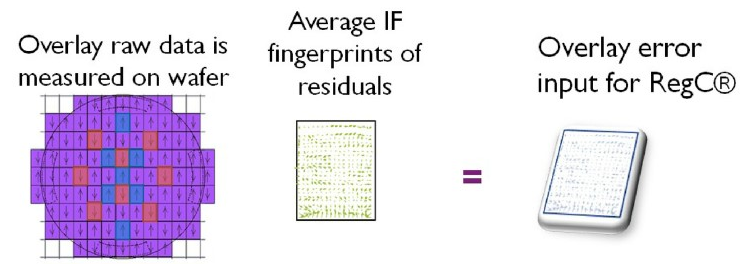

有文献报道,使用PROVE和ForTune组合的这种测量和修正系统可以使光掩膜之间的放置误差减小40%-70%[2]。下方为这套测量和修正系统的工作流程图,最早由蔡司提出[3]。

▲ RegC的工作流程图[3] (IF: intra-field)

首先用光掩膜在晶圆上曝光,测量曝光图形的套刻误差,使用光刻机修正模型分析测量数据,确定曝光区域内套刻(intra-field, IF)误差修正后的残值。把修正后的残值输入到RegC系统中,RegC控制激光在光掩膜的指定区域内植入微应变单元使得光掩膜在该区域内产生微小的方向可控的形变,从而改变该区域内图形的位置,以改善图形的放置精度,并最终提升晶圆的套刻精度。简单而言,RegC可以修正光刻机对准系统无法修正的一部分曝光区域内部的套刻误差[4]。

02

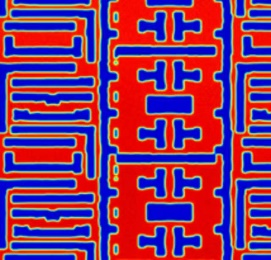

CDC (CD correction) 应用方案:

提升晶圆线宽均一性

ForTune 设备的CDC应用则能通过改变光掩膜指定区域的光通量来调整该区域的到达晶圆表面的实际曝光能量,从而改善整个晶圆场内的CDU,使得晶圆场内CDU导致的工艺缺陷有效减少,进而提高良率。

▲ 通过CDC调整后CDU的改善情况

通过CDC的调整,晶圆CDU显著提升,进而提升工艺窗口和降低缺陷。

审核编辑 :李倩

全部0条评论

快来发表一下你的评论吧 !