基于I2C总线的CMOS图像传感器接口威廉希尔官方网站 设计

电子说

描述

1引言

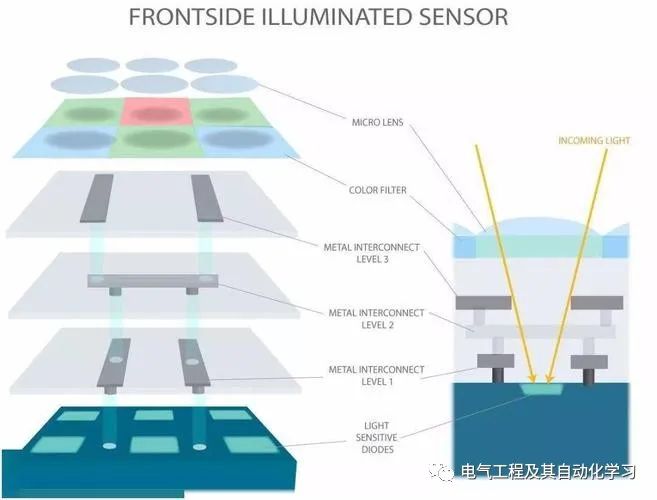

数码相机等图像消费类电子产品产业正在飞速发展,这使得图像传感器和数码相机专用集成芯片的研制获得巨大的市场支持。目前广泛使用的数码相机图像传感器主要是以下两种:CCD和CMOS。CCD图像传感器具有技术成熟、图像噪声小等优点,但由于制作工艺复杂,与标准工艺不兼容,且需要高电压供电,芯片功耗大,目前仅在型数码相机市场上占有一席之地。而CMOS图像传感器采用了CMOS工艺,可以将图像采集单元和信号处理单元集成到同一块芯片上,因而具有集成度高、功耗低、价格便宜的优点,具有很好的发展前景。随着噪声消除技术的改进,目前CMOS图像传感器正由中、低档数码相机向型数码相机发展。

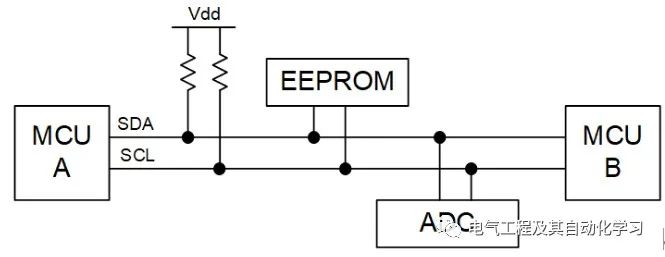

现在的CMOS图像传感器芯片大都把I2C总线的一个子集作为控制接口(如Motorola公司的MCM20027,Omnivision公司的OV9620等),因而用户可以很方便地对芯片进行编程操作。与其他串行总线相比,I2C总线以两根连线实现了全双工同步数据传送,可以极方便地构成多机系统,并进行扩展,适用于消费电子、通信电子、工业电子等领域的低速器件。I2C总线由双向数据线SDA和时钟线SCL组成川,用户使用集电极开路门以“线与”方式进行总线连接。图1为I2C总线的通信协议示意图,包括开始信号、结束信号、应答信号和数据有效等状态。当SCL持续为高电平时,SDA由‘1'跳变到‘0',表示开始信号;当SCL持续为高电平时,SDA由‘0'跳变到‘l',表示结束信号:在数据传输过程中,SDA在时钟高电平时有效,低电平时更换数据。开始和结束信号均由主I2C产生,通过SDA传输的数据以字节(8—bit为单位,高位在前,低位在后,在每个字节后面由接收端发送一个低电平的应答信号。

本文设计了一种基于I2C控制总线的CMOS图像传感器接口威廉希尔官方网站

,能够有效控制CMOS图像传感器的指令,产生数码相机专用集成威廉希尔官方网站

其他模块的同步时序,在MCU的控制下完成取景和拍照操作,并支持多种规格的CMOS图像传感器和液晶显示器。

2顶层设计

根据所设计的数码相机专用集成威廉希尔官方网站 芯片的系统要求[2],CMOS图像传感器接口用来控制达400万像素多种规格的CMOS图像传感器,并且在MCU的控制下,能控制传感器芯片的自动/手动曝光和自动/手动白平衡及其他芯片支持的功能。该接口威廉希尔官方网站 能够在取景和拍照两种模式下工作,在取景模式下,实现可编程的降采样处理,能够输出以4的倍数为基准的任意分辨率的图像,并接受多种规格的液晶显示器,取景速度达到30帧/s。

根据上述功能要求将CMOS图像传感器接口划分为三个模块:主I2C总线接口模块、寄存器文件接口和可编程降采样模块,其总体框图和输入输出端口线如图2所示。端口线主要有:①和MCU接口的连接,包括MCU_AB(地址总线),MCU_DB(数据总线),MCU_nWR(写使能),MCU_nRD(读位能),MCU—nCS(MCU操作选中信号)和MCU nINT(中断信号)②和CMOS图像传感器的连接,包括来自CMOS图像传感器的帧同步(VC L K)、行同步(H C L K)、像素同步(PCLK)、数据ADC(10位CMOS输出的数值),以及I2C总线的SDA,SCL,SCCB_E等:③和数码相机专用集成威廉希尔官方网站 芯片的其他子模块相连,如VSYNC(帧同步)、HSYNC(行同步)、PSYNC(像素同步)、ADCOUT(输出图像数据)。

3模块设计

3.1寄存器文件模块

寄存器文件模块包括一个中断状态机和MCU接口。中断状态机用以控制主I2C总线模块,降采样处理模块和MCU接口的协调工作,它主要包括5个状态:INT_DECIDE,INT_I2C_READ,INT_MCU_READ,INT_I2C_WRITE和INT_CLEAR。状态机缺省状态为INT_DECIDE判决状态,表示状态机处于等待状态:INT_I2C_READ表示I2C,总线正在从CMOS传感器读数据:INT_12C_WRITE表示I2C总线正在从CMOS传感器写数据:INT_MCU_READ表示MCU正从I2C上读数据:INT_CLEAR表示清中断。

MCU接口通过给内部寄存器读写参数,使CMOS图像传感器接口威廉希尔官方网站

能够实现取景、拍照和软复位的功能:并通过I2C总线给CMOS传感器的内部参数寄存器读写参数,实现对CMOS传感器进行各种参数设置,以充分发挥CMOS传感器的性能。其中内部寄存器包括控制寄存器和降采样寄存器,降采样寄存器主要给降采样处理模块提供可编程所需要的参数。控制寄存器为低4位有效,第0位为软复位位,当系统复位或系统设置该位为l时,整个接口置于复位状态;当系统设置该位为0时,则取消复位状态变为工作状态。第1和第2位一起用来控制拍照和取景操作,当两位均为1时表示拍照状态:当第1位为1,第2位为0时表示取景状态;第3位用来表示中断位。

3.2主I2C总线接口

由于CMOS图像传感器目前普遍采用的是I2C总线功能集中的一个子集,因此该接口比一个完整的主I2C总线要更简单。它的读写周期如下:当要进行I2C总线写操作时,先发送所使用的CMOS传感器特定ID写地址,紧接着发送需要写的寄存器的地址(sub_address),再发送数据(data);当进行I2C总线读操作时,先发送所使用的CMOS传感器特定ID写地址,紧接着发送需要写的寄存器的地址(sub_address),再发送CMOS传感器特定ID读地址,接收数据(data)。对于不同的CMOS传感器产品,它们的ID地址是不同的,例如Omnivision公司为60h(写)[3]、61h(读)Motorola公司为66h(写)[4]、67h(读)。

考虑该主I2C总线的读写周期的特殊性,将该I2C总线设计成如图3所示的总体结构。主要包括控制状态机、数据缓存器、SDA产生接收器、SCL产生器以及并-串转换和串-并转换。数据缓存器用来将要通过I2C总线传输的数据组合成所需要的格式,由于CMOS图像传感器的I2C总线特殊的读写操作格式,因此可以将需要传输的ID地址、sub address和data组合在一个30位的缓存器中,它的低六位用来表示高24位的3个字节的属性,以便正确的传输,通过这种数据组合,便于I2C总线传输和识别。串-并转换和并-串转换本质上是两个移位寄存器,用来将接收到的串行数据转变成并行数据或并行数据转变成要发送的串行数据。SDA产生接收器用宋生成主总线的控制命令如开始、结束和应答位等(和SCL配合工作),随后接收和读取数据。SCL产生器用来产生I2C总线的时钟信号和控制命令信号(和SDA配合工作)。控制状态机主要负责控制整个I2C总线的流程,其状态图如图4所示。主要包括以下八个状态:IDLE(等待读取或写入数据)、LOAD(加载需要传输的数据)、START(发送开始信号)、WRRD(I2C总线处于读取或写入数据状态)、DECIDE(判决当前状态是读取数据还是写入数据)、WR_ACK(写应答)、RD_ACK(读应答)、STOP(发送结束信号)。例如给CMOS图像传感器的一个寄存器写一个字节的数据,需要经历以下状态:IDLE→LOAD→START→WRRD→WR_ACK→WRRD→WR_ACK→WRRD→WR_ACK→STOP→IDLE;一个字节的写操作的ActiveHDL的仿真时序如图5所示。

3.3可编程降采样模块

可编程降采样模块是通过MCU给内部的降采样寄存器写入需要的降采样参数来实现可编程的,接口内一共有6个降采样参数寄存器:总行数寄存器(hrefprecnt)、总列数寄存器(pixprecnt)、行丢寄存器(hrefdropcnt)、列丢寄存器(pixdropcnt)、行降采样寄存器(vdscnt)、列降采样寄存器(hdscnt),各个寄存器参数所表示的意义如图6所示。操作过程如下:先跳过列丢寄存器值和行丢寄存器值数目的列和行,接下来保留总列数寄存器值和总行数寄存器值数目的列和行,在这些保留的行和列当中用列降采样寄存器和行降采样寄存器的值进行降采样:行降采样寄存器和列降采样寄存器分为两部分:保留和丢弃,保留和丢弃的像素和行的数目均为偶数且为连续的像素,从而保证降采样后输出的像素满足RGRG…RG或GBGB…GB的Bayer格式。通过这样几个降采样寄存器可以很方便实现的各种分辨率的降采样,能够输出任意4的倍数的分辨率的图像,因而可以很方便的支持多种规格的LCD显示器。

4威廉希尔官方网站 的FPGA验证

在经过上述顶层设计和各个子模块的设计后,用Verilog语言[5]来实现,并用ActiveHDL来进行RTL级仿真,并对威廉希尔官方网站 进行了FPGA验证,使用的芯片是Xilinx公司的SPARTANIIXC2S200PQ208,系统时钟为54MHz,FPGA综合的结果显示需要FPGA芯片的11%的SLICEs,22%的IOBs和25%的GCLKIOBs。整个测试流程由MCU控制,在拍照模式下,CMOS图像传感器的数据流经CMOS接口采样存储在SDRAM中,再由EPP接口上传至PC上:在取景模式下,则有LCD显示器实时显示。该接口威廉希尔官方网站 在各种工作模式下功能验证正确。

FPGA验证通过后,作为数码相机专用集成威廉希尔官方网站 芯片的一部分采用上华0.6μm工艺库进行了ASIC的后端自动综合,包括用Design Compiler(Synopsys公司)进行逻辑综合、Prime Time(Synopsys公司)做版图前验证、Silicon Ensemble(Cadence公司)做自动布局布线、Virtuoso(Cadence公司)做DRC和LVS,得到的版图面积约为3.7mm×3.7mm,综合频率为25MHz,在5V供电下,功耗约为150mW。

5结论

CMOS图像传感器接口威廉希尔官方网站 的设计模块可以分为寄存器文件、主12C总线接口和可编程降采样模块3部分,经过威廉希尔官方网站 的顶层设计和各个子模块的功能设计,进行了Verilog语言代码实现,用ActiveHDL进行了RTL级仿真,并进行了FPGA验证,功能设汁正确,并打算作为数码相机专用集成威廉希尔官方网站 芯片的一部分到工艺厂流片。

审核编辑 黄昊宇

-

基于I2C总线图像传感器配置的FPGA实现2018-11-12 0

-

基于I2C总线的CMOS图像传感器接口威廉希尔官方网站 设计2018-11-30 0

-

基于I2C控制总线的CMOS图像传感器接口威廉希尔官方网站2019-04-11 0

-

I2C总线CMOS型PB-0300数字图像传感器2008-08-13 901

-

I2C总线CMOS型PB-0300 数字图像传感器2009-04-16 549

-

I2C 总线CMOS 型PB-0300 数字图像传感器2009-05-15 474

-

PCA9564 并行总线转I2C总线接口芯片简介2010-03-10 1370

-

基于CP2120的SPI与I2C总线接口转换威廉希尔官方网站 设计2010-04-12 840

-

基于I2C总线控制的音频处理威廉希尔官方网站 设计2009-11-16 2486

-

基于CPLD的I2C总线接口设计2011-02-12 1087

-

基于USB2I2C接口的CMOS图像传感器在线调试系统2015-12-21 773

-

CMOS图像传感器威廉希尔官方网站 设计2016-01-18 8219

-

压力传感器与I2C接口的重要性2019-10-16 2064

-

i2c总线用来做什么_i2c总线数据传输过程2020-11-24 7277

全部0条评论

快来发表一下你的评论吧 !