为什么setup检查下一个沿而hold检查当前沿

描述

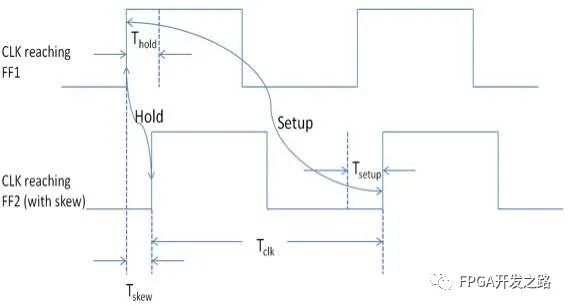

做数字威廉希尔官方网站 设计的可能都见过图一所示的setup和hold时间检查,从图中可以明显看出,setup time检查下一个沿,而hold time检查同一个沿。那么这是为什么呢 ?

图1

数字威廉希尔官方网站 的工作原理

以数字威廉希尔官方网站 设计常见的状态机为例,下一个状态的值总是由当前状态加一些判断条件决定。为了保证下一个状态值的正确,新的状态值要在下一个时钟沿被正确采样,同时不能被当前时钟沿采样。

因此,setup time 的检查是为了保证数据在下一个时钟沿被正确采样,而 hold time 的检查是保证数据不被当前沿采样或破坏,满足了这两点,数字威廉希尔官方网站 便能正常工作。

Hold Time Violation

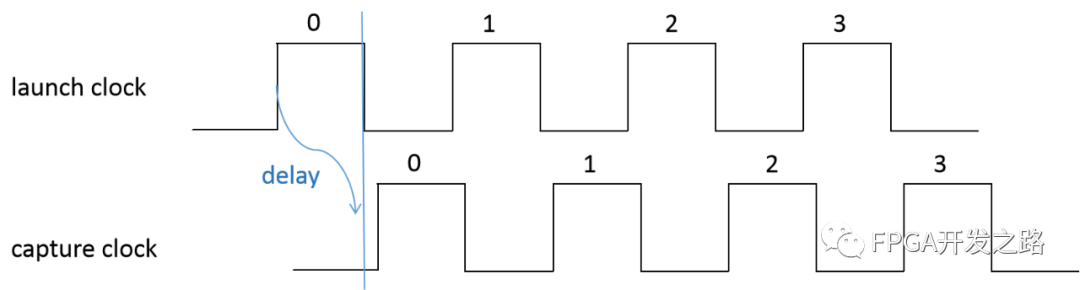

考虑一个两级移位寄存器,其launch clock 和 capture clock如图2所示。可以看到clock skew非常大,大于半个时钟周期。假设数据的延迟小于半个时钟周期,那么 hold time 的检查公式必然不满足, 即 Tcq + Tcomb < Tclk_skew + Thold。

对于这个两级移位寄存器,我们希望的值是 00(cycle0), 01(cycle1), 10(cycle2),00(cycle3)。但是由于第二级寄存器有hold time violation,数据在当前沿就被采样,那么我们实际看到的值为 00(cycle0),11(cycle1),00(cycle2),00(cycle3),完全是错误的结果。

图2

时序违反一定会有亚稳态发生吗

不一定。寄存器进入亚稳态有两个前提条件,一是数据要发生变化,二是数据的变化要发生在setup time和hold time限制的范围内。以上述图2为例,假设数据的变化没有出现在setup和hold time限制的范围内,尽管是有hold time violation,也是没有亚稳态发生的。

- 相关推荐

- 寄存器

- 数字威廉希尔官方网站

- Setup

-

Wi-Fi 6E:Wi-Fi的下一个前沿2023-07-19 377

-

Setup/Hold Time Problem2008-09-11 0

-

解释下setup和hold time2014-04-12 0

-

什么是Setup和Hold时间2021-12-21 0

-

FPC检查,FPC检查是什么意思2010-03-17 8566

-

建立时间和保持时间(setup time 和 hold time)2017-02-08 6052

-

技术研发是华为基石 华为下一个研究前沿是AI2019-09-20 2901

-

如何为下一个符号消除PCB设计项目2019-10-23 2488

-

特斯拉披露:下一个超级工厂可能在美国而不在印度2020-10-28 1634

-

启用负时序检查的步骤2022-10-19 6686

-

通过解剖一个边沿触发器简要说明setup和hold产生原因2023-07-04 1690

-

什么是Setup和Hold时间?2023-11-17 2130

全部0条评论

快来发表一下你的评论吧 !