基于FPGA的低功耗设计方案

可编程逻辑

描述

精确的热分析在很多电子产品设计中都有着举足轻重的作用,在高端的PCB设计中尤为突出。热分析的结果常常会影响PCB的机械层设计和产品的外壳设计:是否需要安装散热片、散热风扇等。如果安装散热风扇,往往需要降低其噪音,这将使得机械层设计变得更加复杂。

热分析的最终目标是要使得整个系统能够稳定地运行,特别是保证芯片的结温不能超过安全阈值。如果无法保证这一点,那么FPGA芯片在性能指标、可靠性、使用寿命等方面将会大打折扣,比如系统不断的重启,FPGA的时序无法满足要求,甚至无法保证其功能的正确运行。热分析必须考虑到FPGA运行的各种实际环境:从恒温实验室的理想环境到外太空极寒/极热的恶劣环境。在后续介绍的功耗分析,实际上和热分析有紧密的关系。

整个FPGA设计的总功耗由三部分功耗组成:1. 芯片静态功耗;2. 设计静态功耗;3. 设计动态功耗。

1、芯片静态功耗:FPGA在上电后还未配置时,主要由晶体管的泄漏电流所消耗的功耗

2、设计静态功耗:当FPGA配置完成后,当设计还未启动时,需要维持I/O的静态电流,时钟管理和其它部分威廉希尔官方网站 的静态功耗

3、设计动态功耗:FPGA内设计正常启动后,设计的功耗;这部分功耗的多少主要取决于芯片所用电平,以及FPGA内部逻辑和布线资源的占用。

所以,前两部分的功耗取决于FPGA芯片及硬件设计本身,很难有较大的改善。可以优化是第3部分功耗:设计动态功耗,而且这部分功耗占总功耗的90%左右,因此所以降低设计动态功耗是降低整个系统功耗的关键因素

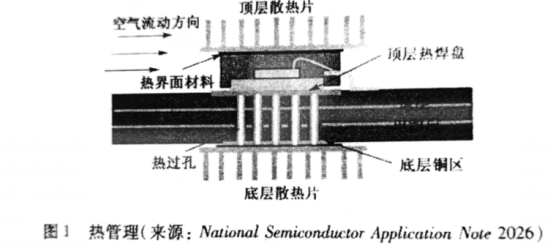

图1显示了对FPGA芯片导热性能产生重要影响的机械元件:顶层和底层的散热片、焊盘和过孔。除此之外,焊盘本身的尺寸和质量,是否使用导热硅脂,空气对流的大小,PCB的尺寸和层数,这些因素都会影响到最终的导热性能指标。

静态功耗分析

以下公式定义了环境温度、芯片恒温、功耗和电阻之间的关系: Tj=(θja·Pd)+Ta Tj代表芯片的结温,反映了半导体器件能够承受的最高温度,每个芯片的器件手册都有该指标。比如Virtex-6芯片的最高Tj为125℃,但是FPGA工具在做静态时序分析和功耗计算时,其默认值通常设定为85℃。不同FPGA芯片的结温指标,包括其工作范围、最大最小值、默认值,在DC and Switching Characteristics数据手册上都会有详细的介绍。 在上述公式中,Ta代表环境温度,PD代表功耗。而Oja是“内核-外环境”之间的热阻,它代表了材料导热的能力,其物理单位是"℃/W”。

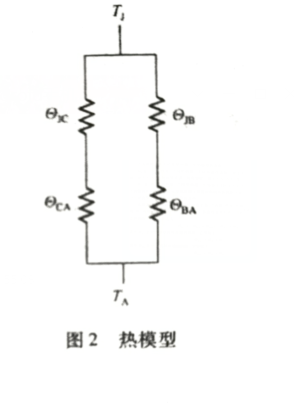

在各种热分析中经常使用图2中的模型和参数。 θjc是“内核-外壳"之间的热阻,不同的器件的值一般也不同。对于Virtex-6的封装来说,其典型值一般小于0.20 ℃/W。 θca是“外壳-外环境”之间的热阻,它等效于FPGA芯片之上的散热片+散热风扇+导热硅脂+其他材料的所有热阻之和,空气对流所带来的影响也要算在其中。 从图2可以看出,整个散热途径有2条:“内核-外壳-外环境"和“内核- PCB -外环境”。由于这2条路径是并行的,因此 总的热阻θja可以表达为 θOja = (θcA x θjba)/(θjca + θjba) 其中Ojca是封装顶层到外环境的热阻,它等效于 θjca = θjc + θca 其中θjba是PCB到外环境的热阻,它等效于 θjba=θjb+θba

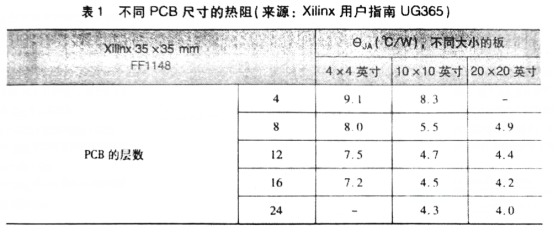

在热分析的建模过程中,还需要将PCB本身的热阻计算在内。对于层数较少的小PCB来说,整个θja值约等于θjca。因为当θjba足够大的时候,该分量对于整个热阻的贡献将变得非常小,甚至可以忽略。PCB越大,层数越多,对应的θjba值也就越大。表1说明了PCB的尺寸和层数对于导热性能的影响。

对于整个热分析而言,最重要就是正确地建立热模型。从表2可以看出,如果没有将PCB的热阻考虑进去,那么最后的结果将变的极不准确。

静态功耗散热方法

空气散热

对于低端、小封装、功托大概在1-6W左右的FPGA芯片而言,一般使用空气对流或者加装散热片的方式即可散热。 散热片的作用在于将芯片表面的热迅速带走,因此通常使用铝或者铜这样的高导热金属作为散热片的材料。散热片通常具有较大的表面积,这样能够更加快速地进行散热。散热片和芯片之间的接触面积对于散热来说非常重要,因此使用导热硅脂将散热片和芯片表面紧紧相连,则能够更进一步地加快热的传导。 在较好的空气对流环境中,功耗在4-10 W左右的芯片,使用散热片将是非常好的选择。

主动散热

对于功耗在8-25W、采用离端大封装的芯片,使用散热片加风扇的组合能够更好地达到散热的效果。 举例 通过给定的结温和环境温度,计算出最大允许的功耗: Tj= +85℃ Ta=+55℃ 器件为Virtex-6芯片,其中热阻Ojc =0. 20℃/W。 散热片和风扇的热阻: Oca=1. 80℃/W, Ojb=0.40℃/W. Oba =2.60℃/W。 通过以下逐个公式的迭代,可以计算出功耗PD: Tj=(OjaxOd)+Ta Oja = (Oca x Ojba)/(Ojca + Ojba) Ojca = Ojc+ Oca=0.2 + 1.8= 2.0℃/W OjBA = Ojb +OBA =0.4 +2.6 = 3. 0℃/W Oja=(2.0x3.0)/(2.0+3.0) = 1.2℃/W Pd=(Tj- Ta)/Oja= (85 -55)/1.2 = 25 w 通过上述正公式可以看出,在给定芯片结温、环境温度及热阻的条件下,整个FPGA芯片的功耗不会超过25 w。

动态功耗的优化设计方法

算法优化

算法优化可分为两个层次说明:实现结构和实现方法 首先肯定需要设计一种最优化的算法实现结构,设计一种最优化的结构,使资源占用达到最少,当然功耗也能降到最低,但是还需要保证性能,是FPGA设计在面积和速度上都能兼顾。比如在选择采用流水线结构还是状态机结构时,流水线结构同一时间所有的状态都在持续工作,而状态机结构只有一个状态是使能的,显而易见流水线结构的功耗更多,但其数据吞吐率和系统性能更优,因此需要合理选其一,使系统能在面积和速度之间得到平衡; 另一个层面是具体的实现方法,设计中所有吸收功耗的信号当中,时钟是罪魁祸首。虽然时钟可能运行在100MHz,但从该时钟派生出的信号却通常运行在主时钟频率的较小分量(通常为12%~15%)。此外,时钟的扇出一般也比较高。这两个因素显示,为了降低功耗,应当认真研究时钟。首先,如果设计的某个部分可以处于非活动状态,则可以考虑禁止时钟树翻转,而不是使用时钟使能。时钟使能将阻止寄存器不必要的翻转,但时钟树仍然会翻转,消耗功率。其次,隔离时钟以使用最少数量的信号区。不使用的时钟树信号区不会翻转,从而减轻该时钟网络的负载。

资源使用效率优化

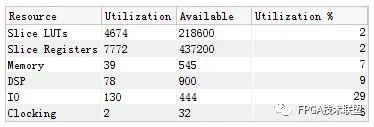

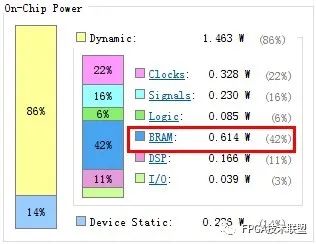

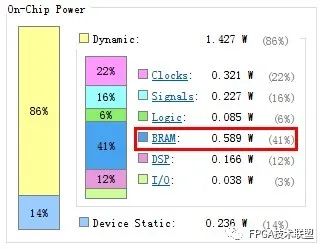

资源使用效率优化是介绍一些在使用FPGA内部的一些资源如BRAM,DSP48E1时,可以优化功耗的方法。FPGA动态功耗主要体现为存储器、内部逻辑、时钟、I/O消耗的功耗。 其中存储器是功耗大户,如xilinx FPGA中的存储器单元Block RAM,因此在这边主要介绍对BRAM的一些功耗优化方法。 如图5中实例,虽然BRAM只使用了7%,但是其功耗0.601W占了总设计的42%,因此优化BRAM的功耗能有效地减小FPGA的动态功耗。

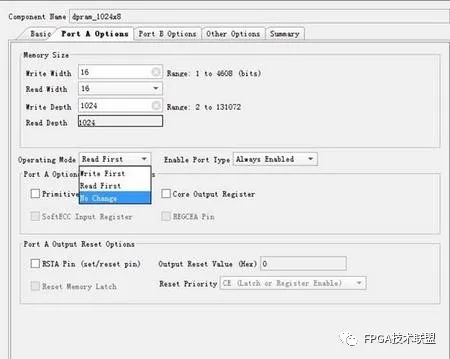

图5 下面介绍一下优化BRAM功耗的方法: a) 使用“NO CHANGE”模式:在BRAM配置成True Dual Port时,需要选择端口的操作模式:“Write First”,“Read First” or “NO CHANGE”,避免读操作和写操作产生冲突,如图6所示;其中“NO CHANGE”表示BRAM不添加额外的逻辑防止读写冲突,因此能减少功耗,但是设计者需要保证程序运行时不会发生读写冲突。

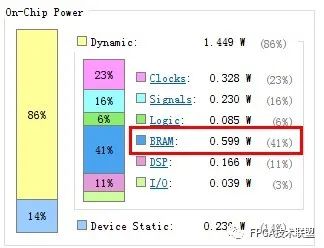

图6 图5中的功耗是设置成“Write First”时的,图7中是设置成“NO CHANGE”后的功耗,BRAM的功耗从0.614W降到了0.599W,因为只使用了7%的BRAM,如果设计中使用了大量的BRAM,效果能更加明显。

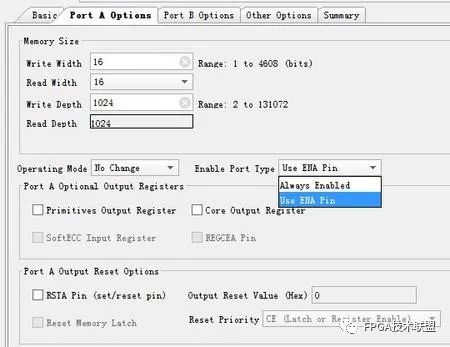

图7 b) 控制“EN”信号:BRAM的端口中有clock enable信号,如图8所示,在端口设置中可以将其使能,模块例化时将其与读/写信号连接在一起,如此优化可以使BRAM在没有读/写操作时停止工作,节省不必要的功耗。

图8 如图9所示为控制“EN”信号优化后的功耗情况,BRAM功耗降到了0.589W

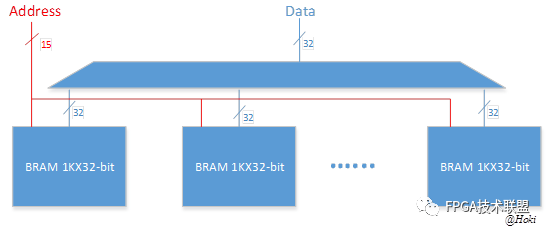

图9 c) 拼深度:当设计中使用了大量的存储器时,需要多块BRAM拼接而成,如需要深度32K,宽度32-bit,32K32Bit的存储量,但是单块BRAM如何配置是个问题?7 series FPGA中是36Kb 的BRAM,其中一般使用32Kb容量,因此可以配置成32K1-bit或者1K*32-bit,多块BRAM拼接时,前者是“拼宽度”(见图10),后者是“拼深度”(见图11)。两种结构在工作时,“拼宽度”结构所有的BRAM需要同时进行读写操作;而“拼深度”结构只需要其中一块BRAM进行读写,因此在需要低功耗的情况下采用“拼深度”结构, 注:“拼深度”结构需要额外的数据选择逻辑,增加了逻辑层数,为了降低功耗即牺牲了面积又牺牲了性能。

图10

图11

参考文献

[1] Xilinx XPower Estimator (XPE) tool for performing thermal and power analysis http://www.xilinx.com/products/design _resources/power _central

[2] Considerations for heatsink selection, Xilinx White Paper WP258 www.xilinx.com/support/documentation/white _papers/wp258.pdf

[3] Virnex-6 Packaging and Pinout Specifications, Xilinx User Guide UG365 www.xilinx.com/support/documentation/user_guides/ug365.pdf

[4] National Semiconductor Application Note 2026 www.national .com/an/AN/AN-2026.pdf

编辑:黄飞

-

用于定位的低功耗有源RFID标签设计方案2013-11-13 1965

-

数字语音解码器的低功耗设计方案2012-08-20 0

-

【专题】低功耗威廉希尔官方网站 设计__低功耗设计技巧2015-06-29 0

-

低功耗AC/DC转换的倒置降压设计方案2021-03-11 0

-

电源管理芯片的低功耗OMAP系统设计方案2009-03-29 946

-

基于单片机的低功耗甲烷检测系统设计方案2009-11-12 1388

-

具有低功耗意识的FPGA设计方法2009-11-26 863

-

基于Spartan-6的FPGA SP601开发设计方案2010-04-02 2500

-

FPGA架构的功耗及影响功耗的用户选择方案2010-08-27 1791

-

FPGA功率损耗与低功耗设计的实现2017-11-23 1425

-

多模式电源管理IC的低功耗设计方案2020-05-20 3937

-

什么是低功耗,对FPGA低功耗设计的介绍2020-10-28 3011

-

还在了解什么是低功耗?FPGA低功耗设计详解2020-10-26 2915

-

FPGA功耗的详细介绍让你实现FPGA的低功耗设计2021-02-14 6591

-

STM32L476xx超低功耗手臂设计方案2021-03-10 1059

全部0条评论

快来发表一下你的评论吧 !