浅谈MCU中集成新型存储器的选择

控制/MCU

描述

半导体技术持续更新迭代,MCU也要与时俱进。为了更好地迎接未来趋势,有的厂商选择从内核下手,比如,由Arm Cortex-M内核转向RISC-V内核;也有选择集成AI,通过在MCU中加入AI加速器,让MCU更加智能;还有一种就是本文将主要介绍的,集成新型存储器。

MCU作为一款需要集成CPU、SRAM、非易失性存储器,以及专用外设的芯片,最常见的存储器形式主要包括了 eDRAM 、SRAM 易失性存储器、闪存、EEPROM 非易失性存储器,这其中集成式闪存是MCU的重要特征。然而,随着时间的推移,闪存却逐渐开始成为制约MCU提高性能、降低功耗的瓶颈之一。一方面,闪存的制程难以扩展到40nm以下,而MCU却已经开始向28nm迈进,并且这些存储单元难以集成到非常复杂的高k金属栅极技术中;另一方面,车载MCU中集成的闪存的可擦写次数太少,随着每个写入和擦除周期,浮栅 NOR 单元中的隧道氧化物会退化并且泄漏会增加,从而加速闪存老化,使其不适合作为数据存储器。

此外,虽然闪存的出现改变了过去ROM所带来的擦除程序数据困难的问题,但嵌入式闪存仍需要较长的写入时间,部分原因在于需要在写入操作之前必须进行擦除操作,这样就会导致运行速度比闪存高两到三个数量级的主MCU必须等待存储器访问,而这些问题都有可能对MCU性能产生不利影响。

基于上述因素,越来越多的MCU大厂开始选择在MCU中集成新型存储器,比如相变存储器(PCM)、磁RAM(MRAM)和阻变存储器(RRAM)等,当然不同的大厂也有着他们不同的选择…

极致低功耗,英飞凌 pick RRAM

MCU巨头厂商英飞凌选择了RRAM(ReRAM),就在11月25日,英飞凌宣布与代工龙头台积电准备将台积电的RAM非易失性存储器 (NVM) 技术引入英飞凌的下一代 AURIX MCU中。

阻变存储器,全称为电阻式随机存取存储器,Resistive Random Access Memory,简称为ReRAM或RRAM。作为结构最简单的存储技术,RRAM通过改变电介质的电阻来工作,在电介质上施加恰到好处的电压产生允许电流流动的细小导电丝,并能在高阻态和低阻态之间实现可逆转换。

由于RRAM可以将DRAM的读写速度与SSD的非易失性结合于一身,因此其拥有了擦写速度高、耐久性强、单个存储单元能存储多位数据的优势。而它还有一个极为重要的优势,就是功耗低,Rambus Labs高级副总裁Gary Bronner就曾强调,RRAM的功耗比闪存低得多,可能是下一代 MCU 的一个关键差异化因素。

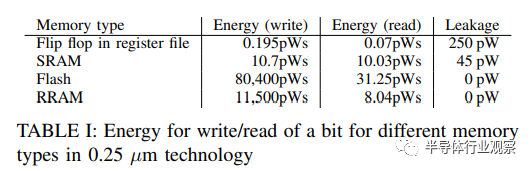

此外,2016年《Application study: RRAM for Low-Power Microcontrollers》论文也曾指出,RRAM的一个可能应用领域就是MCU中所有易失性存储器的备份存储器。论文认为,在RRAM中存储一位值所需的能量小于在闪存技术中存储一位所需的能量。RRAM中的每个存储单元都可以独立于其他单元进行置位或复位,但在闪存中,就必须先擦除整个块,从而增加了数据管理的工作量。此外,与闪存相比,RRAM存储块的设计不太复杂,高压发生器不是必需的,并且具有双栅极的晶体管的复杂结构由晶体管和修改的通孔代替。因此,RRAM存储器似乎是低功耗微控制器的理想备份存储器。

不同存储器类型的位写/读能量消耗

图源:《Application study: RRAM for Low-Power Microcontrollers》

该论文也得出结论称,RRAM作为额外的存储器,允许MCU快速进入非常深度的睡眠模式,从而可以完全关闭电源,将能量泄漏减少到零,并且存储和恢复来自RRAM的数据所需时间和能量也很低,而少于一分钟的睡眠时间甚至可以分别增加电池和传感器节点的寿命。

从目前技术来看,RRAM显然有望“备胎转正”,能做的不仅仅是MCU中的备份存储器。此前有数据显示,采用 65 nm工艺制造的 RRAM 将有助于减小芯片和内存尺寸,同时与闪存相比仅消耗 1/10 的功率,而此次英飞凌和台积电要做的已经是向28nm迈进。据悉,英飞凌和台积电在 RRAM NVM 技术方面合作了近十年,英飞凌官方消息显示,RRAM 技术为性能扩展、功耗降低和成本改善创造了巨大潜力,已经向基于台积电 28nm eFlash 技术的主要客户运送其 AURIX TC4x 系列样品,首批基于 28nm RRAM 技术的样品将于 2023 年底提供给客户。从某种意义上来说,采用28nm工艺制造的RRAM或许会带来从尺寸、功耗,到速度等多方面的惊喜。

据英飞凌透露,AURIX TC3x 已成为许多应用领域的首选汽车微控制器,而基于台积电RRAM 技术的 AURIX TC4x 通过提高 ASIL-D 性能、人工智能功能和最新的网络接口(包括 10Base T1S 以太网和 CAN-XL)进一步扩大了这一成功,AURIX TC4x MCU将性能扩展与虚拟化、安全和网络功能的最新趋势相结合,以支持下一代软件定义的车辆和新的 E/E 架构,为在汽车领域引入 RRAM 奠定了基础。

当然,除了低功耗,成本也是RRAM的优势之一。《The future of RRAM : From Embedded Application to In Memory Computing andB eyond》指出,28nm及以下的闪存会面临需要额外增加9-12层掩膜版,导致成本升高,而RRAM由于采用简单的内存单元结构与材料,因此只需多增加一层掩膜版,就能够整合于现有的制造流程,进而可以实现更低的生产成本。

快速读取和写入,ST认准PCM

在新型存储方面,意法半导体一直是微控制器嵌入式存储器相变存储器 (PCM) 的早期研究者,尤其是汽车应用。PCM全称Phase-change RAM(相变存储器),也可以为PCRAM,原理是通过改变温度,让相变材料在低电阻结晶(导电)状态与高电阻非结晶(非导电)状态间转换。

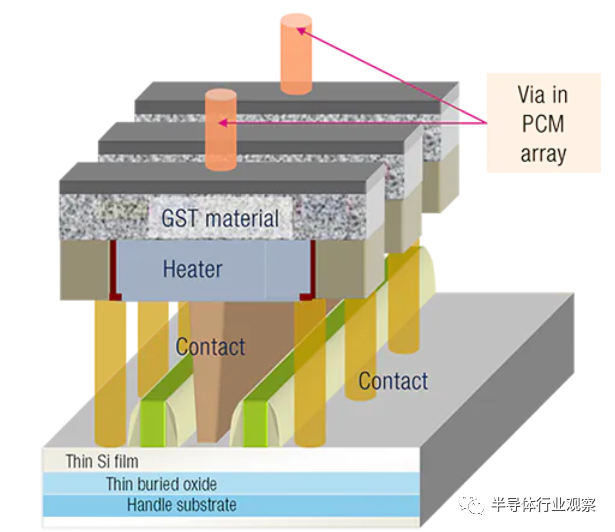

PCM的基本机制是在 1960 年代由Stanford Robert Ovshinsky发明,使用锗锑碲 (GST) 合金制成,并利用非晶态和结晶态之间材料物理特性的快速热控变化,以低电压进行读写,与闪存和其他嵌入式存储器技术相比具有多项显着优势,比如拥有低延时、写入性能/数据保留,寿命长,功耗低,密度高,抗辐照特性好、灵活的后端流程等诸多技术特点。

或许是性能过于优异,PCM率先登上了MCU的舞台,据pc.watch报道,在28纳米世代以后的生产技术中,MCU厂家率先发布的eNVM技术就是ePCM。2018年,意法半导体宣布,内建ePCM的28nm FD-SOI车用MCU技术架构和性能标准,开始提供主要客户搭载ePCM的MCU样片。

集成在 28nm FD-SOI 技术中的嵌入式 PCM 位单元的横截面

图源:意法半导体

消息显示,意法半导体是首家有能力整合这种非易失性存储器与28nmFD-SOI技术,并研发高性能之低功耗汽车MCU的厂商。其实,意法半导体早在2000年就开始研究PCM,并与英特尔合作,2005年意法半导体和英特尔共同开发了90nm的PCM技术,2008年两家公司合并了各自的分立存储器业务,成立了 Numonyx NV 合资企业,随后被美光(爱达荷州博伊西)收购。

曾有一篇文章分析了在eNVM各种技术中,为什么PCM是最适合车载应用,主要原因还是在于PCM的可制造性和成本。比如,在汽车应用中,ePCM 存储元件的集成比 28 nm 嵌入式闪存技术便宜得多;ePCM 提供了快速的读取和写入,缩短了工厂编程时间,降低了制造成本;允许模拟真正的 EEPROM 的单比特可更改性,显着减少系统写入时间;提供可与嵌入式闪存媲美的可靠性和耐用性优势,允许进行更多写入…

目前来看,意法半导体搭载ePCM的MCU就主要应用于汽车领域。在2018年时,意法半导体曾表示,ePCM解决方案可以克服汽车对容量更大的嵌入式存储器的需求,其最高工作温度可达+165℃,能够确保在高温回流焊制程后其韧体/数据可完好保存,并且抗辐射,为数据提供更多的安全保护。到了2021年8月,意法半导体开始向主要车商交货其首批Stellar SR6系列车用MCU,计划于2024年量产。其中,Stellar SR6 P和G两个系列首批MCU配备高达20MB的PCM,确保读写效能优异,数据保存期限长,同时符合AEC-Q100 0级汽车标准。

灵活使用内存,瑞萨选择MRAM

在eNVM各种技术中,日本MCU大厂瑞萨选择了MRAM。MRAM全称Magnetic RAM(磁性存储器),是一种基于隧穿磁阻效应的技术,拥有非易失,读写次数无限,写入速度快、功耗低,和逻辑芯片整合度高等技术特点。

Objective Analysis首席分析师Jim Handy曾认为MRAM比闪存更能持久储存数据,他表示,MRAM和其他新兴非挥发性技术的特点之一在于编程人员能够灵活地使用内存。工程师不再需要将程序代码限制在NOR的大小或限制数据只能在SRAM的大小,不仅简化了设计,而且透过让同样基于MRAM的MCU用于多种应用中,可为某些客户节省成本。

目前,主流的MRAM技术是STT-MRAM(自旋注入MRAM),作为MRAM的一种变体,其附近电子的自旋会影响 MTJ( magnetic tunnel junction)的极性。与其他形式的 MRAM相比, STT-MRAM具有更低的功耗和进一步扩展的能力,虽然STT-MRAM具有与 DRAM和 SRAM相当的性能,比如即使切断电源,信息也不会丢失,而且和DRAM一样可随机存取;可擦写次数超过1015次,和DRAM及SRAM相当,大大超出了闪存的105次等,但其似乎也能在10nm以下进程实现,IMEC在2018年IEEE IEDM 会议上就曾展示了在 5nm 技术节点引入 STT-MRAM 作为最后一级 (L3) 缓存存储器的可行性,因此很多人认为STT-MRAM会改变“存储器(硬盘及NAND闪存)为非易失性、更高层级的内存(DRAM及SRAM)为易失性”的传统计算机架构,有望成为领先的存储技术。

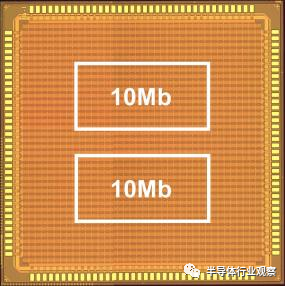

瑞萨主攻的就是STT-MRAM,并为其不断研发新技术。在去年年底的IEDM 2021上,瑞萨宣布确认在 16 nm FinFET 逻辑工艺嵌入式 STT-MRAM 测试芯片上降低了功耗并提高了写入操作速度。

瑞萨表示,MRAM 比闪存需要更少的写入操作能量,因此特别适合数据更新频繁的应用,但随着对 MCU 数据处理能力的需求激增,改善性能和功耗之间权衡的需求也在增加,进一步降低功耗仍然是一个紧迫的问题。为了满足这一需求,瑞萨为 MRAM 开发了两种技术,分别是利用斜率脉冲的自终止写入方案和同步写入位数优化技术。最后,瑞萨在采用 16 纳米 FinFET 逻辑工艺的 20 Mbit 嵌入式 MRAM 存储单元阵列测试芯片上进行的测量证实,上述两种技术的组合可将写入能量降低 72%,并将写入脉冲应用时间缩短 50%。

嵌入式STT-MRAM芯片照片

图源:瑞萨

而在今年6月的VLSI 研讨会上,瑞萨再次宣布已开发出用于STT-MRAM测试的威廉希尔官方网站 技术使用 22 纳米工艺制造的具有快速读写操作的芯片。瑞萨表示,随着物联网和人工智能技术的不断进步,需要采用更精细的工艺节点来制造MCU,对于亚 22 纳米工艺,在生产线后端中制造的 MRAM 与在生产线前端中制造的闪存相比具有优势,因为它与现有的 CMOS 逻辑工艺技术兼容并且需要更少的额外掩膜版。

嵌入式STT-MRAM测试芯片

图源:瑞萨

但瑞萨也指出,MRAM 的读取余量过小,会降低读取速度,进而影响MCU的性能,因此需要进一步提高速度以缩短端点设备所需的无线 (OTA) 更新的系统停机时间,为此瑞萨开发了采用高精度灵敏放大威廉希尔官方网站 的快速读取技术和同步写入位数优化和缩短模式转换时间的快速写入技术,经验证,在测试芯片上实现 5.9 ns 随机读取访问和 5.8 MB/s 写入吞吐量。瑞萨认为,这些新技术有可能显着提高内存访问速度超过 100 MHz,从而实现具有更高性能的集成嵌入式 MRAM 的MCU。

值得一提的是,不同于英飞凌和意法半导体应用于汽车电子,从瑞萨官方消息来看,目前其集成STT-MRAM技术的MCU主要应用在物联网领域,至于未来是否会转向汽车领域,我们拭目以待。

新兴存储,谁会是未来选择

那么,在众多新兴存储技术中,谁会成为未来选择?目前来看,PCM肯定走在了最前头,毕竟集成PCM的MCU样品已出货,量产时间也指日可待,但需要注意的是,PCM并不是一个十全十美的选择,它也有着一定的局限性。

一是,PCM RESET后的冷却过程需要高热导率,会带来更高功耗,且由于其存储原理是利用温度实现相变材料的阻值变化,所以对温度十分敏感,无法用在宽温场景。

二是,为了使相变材料兼容CMOS工艺,PCM必须采取多层结构,因此存储密度过低,在容量上无法替代NAND Flash。

三是,由于PCM典型的锗、锑、碲元素比例为25,熔点相对较低,或许会存在预编程的存储器在焊接到印刷威廉希尔官方网站 板上时可能被擦除的问题,虽然系统编程可以解决这个温度限制问题,但它也会影响在高温下10 年的保留能力。

其实,被大家所熟知的英特尔3D XPoint内存技术就是PCM的一种,由于所需要的掩膜版过多导致成本升高,并且制造难度也十分困难等原因,虽然这项技术在非易失存储器领域实现了革命性突破,但也没逃过落魄的命运。

另一边,MRAM虽然性能较好,但临界电流密度和功耗仍需进一步降低。目前MRAM的存储单元尺寸仍较大且不支持堆叠,工艺较为复杂,大规模制造难以保证均一性,存储容量和良率爬坡缓慢。

虽然上述说到,IMEC曾在2018年IEEE IEDM 会议上展示了在 5nm 技术节点引入 STT-MRAM 作为最后一级 (L3) 缓存存储器的可行性,但其实这项技术也被证明不足以将操作扩展到更快、更低级别的缓存 (L1/L2)。一方面,与SRAM相比,STT-MRAM写入过程仍然相对低效且耗时,对切换速度(不快于5ns)构成了固有限制。另一方面,速度增益将需要增加流过 MTJ 的电流,从而流过薄的电介质屏障,因此每一次的读写都会造成绝缘层的小破坏,久而久之也会降低设备的耐用性,显然对于需要亚纳秒切换速度的L1/L2 缓存操作来说,STT-MRAM并不是一个良配。

至于RRAM,它的缺点也很明显,最大的缺点就是严重的器件级变化性。器件级变化性直接关乎芯片的可靠性,但由于RRAM器件状态的转变需要透过给两端电极施加电压来控制氧离子在电场驱动下的漂移和在热驱动下的扩散两方面的运动,使得导电丝的三维形貌难以调控,再加上噪声的影响,因此容易造成器件级变化性。

此外,虽然RRAM阵列拥有两种机构,但是1T1R结构的RRAM总芯片面积取决于晶体管占用的面积,因此存储密度较低;而Crossbar结构的RRAM虽然存储密度较高,但存在互连线上的电压降和潜行电流路径,造成读写性能下降,能耗上升以及写干扰等问题。

总而言之,每种存储技术都各有优缺点,并没有完美的存在。MCU厂商如何进行取舍?如何尽可能针对弱项研发出新技术?又如何针对新兴技术研发出所需的新设备、新材料?这些都是不容忽视、且需要考虑的问题,但有一点可以确认,那就是哪怕是MCU厂商,也必须密切关注新兴存储技术的发展状况和态势,否则将会被竞争者抛在身后

编辑:黄飞

-

RTOS的存储器选择2019-06-28 0

-

集成铁电存储器的MCU有何作用2021-11-10 0

-

如何在MSP430™微控制器 (MCU) 中集成多种功能2022-11-04 0

-

MRAM实现对车载MCU中嵌入式存储器的取代2023-04-07 0

-

如何选择DSP芯片的外部存储器?2009-04-07 1916

-

相变存储器:能实现全新存储器使用模型的新型存储器2009-12-31 1183

-

浅谈存储器的“升存”之道2010-03-24 390

-

关于存储器的选择指南2018-06-26 3566

-

新型存储器将有望卷动千亿美元的内存市场2020-01-17 684

-

新型存储器与传统存储器介质特性对比2020-04-25 2954

-

集成铁电存储器MCU为物联网应用提供了出色的性能2020-11-17 726

-

集成铁电存储器MCU为物联网应用提供出色性能2021-11-05 616

-

存储器工作原理及如何选择存储器品牌2022-10-11 3823

-

在 MSP430™ 微控制器 (MCU) 中集成多种功能2022-10-28 504

-

一文了解新型存储器MRAM2023-04-19 3595

全部0条评论

快来发表一下你的评论吧 !