FPGA设计硬件语言Verilog中的参数化

可编程逻辑

1366人已加入

描述

1 参数化

FPGA 设计的硬件语言Verilog中的参数化有两种关键词:define 和 paramerter,参数化的主要目的是代码易维护、易移植和可读性好。

Parameter关键词类似于C语言中的形参可在其他模块调用时实例化参数,这个参数在运行过程中不能修改,在编译时就已经确定好了。

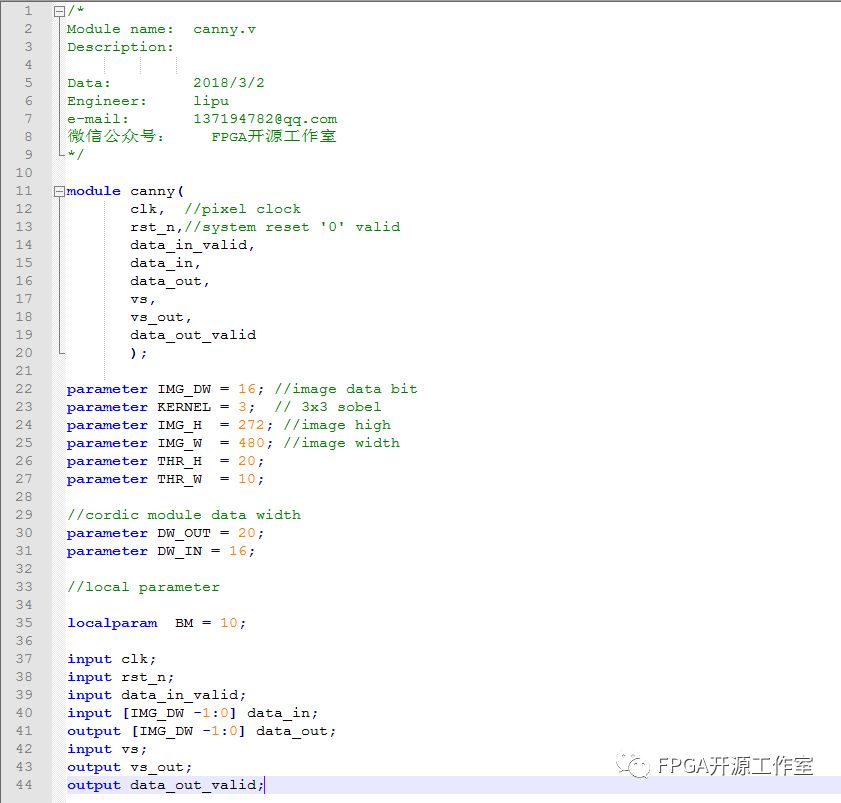

示例:

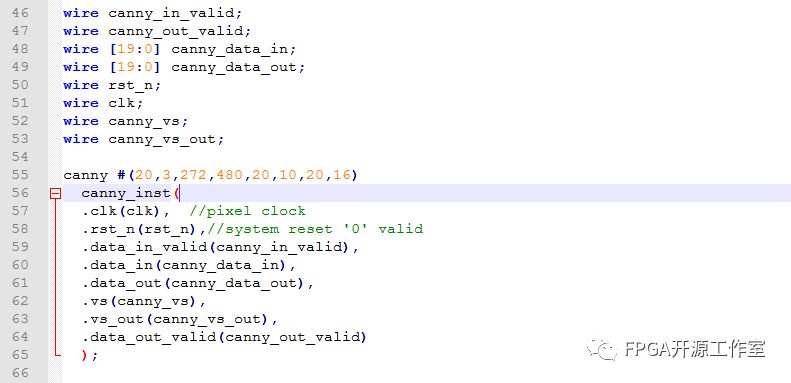

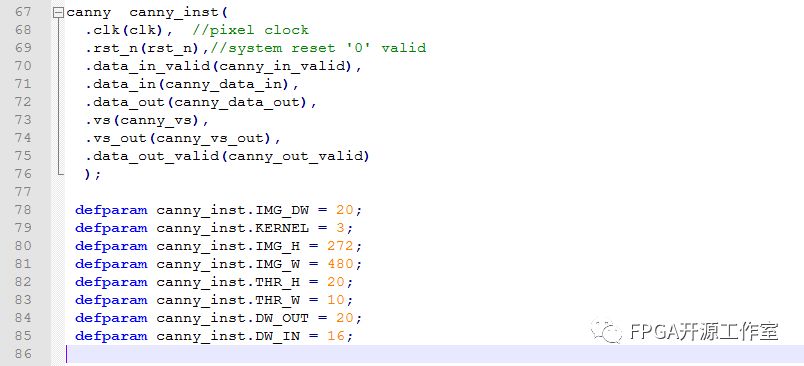

模块引用如下:

方式一:

方式二:

第一种方式必须按照顺序,而第二种方式可以顺序颠倒。所以在参数化比较多的情况下,尽量采用第二种方式,以避免顺序的错乱。

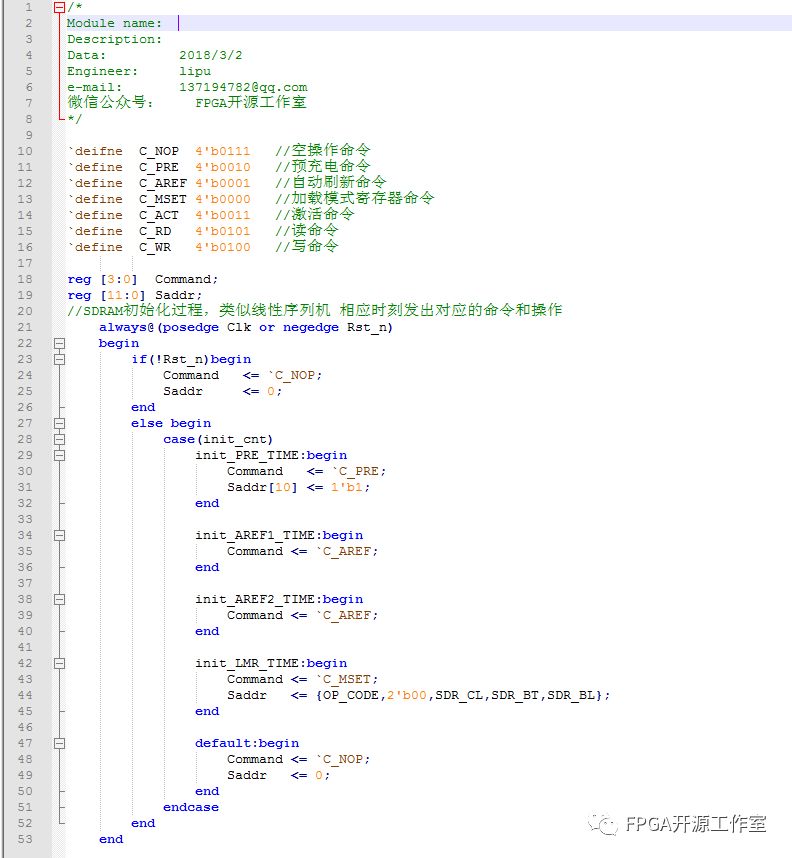

Define关键词类似于C语言中的define 。主要用于本地模块的一些定义,例如状态机。

示例:

2 条件编译

一般情况下,Verilog HDL源程序中所有的行都将参加编译。但是有时希望对其中的一部分内容只有在满足条件才进行编译,也就是对一部分内容指定编译的条件,这就是“条件编译”。

有时,希望当满足条件时对一组语句进行编译,而当条件不满足是则编译另一部分。

条件编译命令有以下几种形式:1) `ifdef 宏名 (标识符)程序段1`else程序段2`endif

2) `ifdef 宏名 (标识符)程序段1`endif

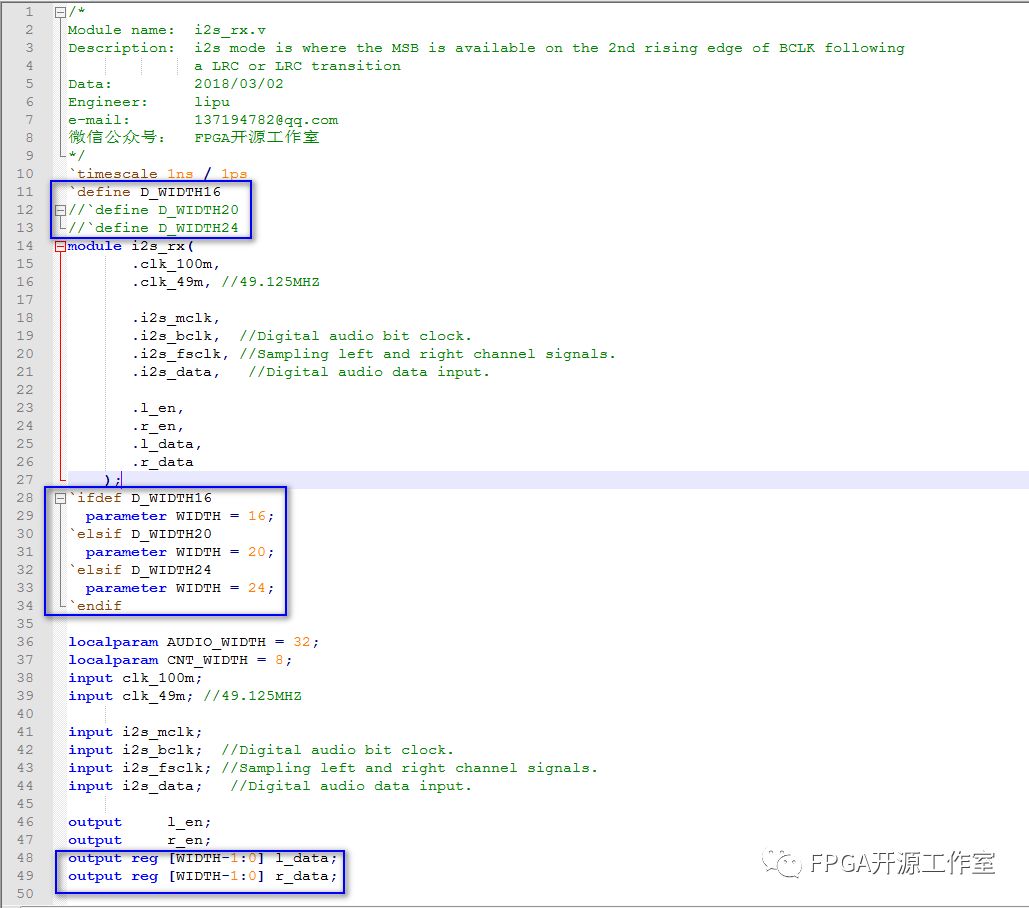

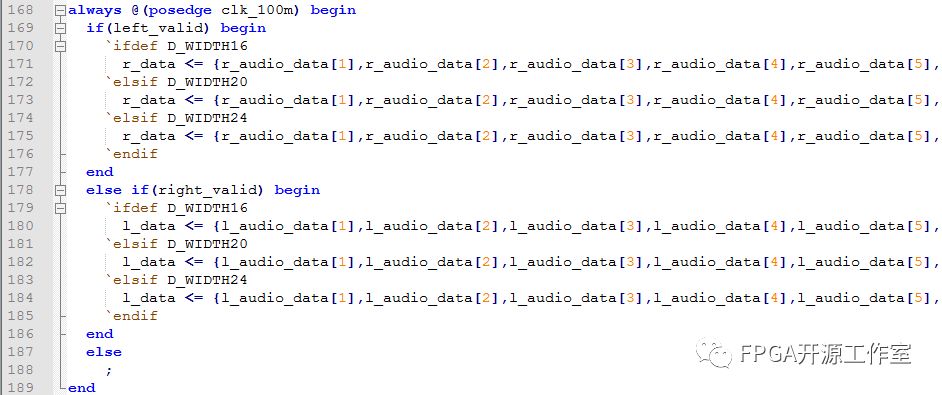

示例:

如上所示我们在写I2S的时候会遇到不同位宽的I2s数据,这就意味着对于不同的数据模块我们就要写一个文件。

如果采用条件编译就可以只写一个文件。当需要修改时只需要修改`define D_WIDTH16

//`define D_WIDTH20

//`define D_WIDTH24

就可以完成不同i2s数据位宽的修改。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Verilog_HDL硬件描述语言2013-02-26 0

-

学fpga的verilog语言怎么模块化2013-11-21 0

-

基于Verilog HDL语言的FPGA设计2009-08-21 525

-

Verilog HDL语言在FPGA/CPLD开发中的应用2009-06-20 1975

-

PLD/FPGA硬件语言设计verilog HDL2011-03-12 1787

-

verilog硬件描述语言课程讲义2012-05-21 822

-

Verilog硬件描述语言参考手册2015-11-12 703

-

Verilog硬件描述语言2016-09-01 699

-

基于FPGA Verilog-HDL语言的串口设计2017-02-16 1251

-

FPGA之硬件语法篇:Verilog关键问题解惑2019-12-05 1746

-

FPGA之硬件语法篇:用Verilog代码仿真与验证数字硬件威廉希尔官方网站2019-12-05 3345

-

FPGA CPLD中的Verilog设计小技巧2021-09-18 880

-

fpga用的是什么编程语言 fpga用什么语言开发2024-03-14 3499

-

fpga语言是什么?fpga语言与c语言的区别2024-03-15 941

-

fpga是用c语言还是verilog2024-03-27 1990

全部0条评论

快来发表一下你的评论吧 !