Verilog语法之generate for、generate if、generate case

描述

Verilog-2005中有3个generate 语句可以用来很方便地实现重复赋值和例化(generate for)或根据条件选择性地进行编译(generate if和generate case)等功能。接下来就一起看下这3个语句的应用场景和应用方法吧。

PART ONE

generate for

假设我希望把2个输入a[4:0]和b[4:0]做一个异或操作,但是顺序要颠倒,也就是这样:

module xor_test(

input[4:0]a,

input[4:0]b,

output[4:0]out);

assignout[4] = a[4] ^ b[0];

assignout[3] = a[3] ^ b[1];

assignout[2] = a[2] ^ b[2];

assignout[1] = a[1] ^ b[3];

assignout[0] = a[0] ^ b[4];

endmodule

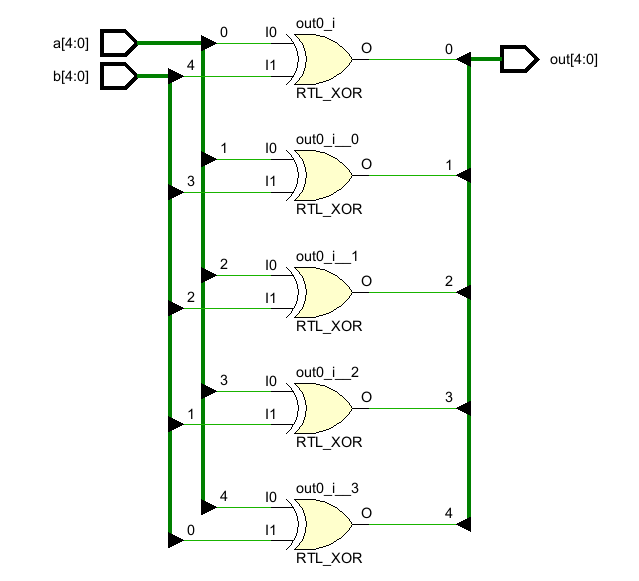

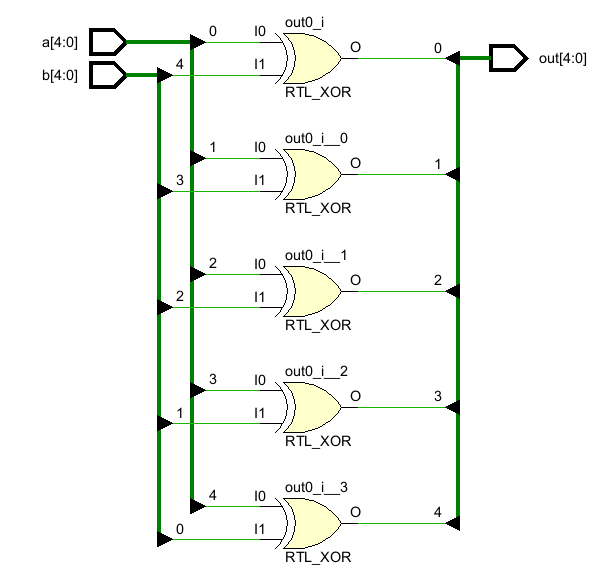

在vivado中分析出来是这样的:很简单就是两个输出的不同为做一个异或运算。

vivado综合出来是这样的:用了几个LUT来实现异或功能。

1应用场景

上面的例子限于篇幅我只假设了输入为5bit的位宽,所以这样写并不会让人觉得有多麻烦,但是假想一下如果位宽变成10、20、100呢?那我手不写断去?

当你需要进行一些重复性的工作时,比如多次例化同一模块、同一语句等,可以使用generate for语句来解放双手,节省工作量。当然你用脚本语言来生成或者直接用某些编辑器也能很快地实现这个功能,不过在这里我们就不提了。

上面的例子用generate for语句写是这样的:

module xor_test(

input[4:0]a,

input[4:0]b,

output[4:0]out

);

genvar i;//定义常量作为重复判断条件

generate

for (i = 0; i < 8; i = i + 1)//重复条件

begin: XOR_INST//begin要起个名字

assignout[i] = a[i] ^ b[4-i];//需要重复的语句

end

endgenerate

endmodule

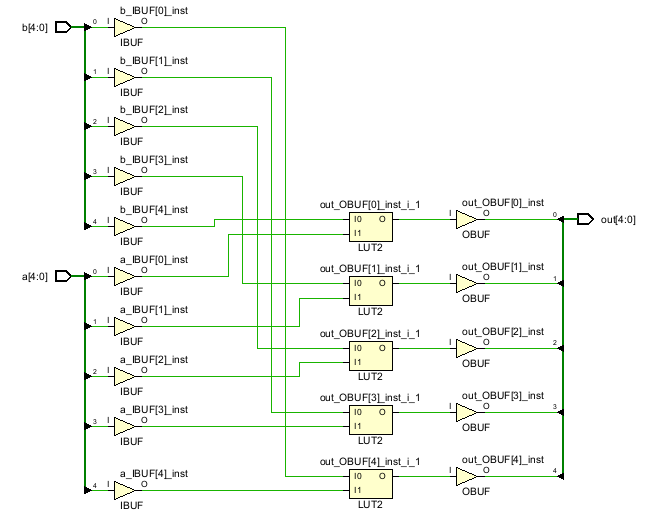

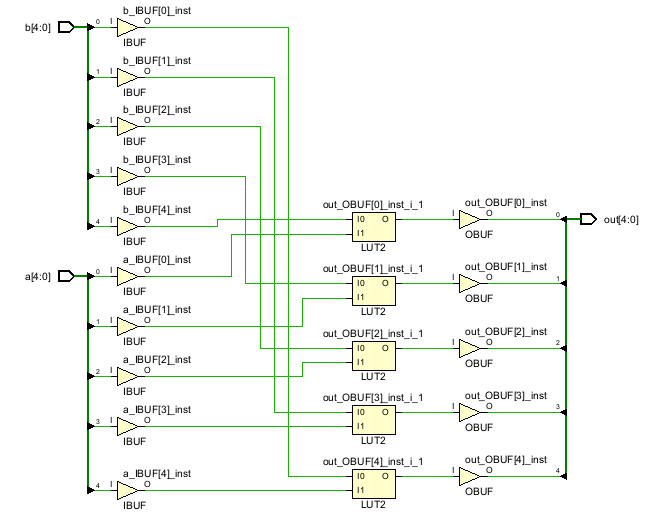

在vivado中分析出来是这样的:(与上面的方式一致)

vivado综合出来是这样的: (仍然与上面的方式一致)

这样看, generate for是个不错的提高效率的方案。当然,该语句不光可以对assign进行重复赋值,还适用以下场景:

(1)模块module;(2)用户定义原语UDP;(3)门级语句;(4)连续赋值语句assign;(5)initial和always块。

2格式

generate for语句的一般用法:

// Declare the loop variable

genvar;

// Code for the

generate

for (;;) begin

// Code to execute

end

endgenerate

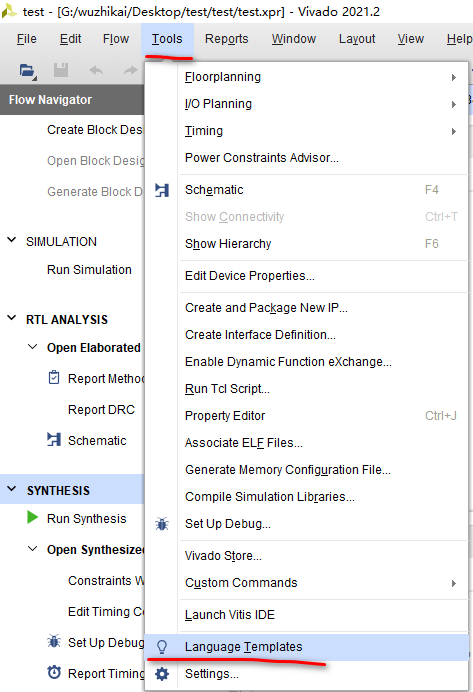

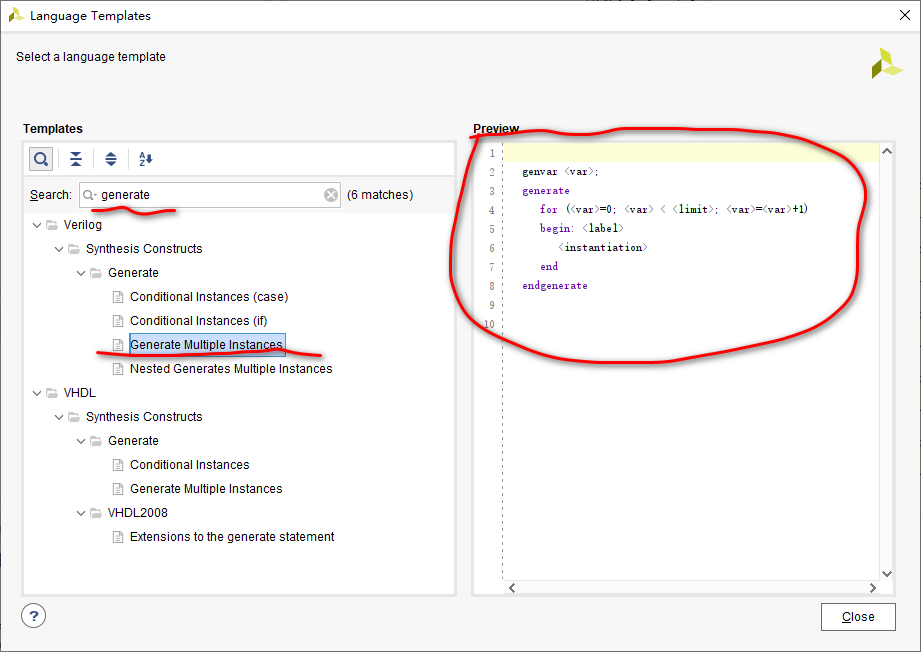

如果你是一个基于xilinx的开发者,可以使用vivado自带的语法模板:

(1)打开语法模板:

(2)搜索generate:

(3)把上图右侧的语句复制到你自己的代码里边。

关于generate for语句的使用需要注意:

generate for 语句必须使用genvar关键字定义for循环变量

generate for 循环必须加 begin…end, 哪怕只有一句

不要使用 i++这种C语言式的自增语句(Verilog没有i++这个语法),而是使用 i = i + 1

generate后不加begin,里面的语法:for循环、if…else…、case语句 后面的begin后面一定要加名字,且名字唯一,否则会导致无法比对通过的问题

过多的generate会导致收集覆盖率缓慢,要注意使用

PART TWO

generate if

generate if的使用场景和条件编译语句类似,比如你的代码中包含了一个加法模块和一个减法模块,对于2个输入a和b,希望使用POL来进行控制:如POL=1则进行加法,反之亦然----POL=1----out = a + b;POL=0----out = a - b。

代码是这样写的:

module xor_test(

input[4:0]a,

input[4:0]b,

output[4:0]out

);

localparamintegerPOL = 1;//根据POL的值来生成对应的威廉希尔官方网站

generate

if (POL == 1) begin: POL1

assignout = a + b;

end else begin: POL0

assignout = a - b;

end

endgenerate

endmodule

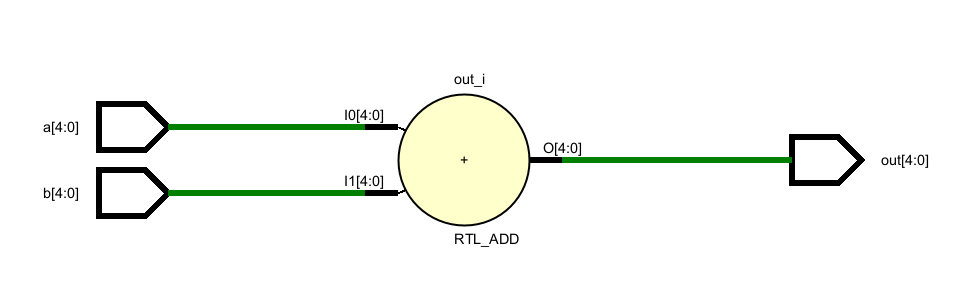

定义成POL = 1时会由vivado综合成一个加法器:

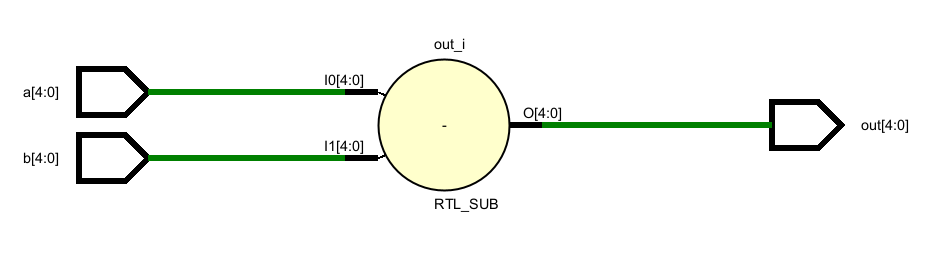

定义成POL = 0时则会由vivado综合成一个减法器:

假如不使用generate if语法,则代码是这样的:

module xor_test(

input[4:0]a,

input[4:0]b,

inputPOL,

outputreg[4:0]out

);

always@(*)begin

if(POL == 1)

out = a + b;

else

out = a - b;

end

endmodule

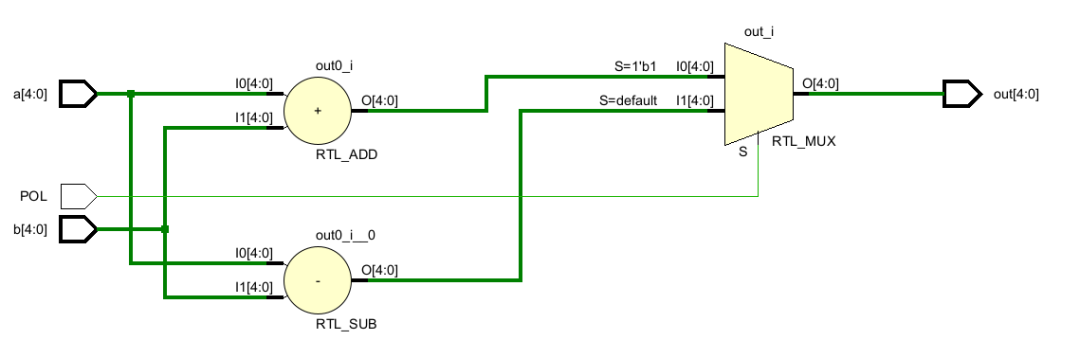

这样综合出来的就是加法威廉希尔官方网站 和减法威廉希尔官方网站 一起:

使用generate if可以根据需要来灵活地生成对应威廉希尔官方网站 ,不会浪费资源,适用于某些根据特定需求来实现威廉希尔官方网站 的场景。而不使用该语句则会把所有潜在的威廉希尔官方网站 均综合出来,会使威廉希尔官方网站 面积增大,但是灵活性却较高。

这是vivado自带的语法模板:

generate

if () begin:

;

end else if () begin:

;

end else begin:

;

end

endgenerate

PART TWO

generate case

generate case和generate if作用上是差不多的,都是用于选择性综合威廉希尔官方网站 ,区别就是if语句和case语句的区别,如果你会用其中一个,那另一个也很简单,模板如下:

generate

case ()

: begin:

end

: begin:

end

default: begin:

end

endcase

endgenerate

上面的例子照着改就是这样了:

module xor_test(

input[4:0]a,

input[4:0]b,

output[4:0]out

);

localparamintegerPOL = 1;//根据POL的值来生成对应的威廉希尔官方网站

generate

case(POL)

1'b1: begin: POL1

assignout = a + b;

end

1'b0: begin: POL0

assignout = a - b;

end

defaultDEFAULT end

endcase

endgenerate

endmodule

审核编辑:汤梓红

-

滢泉_892

2023-03-22

0 回复 举报有综合结果,一目了然 收起回复

滢泉_892

2023-03-22

0 回复 举报有综合结果,一目了然 收起回复

-

Generate Waveform.vi2012-07-09 0

-

Verilog中 generate if 语句如何用systemc实现?2014-08-28 0

-

Verilog 中generate if语句如何用systemc实现?2014-08-29 0

-

【梦翼师兄今日分享】 generate语句块的讲解2019-12-04 0

-

verilog中generate语句的用法分享2020-12-23 0

-

怎样去使用在Verilog语法中的Generate for功能呢?有哪些注意事项2022-08-02 0

-

Using References to Generate O2010-06-02 632

-

DAC and Op Amp Generate Variab2009-04-20 763

-

How to Generate PWM Waveforms2009-04-23 1302

-

Delphi资源生成器Delphi Resource Generate免费下载2017-12-12 633

-

Verilog generate语句的类型2018-03-16 21600

-

generate语句的基本概念与用法2019-11-21 5894

-

generate的用法与结构2022-09-27 4536

-

时序分析基本概念介绍<generate clock>2023-07-06 2288

全部0条评论

快来发表一下你的评论吧 !