使用Vitis加速RFSoC解决方案

电子说

描述

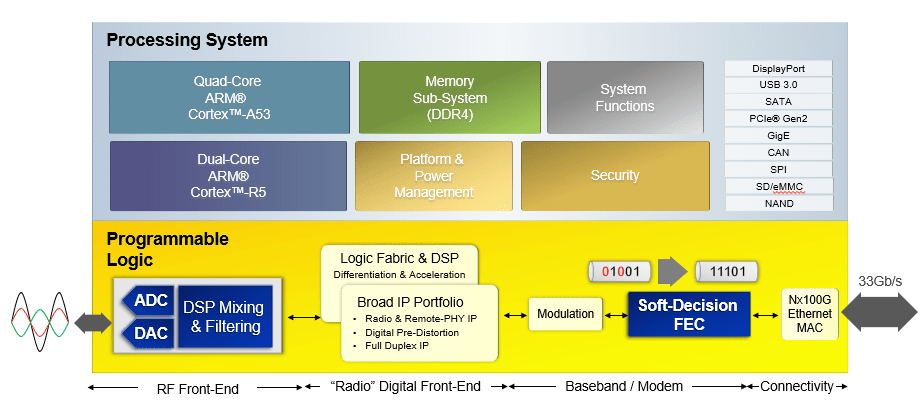

Xilinx的Zynq ® UltraScale+ ™ RFSoC系列器件是真正具有开创性的一类设备,它将射频数据转换器与信号设备中的高性能处理系统和可编程逻辑融合在一起。值得注意的是,射频数据转换器包括模数转换器 (ADC) 和数模转换器 (DAC) 以及生成和处理射频信号所需的所有元件。因此,RF 数据转换器提供数字上变频器和下变频器、混频器和数控振荡器。射频片上系统 (RFSoC) 还具有软决策、低密度奇偶校验前向纠错块,支持最新的前向纠错 (FEC) 编码方案,有助于最大限度地提高信道容量。

这种单芯片解决方案为系统开发人员提供了多项优势,包括紧密集成的解决方案,可显着减小威廉希尔官方网站 板的尺寸和复杂性,并降低整体功耗。Zynq UltraScale+ RFSoC 还为开发人员提供直接采样解决方案。得益于 RF 数据转换器中使用的 ADC 和 DAC,直接采样成为可能。它们提供高采样频率(第三代设备中为 10GSPS)和宽模拟输入带宽(第三代设备中为 6GHz)。使用直接采样方法消除了对提供向上或向下转换的模拟前端的需要。这提供了显着的系统级优势,因为这些模拟前端不可编程或容易适应支持许可或地理限制,

Zynq UltraScale+ RFSoC 还包含一个 64 位四核 Arm ® Cortex-A53 应用处理单元和一个 32 位双核 Arm Cortex-R5 实时处理单元(图 1)。

图 1:Zynq UltraScale+ RFSoC 框图概述了解决方案结构。(来源赛灵思)

实时控制和安全应用以及高性能应用可以在 Zynq UltraScale+ RFSoC 处理系统 (PS) 中实现。为支持接口,Zynq UltraScale+ RFSoC PS 还支持多种行业标准接口,例如 GigE、SATA、USB3、PCIe、CAN、I 2 C、SPI 等。同时,可编程逻辑与 GTY 串行器/解串器 (SERDES) 相结合,提供了支持所有通用公共无线电接口 (CPRI) 线路速率和高达 100GE 的能力。

RFSoC 解决方案的开发将努力利用可编程逻辑,以便从其并行结构提供的吞吐量、确定性和响应性中获益。当然,使用 Zynq UltraScale+ RFSoC 实施的解决方案会很复杂。软件无线电、雷达和测试设备就是很好的例子。纯粹在寄存器传输级 (RTL) 开发和实施这些算法可能非常耗时,并且会影响上市时间。

实现最佳上市时间同时仍允许开发人员利用可编程逻辑的并行特性的一种方法是使用 Xilinx 的 Vitis ™统一软件平台。Vitis 使用户能够将算法从处理系统加速到可编程逻辑。当与 Xilinx 异构片上系统设备或加速卡一起使用时,由于高级综合和 OpenCL ™ ,这种加速成为可能。

使用 Vitis 和 OpenCL 加速

Vitis 使用户能够利用 OpenCL 框架在可编程逻辑中实现加速内核。这些加速内核是使用比传统 RTL 更高级的语言定义的。

OpenCL 是一个行业标准框架,支持异构系统上的并行计算。OpenCL 背后的核心原则之一是无需更改代码即可启用跨平台功能。这允许相同的代码可以跨 CPU、GPU、FPGA、DSP 等移植,性能扩展取决于平台的功能。

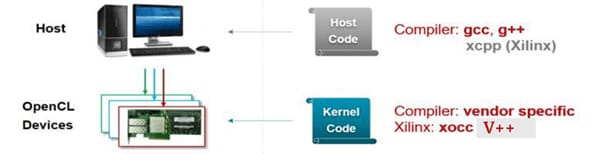

OpenCL 使用主机和内核模型(图 2)。每个系统都有一个主机(通常是基于 x86 的)和几个提供加速的内核,通常是基于 GPU、DSP 或 FPGA 的。为支持 OpenCL 流程,主机应用程序通常使用 C/C++ 开发并使用 OpenCL API。这些 OpenCL API 允许主机管理加载、配置和执行内核的整个应用程序生命周期。在支持跨平台移植的同时,内核使用OpenCL C语言开发,基于C语言,但在支持跨平台移植方面存在局限性。

该模型允许使用 GCC 或 G++ 等标准编译器编译主机程序,而内核编译器是特定于供应商的。

图 2:该图显示了 Open CL 结构如何使主机程序能够使用标准编译器,而内核使用特定于供应商的编译器。(来源:赛灵思)

使用 Xilinx 异构片上系统设备时,Arm 应用程序处理单元是主机,而可编程逻辑实例化内核。Vitis 为开发人员提供了在针对 Xilinx 异构 SoC 或加速卡时生成、调试和分析主机和内核元素所需的一切。

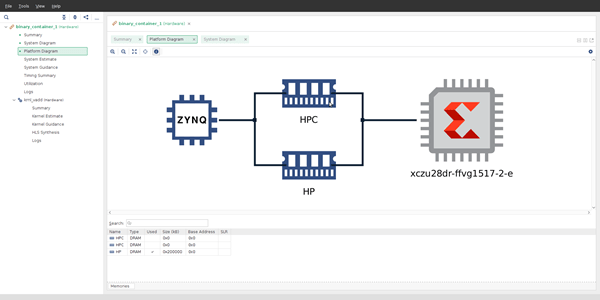

Vitis 平台

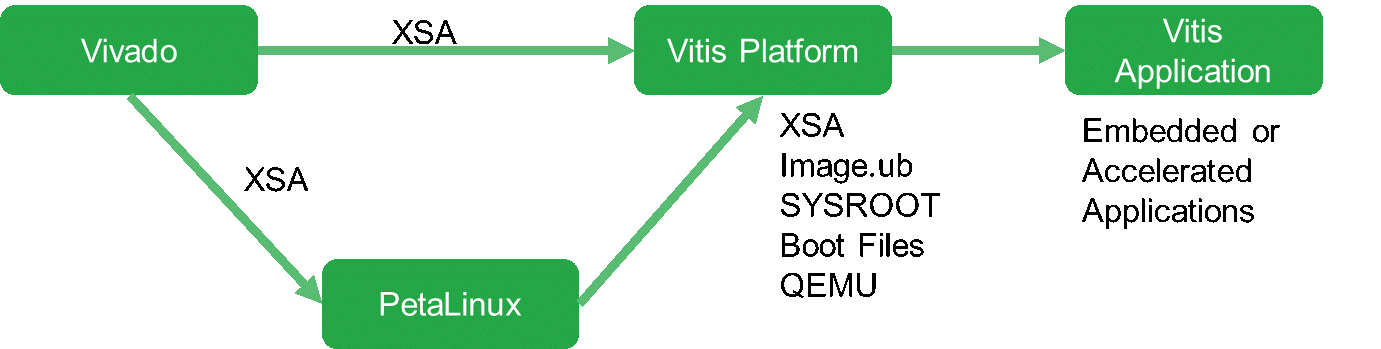

为了能够利用 Vitis OpenCL 功能,需要一个基础平台。该基础平台定义了底层硬件的硬件和软件配置。硬件平台使用 Vivado ® Design Suite 创建,提供可用时钟、高级可扩展接口处理系统/可编程逻辑 (AXI PS/PL) 接口,并中断 Vitis 编译器。使用这些接口,Vitis 编译器可以将加速内核连接到处理系统内存映射中。这允许使用直接内存访问 (DMA) 和内核控制进行高效的数据传输。该平台的软件元素由 PetaLinux 提供,并提供支持赛灵思运行时 (XRT) 的嵌入式 Linux 操作系统(图 3)。

图 3:该图说明了 Vitis 平台开发流程。(来源:作者)

当然,在 Vivado 中开发的基础平台也可以包含设计元素和 Vitis 可用的挂钩。在 Zynq UltraScale+ RFSoC 的情况下,基础设计可以包括必要的基础设施,以使用 GTY 收发器将 RF 数据转换器连接到外部接口或在处理器内存空间之间传输数据。

葡萄加速

一旦加速平台可用,开发人员就可以开始使用 Vitis 开发他们的解决方案。使用 Vitis,他们可以实现 RF 数据转换器和附加 IP 的控制和配置。然后,开发人员还可以使用 C/C++ 和 OpenCL C 实施所需的 RF 数据处理算法,以加速解决瓶颈并提高整体系统性能。

为了帮助开发算法,Vitis 提供了几个开源加速就绪库(图 4)。这些库包括对数学、线性代数、DSP、数据压缩,当然还有 AI 的支持。

图 4:Vitis 开发环境提供开源加速就绪库来帮助设计解决方案。(来源:作者)

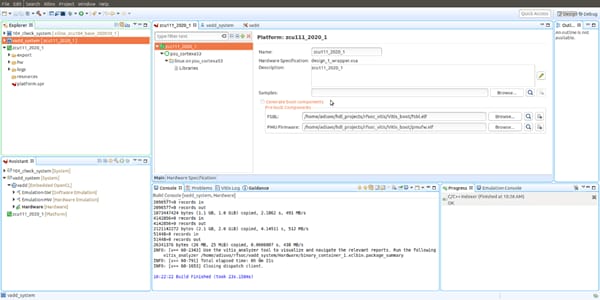

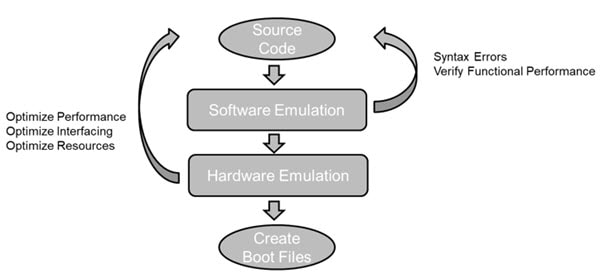

实现软件算法后,开发人员可以使用 Vitis 提供的软件和硬件仿真流程来优化算法,以便在生成最终引导映像之前在可编程逻辑中实现(图 5)。

图 5:Vitis 应用开发流程在创建最终引导映像之前使用可编程逻辑中的软件和硬件仿真优化算法。(来源:作者)

为了利用可编程逻辑的并行特性,开发人员可能希望在内核中流水线化或展开循环、组织内存和 AXI 接口结构。这些优化是使用源代码中的编译指示实现的。可以使用 Vitis Analyzer 和 Vitis HLS 分析视图来识别优化内核代码的潜在区域(图 6)。

图 6: Vitis Analyzer 平台视图可帮助开发人员确定优化内核代码的潜在区域。(来源:作者)

优化完成后,开发人员可以构建最终的引导文件并部署系统以进行下一阶段的测试和验证。

包起来

RFSoC 与 Vitis 的 OpenCL 功能相结合,为开发人员提供了突破性的紧密耦合解决方案。该解决方案可以通过利用高级语言、库和框架来提供最具响应性和确定性的解决方案。这种开发方法支持采用更高级别的系统驱动方法来实施解决方案,从而缩短上市时间。

审核编辑:汤梓红

-

Vitis2023.2使用之—— classic Vitis IDE2024-03-24 0

-

Vitis2023.2使用之—— updata to Vitis Unified IDE2024-03-24 0

-

立体智慧仓储解决方案.#云计算学习电子知识 2022-10-06

-

【解决方案】加速海啸模拟2018-07-27 0

-

【KV260视觉入门套件试用体验】Vitis-AI加速的YOLOX视频目标检测示例体验和原理解析2023-10-06 0

-

浅谈Vitis 加速库 可扩展,灵活度高2020-11-23 1715

-

Vitis定量金融库提供优化功能,加速计算解决方案2020-12-02 1576

-

Vitis 更新了?获奖了?还不快来体验吗?2020-12-09 1421

-

如何在Vitis中封装加速平台?2020-12-26 2819

-

Vitis视频分析SDK构建自己的智能视频分析解决方案2021-11-08 4191

-

基于Vitis HLS的加速图像处理2022-02-16 2459

-

基于软件的Vitis AI 2.0加速解决方案2022-03-15 2344

-

Vitis HLS工具简介及设计流程2022-05-25 2385

-

揭秘Vitis嵌入式加速平台的创建2023-09-14 136

-

Vitis加速库:广泛且性能优化的开源库2023-10-30 754

全部0条评论

快来发表一下你的评论吧 !