前段集成工艺(FEOL)

描述

锗硅(SiGe)外延(p-MOS源漏)

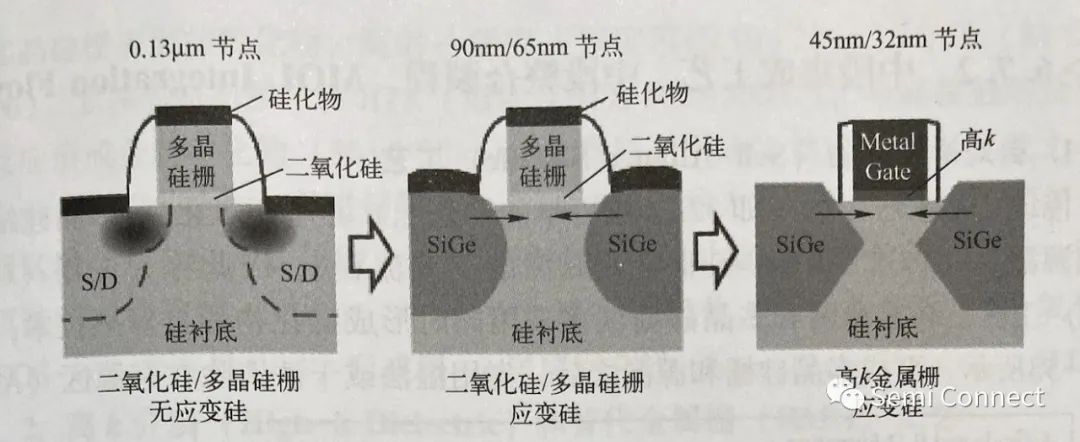

自 32 nm节点以来,CMOS 器件结构已从多晶硅栅(如硅氧化/多晶硅结构)和非应变源漏结构演变到利用高k栅介质/金属栅 (high-k/ Metal-Gate, HKMG)和应变硅源漏,如图所示。

其制造工艺流程如下:首先形成补偿侧墙 (Offset Spacer),经n+/p+轻掺杂源漏后,选择性地进行图形化,在p型源漏区先进行干法刻蚀,使其凹陷适当的深度(30~100nm);然后采用湿法各向异性刻蚀形成“钻石”形腔(Diamond Cavity,又称“∑”形状);接着外延锗硅(SiGe)形成p-MOS 的源漏,p型掺杂可由原位硼摻杂或硼离子注入和快速热退火(RTA) 来形成。p型源漏的钻石形锗硅面向沟道的邻近尖点(Diamond Tip),可有效地增强沿沟道方向的压应力,因此也增强了沟道空穴迁移率。

审核编辑 :李倩

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

#硬声创作季 #集成威廉希尔官方网站 集成威廉希尔官方网站 制造工艺-03.3.1光刻工艺的基本流程-光刻工艺的基本流程水管工 2022-10-17

-

#硬声创作季 #集成威廉希尔官方网站 集成威廉希尔官方网站 制造工艺-03.4先进的光刻工艺-先进的光刻工艺水管工 2022-10-17

-

#硬声创作季 #集成威廉希尔官方网站 集成威廉希尔官方网站 制造工艺-08.1.3芯片组装工艺流程-划片工艺水管工 2022-10-17

-

#硬声创作季 #集成威廉希尔官方网站 集成威廉希尔官方网站 制造工艺-10.3CMOS中其他相关工艺水管工 2022-10-17

-

猎头职位——封测前段工艺设备经理2013-08-01 0

-

沈阳芯源微电子设备有限公司 前段TRACK工艺工程师2015-12-26 0

-

集成威廉希尔官方网站 前段设计流程2021-07-23 0

-

集成威廉希尔官方网站 制造工艺2016-04-15 847

-

12吋晶圆集成威廉希尔官方网站 芯片制程工艺与工序前端FEOL第二部分免费下载2019-04-10 1384

-

MEMS工艺前段制程的特点及设备2021-01-11 2464

-

前段集成工艺(FEOL)-42022-12-09 1755

-

cmp是什么意思 cmp工艺原理2023-07-18 15588

-

用于Chiplet 3D系统的硅光Interposer工艺架构介绍2023-08-02 6165

-

前段制程FEOL—晶圆上的元件制程2024-04-03 1204

-

大马士革铜互连工艺详解2024-12-04 815

全部0条评论

快来发表一下你的评论吧 !