一文详解带复位的SR触发器和JK触发器

描述

带复位的SR触发器

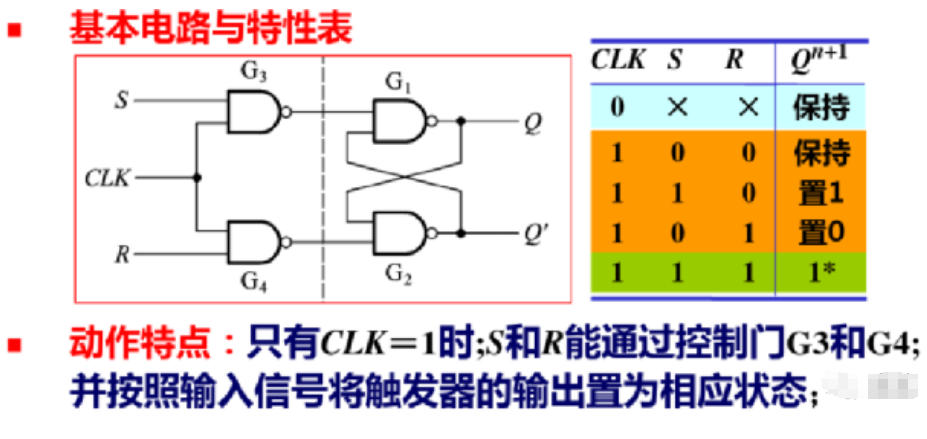

图1是基本SR触发器及其真值表。

图1 基本SR触发器及其真值表

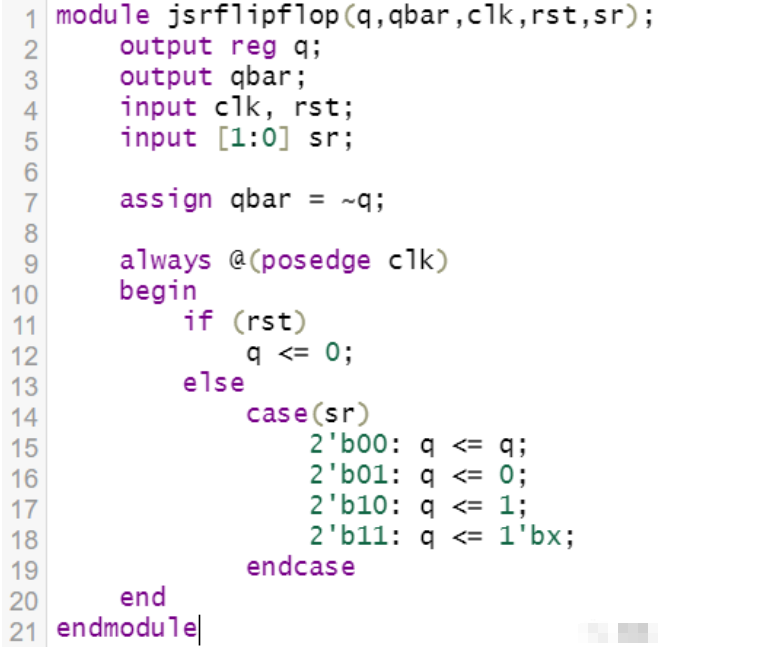

图2 异步复位SR触发器的verilog描述

图2的SR触发器在图1的基本SR触发器的基础上添加了异步复位,所以多了一个rst信号,当rst为高电平,则SR触发器复位到0。当rst为低电平时,那么此时该触发器的功能和基本SR触发器一致。

另外该module将SR触发器中的S和R信号合并为一个2bit位宽的一个信号input [1:0] sr,在综合工具编译的时候应该会编译成sr[0]和sr[1](高低位)。

带复位的JK触发器

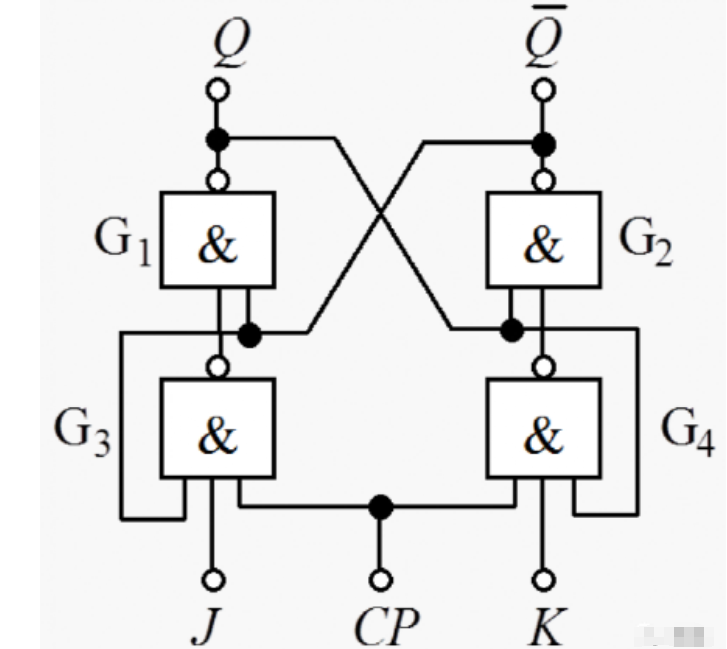

JK触发器是数字威廉希尔官方网站 触发器中的一种基本威廉希尔官方网站 单元。JK触发器具有置0、置1、保持和翻转功能。在各类集成触发器中,JK触发器的功能最为齐全。在实际应用中,它不仅有很强的通用性,而且能灵活地转换其他类型的触发器。由JK触发器可以构成D触发器和T触发器。

图3 基本JK触发器

图4 基本JK触发器真值表

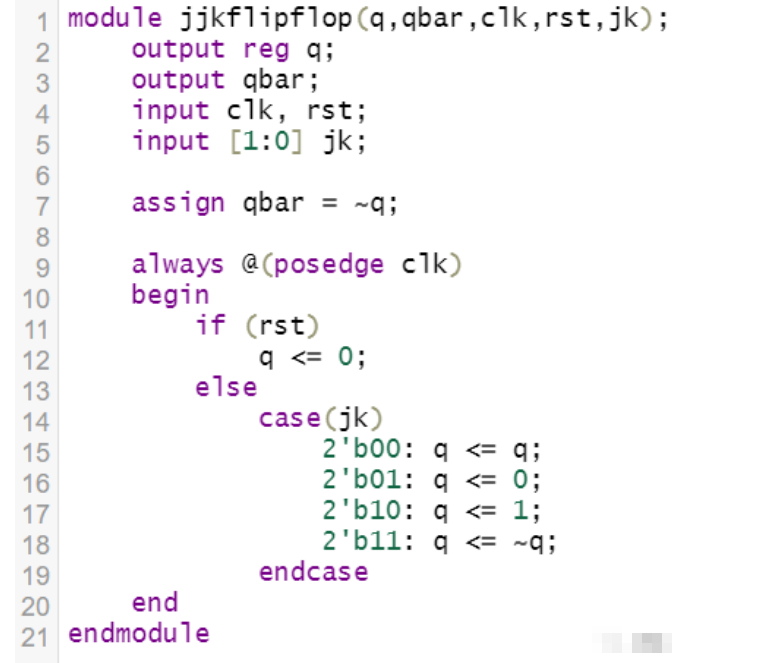

图5 带复位的JK触发器的verilog描述

该JK触发器module描述与上述的SR触发器类似,唯一的区别在于真值表的不同。

D触发器

D触发器是常用的触发器,时钟高电平下,D端数据赋值给Q端。

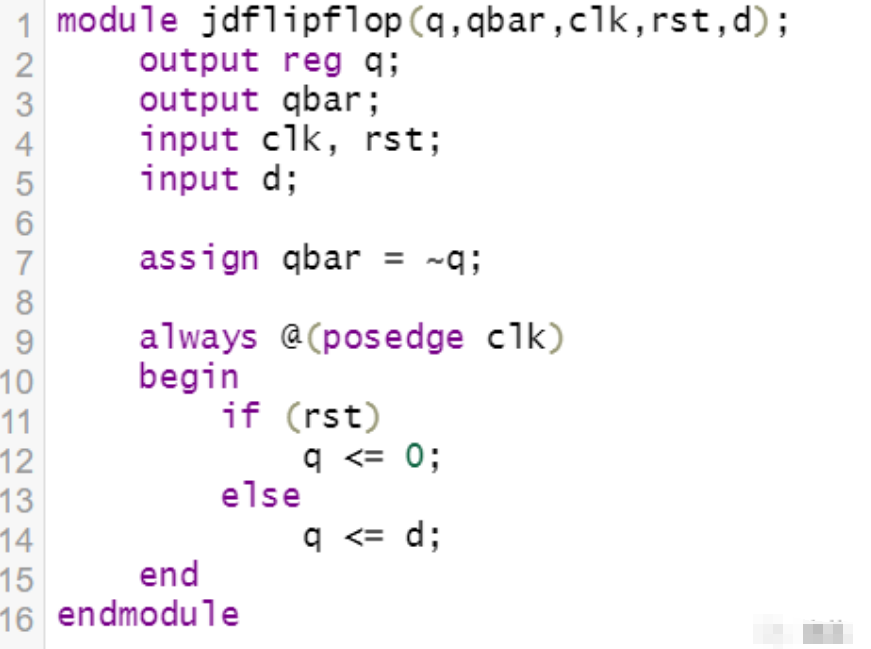

图6 D触发器verilog描述

T触发器

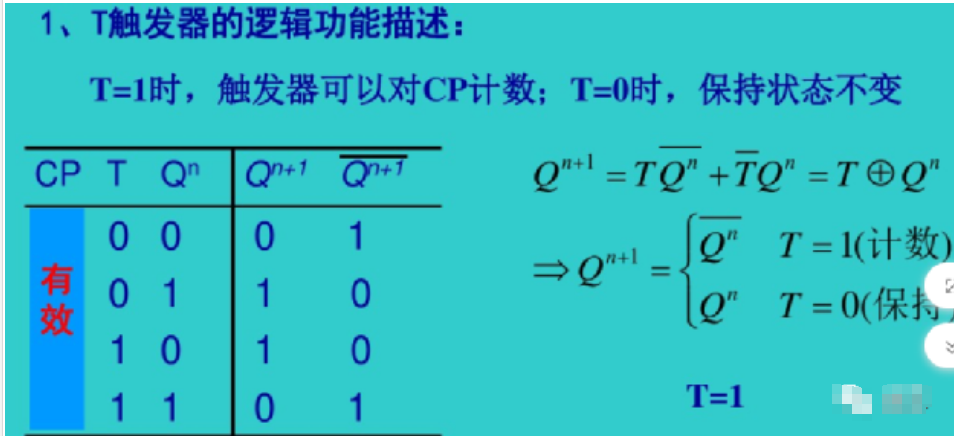

图7是基本T触发器。

图7 T触发器

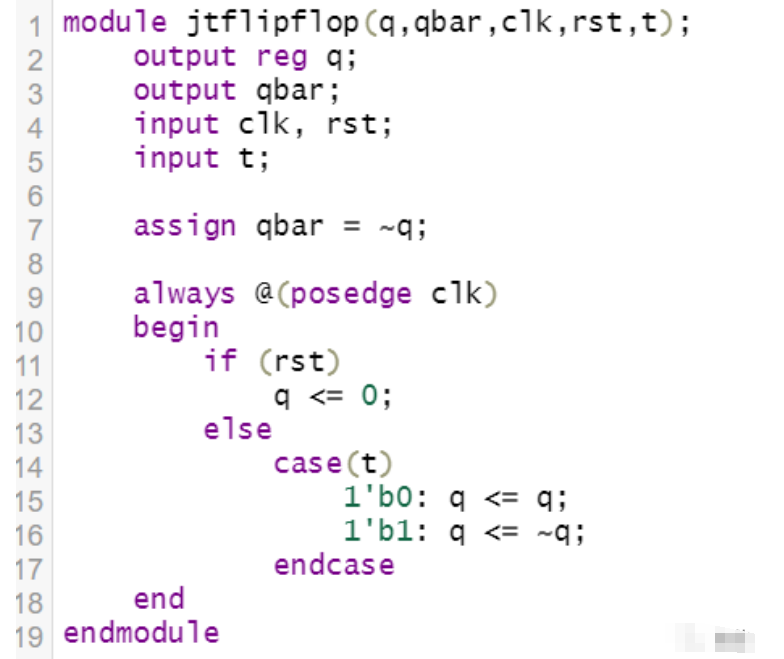

图8 T触发器的verilog描述

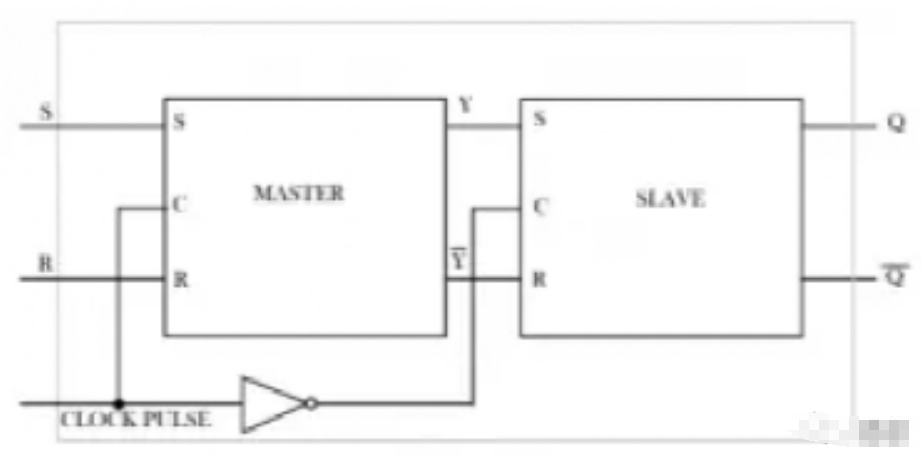

主从触发器

主从是串联连接的两个触发器的组合,其中一个充当主机,另一个充当从机。每个触发器都连接一个互补的时钟脉冲,即如果时钟脉冲处于高电平状态,则主触发器处于使能状态,从触发器处于禁用状态,如果时钟脉冲为低电平,主触发器处于禁用状态,从触发器处于启用状态。主从触发器也称为脉冲触发器,因为在此操作模式下,触发器可以通过 CLK 脉冲启用或禁用。

图9 主从触发器

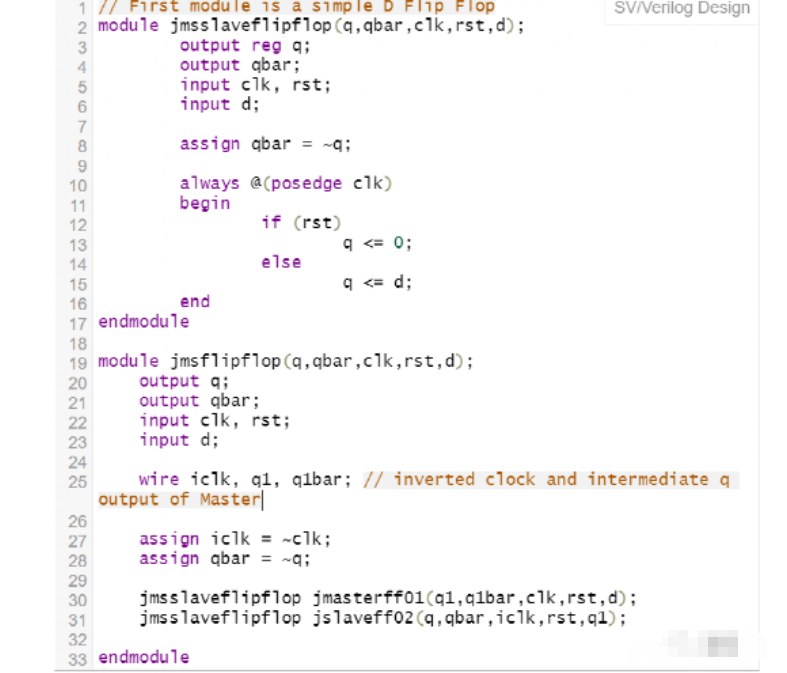

图10 主从触发器verilog描述

在主从触发器中我们可以看到,verilog描述提前定义了一个基本D触发器,并在描述中调用了两次该module。主从触发器中的主触发器的输入pin从module端口定义,从触发器的输入pin用wire变量定义。

-

JK触发器基本教程,讲的超详细!!2021-02-01 0

-

JK触发器,JK触发器是什么意思2010-03-08 6852

-

JK触发器原理是什么?2010-03-08 23913

-

jk触发器是什么原理_jk触发器特性表和状态转换图2017-12-25 188636

-

JK人字拖触发器和函数表2019-06-26 6527

-

JK触发器逻辑符号_jk触发器的特性方程2019-11-08 93698

-

带复位功能的双 JK 触发器;下降沿触发-74HC732023-02-15 627

-

带复位功能的双 JK 触发器;下降沿触发-74HC_HCT107_Q1002023-02-16 356

-

带复位功能的双 JK 触发器;下降沿触发-74HC_HCT1072023-02-16 643

-

带复位功能的双 JK 触发器;下降沿触发-74HC73_Q1002023-02-17 571

-

t触发器和jk触发器的区别和联系2024-02-06 6140

-

如何用jk触发器构成t触发器?t触发器逻辑功能有哪些2024-02-06 8885

-

JK触发器的置位和复位有什么区别2024-07-27 2303

-

JK触发器是一种什么稳态威廉希尔官方网站2024-08-22 955

-

怎么用jk触发器变成t触发器2024-08-28 2787

全部0条评论

快来发表一下你的评论吧 !