了解宽带GSPS ADC中的无杂散动态范围

模拟技术

描述

在为高性能系统选择宽带模数转换器(ADC)时,应考虑许多模拟输入规格,例如ADC分辨率、采样速率、信噪比(SNR)、有效位数(ENOB)、输入带宽、无杂散动态范围(SFDR)以及差分或积分非线性。

对于每秒千兆采样(GSPS)ADC,SFDR可能是最重要的交流性能规格之一。它定义了ADC和系统从其他噪声或任何其他杂散频率中破译载波信号的能力。

为了实现GSPS ADC中使用的转换速度,可以采用几种以高目标采样率捕获信号的架构。但是,其中一些架构的使用是以牺牲全带宽 SFDR 性能为代价的。

为了了解转换器SFDR对系统的影响,我们回答了设计工程师提出的一些常见问题,包括SFDR规范的细节、转换器数据手册中如何描述SFDR规范、限制或最大化ADC性能的架构以及限制SFDR性能的系统设计方面。

我已经看到SFDR在数据表中有和没有警告。究竟什么是 SFDR?

能够从噪声中辨别信号是许多信号采集系统的一个关键方面。无论是定义的电信协议、雷达扫描还是测量仪器,采集和破译微弱信号都是任何差异化系统性能的核心。

SFDR表示可以与大干扰信号区分开来的最小功率信号。它定义了载波功率的均方根(rms)值与频域中下一个最重要杂散信号的均方根值之间的动态比,例如在快速傅里叶变换(FFT)中。因此,根据定义,该动态范围必须没有其他杂散频率或杂散。

SFDR通常量化为相对于目标载波与下一个最重要频率的功率的范围,以功率单位(dBc)为单位。但是,它也可以参考以功率单位(dBFS)为单位的满量程信号。这是一个重要的区别,因为目标载波可能是功率相对较低的信号,远低于ADC的满量程输入。在这种情况下,SFDR在将信号与其他噪声和杂散频率区分开来方面变得至关重要。

什么限制了 ADC 的 SFDR?

谐波频率是基频的整数倍。对于设计良好的单芯片ADC内核,SFDR通常由载波频率与目标基频的二次或三次谐波之间的动态范围决定。一些窄带ADC数据手册仅在窄带内定义SFDR,通常是当二次和三次谐波落出带外时。其他数据手册可能会描述宽带宽下的SFDR,并需要注意该性能需要满足哪些条件。

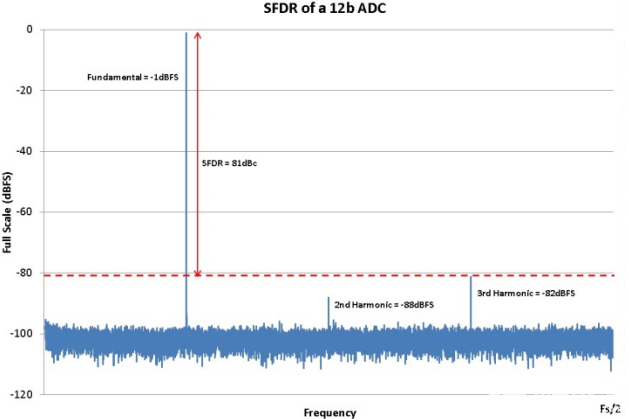

虽然二次或三次谐波通常可能是主要的杂散频率,但由于其他系统原因,有些杂散也可能限制GSPS ADC的SFDR性能。例如,多个交错式ADC内核可以通过在频域中引入交错伪像来创建杂散频率。这些可能在幅度上大于基频的二次或三次谐波。因此,它们将是SFDR的主要限制因素。虽然这似乎违反直觉,但SFDR也可以在交错式ADC数据手册中指定,并告诫交错杂散被排除在计算之外(图1)。

图1.这是单芯片12位ADC的FFT,显示三次谐波是SFDR的主要贡献因素。在这种情况下,从基波(–1 dBFS)到三次谐波(–82 dBFS)的动态范围为–81 dBc,因为它与载波功率有关。

窄带SFDR可以外推到宽带SFDR吗?

如果系统只关注窄带频谱,则可以使用带通抗混叠输入滤波器来抑制目标频带外的谐波或伪影。这对于某些应用可能工作正常,只要不需要观察此滤波频带内的信号即可。但对于宽带信号采集系统来说,这是不可行的。在某些数据手册中,ADC的SFDR也可以指定在远小于ADC全输入带宽的窄带宽上。

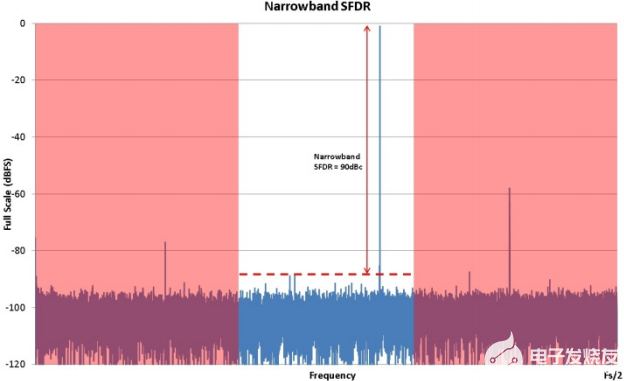

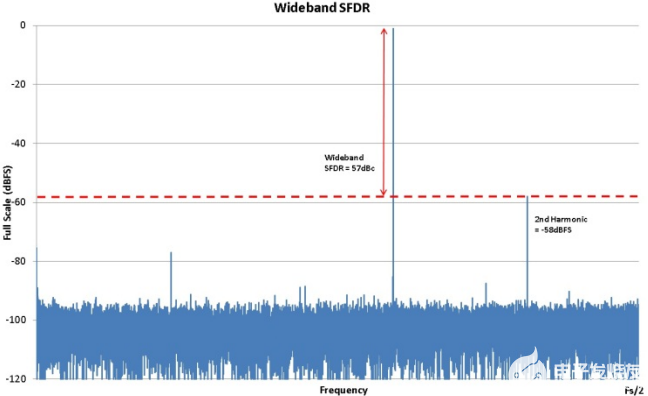

通常,不能假设可以外推窄频带上的SFDR,以便在Fs/2的更宽或全奈奎斯特频带上获得相同的性能。这主要是因为基波窄带的频率规划是有意建立的,以滤除并将高次谐波推出目标频带。如果去掉滤波器,那么这些谐波和其他杂散现在将成为系统中宽带SFDR的一部分(图2和图3)。

图2.窄带应用可以有效地使用宽带SFDR较差的ADC。通过使用抗混叠滤波器来抑制红色阴影区域的频率,任何谐波或杂散现在都会被带外滤除,否则会导致SFDR较差。

图3.使用相同的条件,但假设ADC滤波被移除,那么宽带谐波或杂散现在将限制SFDR。这说明了一种情况,即不能假设将优秀的窄带SFDR外推到宽带SFDR。

差分输入ADC的SFDR是否会受到其他前端系统组件的影响?

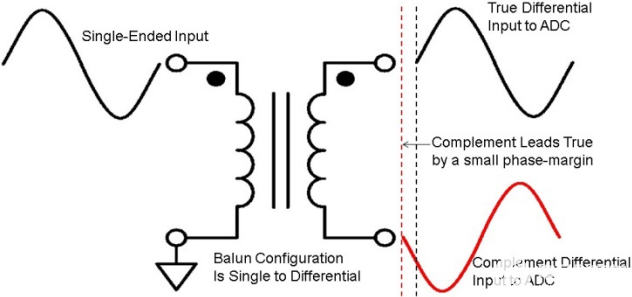

大多数高速ADC采用差分输入结构,可提供良好的共模噪声抑制能力。然而,这需要许多采集系统将单端信号转换为ADC输入前端的差分信号。无源巴伦或变压器和有源放大器是这种单差信号转换过程的主要选择。虽然系统这一部分有许多高性能元件选择,但即使是最好的解决方案也会嵌入一些小的差分不平衡,这些不平衡会使目标信号失真,并通过ADC降低SFDR。

ADC前端差分输入信号每侧之间的相位失配导致基波信号谐波的功率增加。当差分信号的一侧相对于其周期在时间上领先另一侧一定量的相位时,就会发生这种情况。这种效应如图4所示,当差分对的一侧领先另一侧时,周期相位的幅度很小。

图4.在这种情况下,巴伦输出与ADC差分输入的相位失配为几度。这可能导致FFT中的二次谐波高于差分输入相位完美匹配时的二次谐波,从而影响SFDR。

差分信号采集系统前端的另一个不平衡可能是幅度失配。当差分信号的一侧增益与其补码不同时,ADC输入将一侧视为较大的信号,另一侧视为较小的信号。否则,这会降低基波信号的全部功率,并降低SFDR(以dBc为单位)。差分输入之间2 dB幅度失配将导致输入信号功率满量程降低1 dB。这些前端信号完整性问题都有可能降低ADC的SFDR以及整个系统的信号解密能力。

有哪些ADC架构可能会限制SFDR?

采样速率高达1 GSPS及以上的多个ADC采用一对或几个分立通道或内核的交错方案,以实现全高速数据速率。例如,可以使用双通道ADC,每个内核通过交错在采样采集过程中旋转,以实现全采样速率。当一个通道正在采样时,另一个通道仍在处理以前的样本。交错架构还可以使用三个或更多ADC内核。

使用交错方法,多个ADC内核可以并行工作,以实现比单个内核更高的采样速率。但是,每个内核的输入之间存在相位、偏移、增益和带宽的细微差异。结果是可以在频谱中引入新的交错伪像和镜像杂散,从而降低ADC的宽带SFDR。这将降低系统的动态范围及其区分目标信号和交错杂散信号的能力。为了减轻交错式ADC的伪影,系统工程师可能必须阅读有关特殊校准模式和杂散规划方法的详细应用笔记。

单芯片ADC架构只有一个处理内核,不会出现交错杂散。单流水线内核ADC是宽带转换器的一个例子,它将吹捧相对较高的SFDR,通常受二次或三次谐波的限制。

交错ADC在频域中的性能如何?

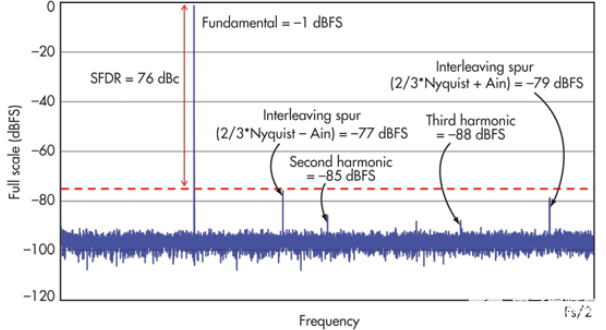

对于包含三个分立交错内核的采样架构,有两个增益和相位镜像杂散和一个失调杂散(图 5)。在奈奎斯特× 2/3 处可以看到偏移杂散,但在这种情况下不是 SFDR 的主要贡献者。SFDR限制增益和相位杂散在(2/3 × Nyquist ±模拟输入频率下可见。

图5.本FFT显示了交错系统板上使用的三个分立ADC。请注意相关的交错杂散伪像,与二次谐波(–8 dBFS)相比,这些伪像将SFDR限制为–85 dBc。

规模上最大的刺激将是该系统SFDR的主要贡献者。如果没有交错杂散,SFDR将是从基频到二次谐波的动态范围。在这种特殊情况下,由于交错镜像杂散,SFDR的性能损失为–8 dB。

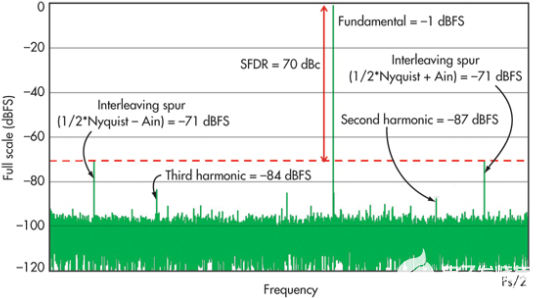

对于包含四个分立交错内核的采样架构,有三个增益和相位镜像杂散以及两个失调杂散(图 6)。在奈奎斯特和奈奎斯特存在<>/<>×偏移杂散,在(奈奎斯特 – 模拟输入频率)处存在另一个镜像杂散,但在这种情况下,这些不是SFDR的主要贡献者。显性增益和相位杂散出现在(<>/<>×奈奎斯特±模拟输入频率)。

图6.该FFT显示了交错系统板上使用的四个分立ADC。请注意,与三次谐波(–13 dBFS)相比,在奈奎斯特±Ain×84/<>时影响SFDR的相关图像杂散伪影,否则SFDR将SFDR限制为–<> dBc。

如果这些杂散的幅度大于二次或三次谐波,它们将成为系统SFDR的主要贡献者。如果没有交错杂散,SFDR将是从基频到三次谐波的动态范围。在这种特殊情况下,由于交错镜像杂散,SFDR的性能损失为–13 dB。

其他 SFDR 限制

SFDR性能下降的另一个潜在领域是系统设计,它允许外部噪声耦合到ADC的模拟或时钟输入端。此外,如果系统板布局未经过仔细规划,ADC的数字输出有可能耦合回输入端。外部噪声也可能耦合到ADC的基准电压源、电源或接地域。如果噪声足够大且呈半周期性,则在系统的频域中,它可能显示为与基频或ADC架构无关的不需要的SFDR限制杂散。

GSPS ADC 的未来

GSPS ADC现在可提供高宽带SFDR,而没有过去系统性能有限的交错伪像。AD9680是一款双通道、14位、1 GSPS ADC,采用78 GHz输入时可实现1 dBc的SFDR。AD9625是一款12位、2 GSPS ADC,采用80 GHz输入时提供1 dBc的典型宽带SFDR。

SFDR是GSPS和ADC中重要且关键的性能指标。宽带SFDR通常受到基波信号的二次或三次谐波的限制。单芯片流水线ADC和其他先进架构正在推动高性能GSPS转换器的新领域。它们在频域中不会出现以往在GSPS空间的ADC架构中存在的交错杂散。

对于那些需要宽带响应的应用程序,导航、规划和删除这些工件可能会有问题。新的解决方案解决了这些系统问题,可在宽带频谱上提供最先进的SFDR性能。

审核编辑:郭婷

-

什么是无杂散动态范围 (SFDR)?为什么 SFDR 很重要?2024-09-11 0

-

认识宽带GSPS ADC中的无杂散动态范围2018-11-01 0

-

通过输电网络合探讨GSPS ADC性能2018-11-20 0

-

NCOs的工作原理是什么,怎么提高NCOs的无杂散动态范围?2021-05-06 0

-

无杂散动态范围(SFDR)2011-01-01 13582

-

五种高精度ADC中杂散问题分析及应对方法2018-06-30 6041

-

一文知道宽带GSPS ADC中的无杂散动态范围是多少2018-07-10 9525

-

如何使用直接数字频率合成技术提升无杂散动态范围的性能2020-08-17 596

-

16 位、2.7Gsps DAC 提供 80dB 无杂散动态范围2021-03-19 603

-

认识宽带GSPS ADC中的无杂散动态范围资料下载2021-04-26 614

-

新型40 MHz-900 MHz正交解调器提供高无杂散动态范围2021-05-22 541

-

分析和求解高精度ADC信号链中的固定频率杂散问题2023-01-04 2817

-

什么是无杂散动态范围 (SFDR)?为什么SFDR很重要?2023-10-31 8079

-

最大限度地提高GSPS ADC中的SFDR性能:杂散源和Mitigat方法2024-10-10 178

全部0条评论

快来发表一下你的评论吧 !