FPGA应用之vivado三种常用IP核的调用

可编程逻辑

描述

今天介绍的是vivado的三种常用IP核:时钟倍频(Clocking Wizard),实时仿真(ILA),ROM调用(Block Memory)。

Clocking Wizard该IP核可以将输入的时钟信号进行倍频,倍数可以大于1,也可以小于1,非常方便。

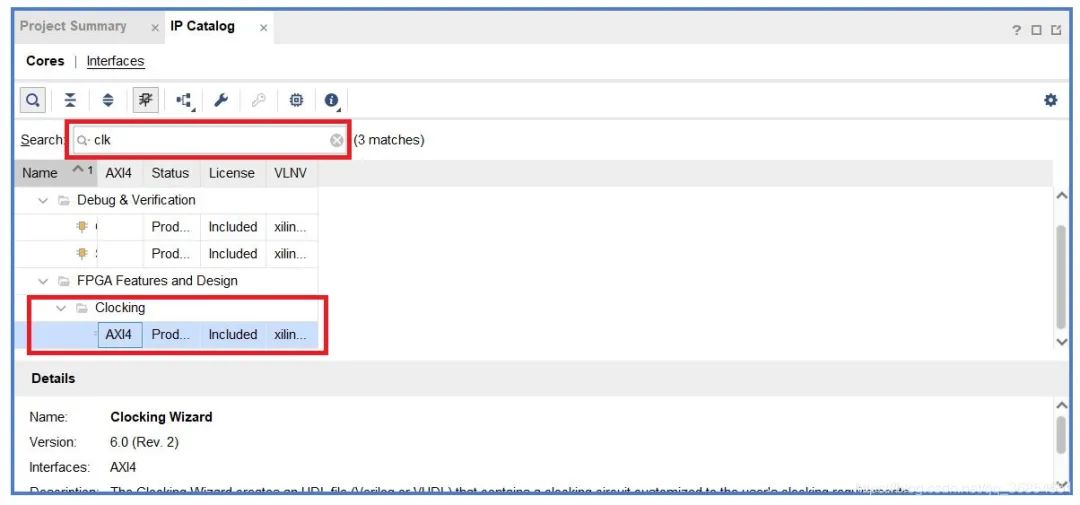

1.打开vivado 找到IP Catelog

在右侧输入栏中输入clk,找到Clocking Wizard

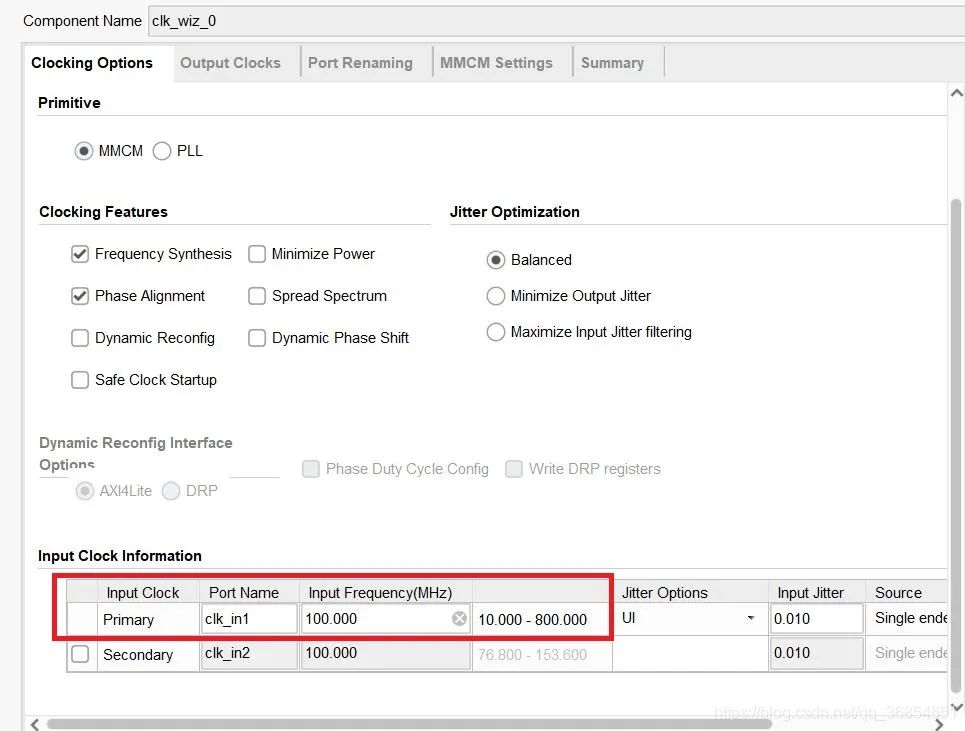

双击该项目打开,根据开发板上晶振频率进行输入时钟配置

配置需要输出的倍频频率

在最下方可选择IP核需要的引脚,我都没用到,因此全取消了(之前有遇到选择reset和lock引脚后IP核不能使用的情况,原因还未弄清楚)。

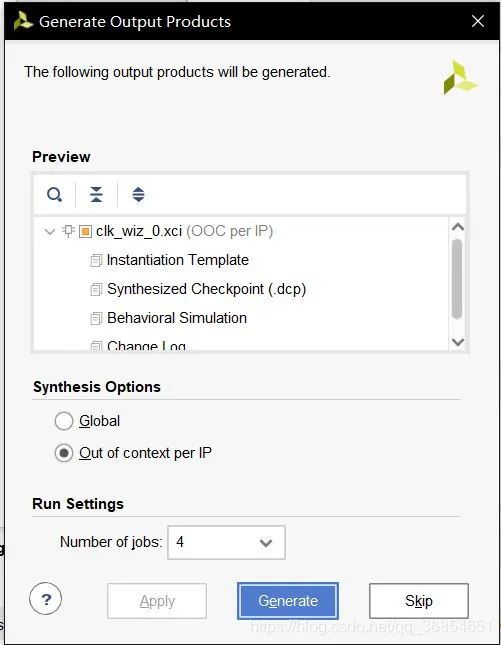

点击OK,并点击Generate,完成Clocking Wizard的配置

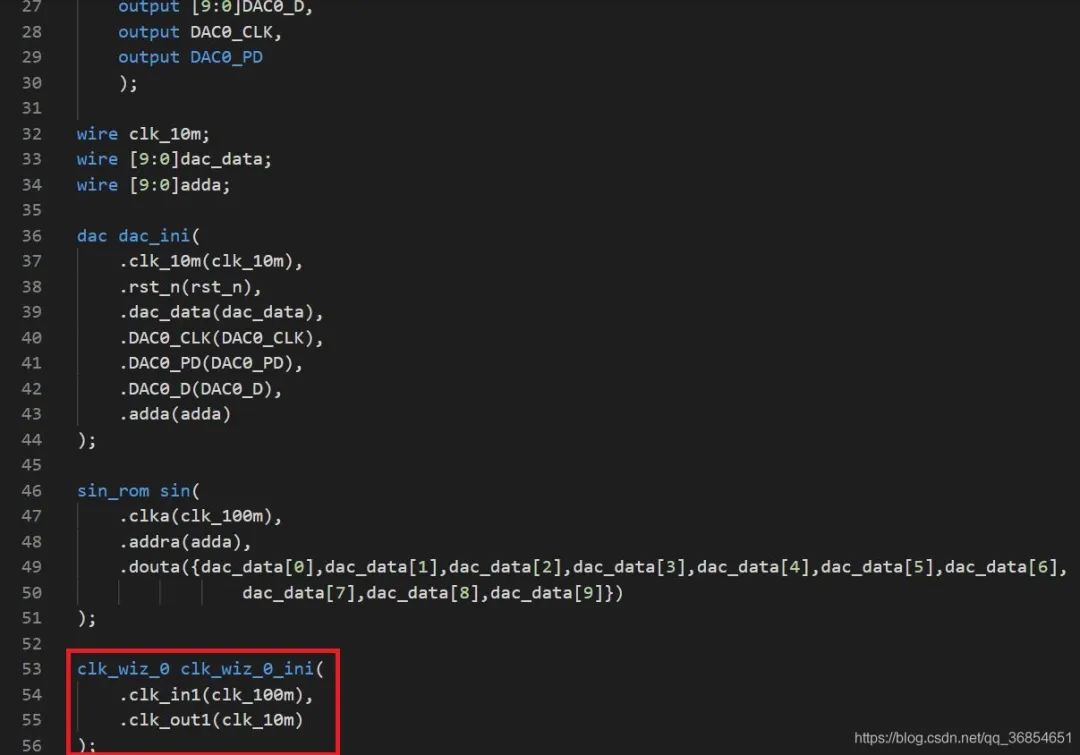

在代码中对IP核进行调用

编写TESTBENCH,仿真结果如下

ILAILA是用于实时仿真的IP核,在你将bit文件烧入芯片后,可在ILA核中看到你想观察的图像和数据。

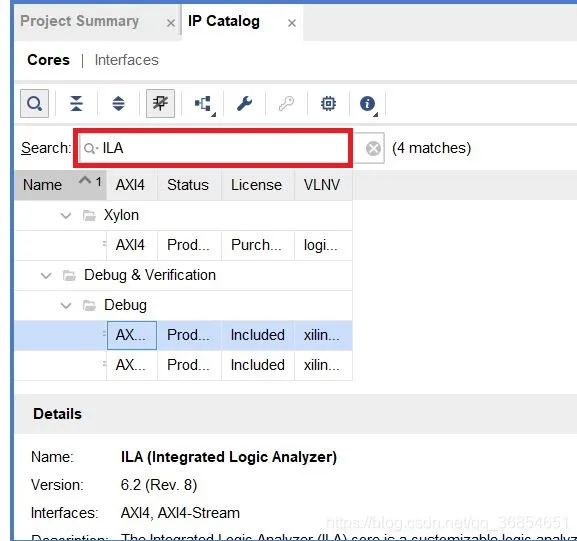

打开IP Catelog,输入ILA

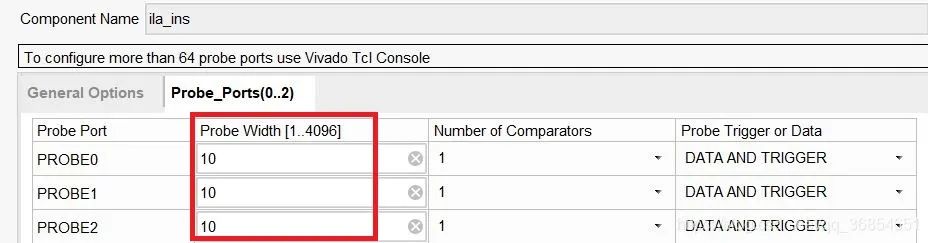

双击打开项目,配置需要观察的端口数,采样的深度

配置观察端口的位数

点击OK,和Generate完成IP核配置

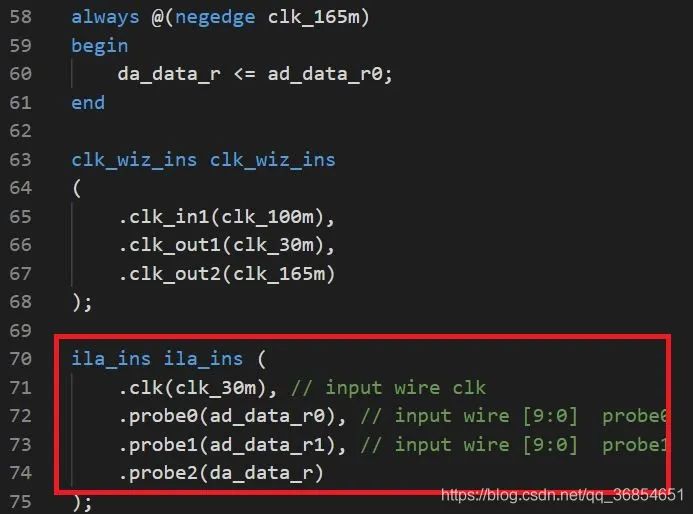

在代码中调用IP核

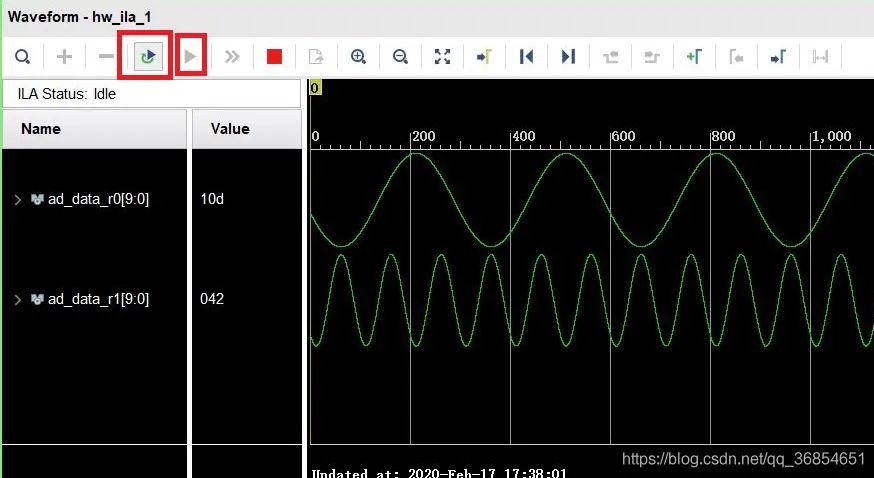

完成工程综合后,下载文件,点击运行和循环,开始观察

Block Memory该IP核调用片内ROM,可以用来储正弦波,三角波等波形。该IP核引用文件的格式为.coe,因此我们需要先使用Matlab生成一个.coe文件。

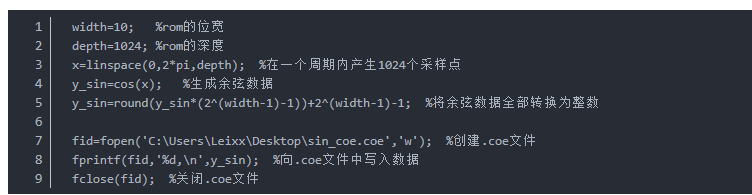

打开matlab,新建一个.m文件,输入以下代码生成一个位宽10位,深度1024的正弦波

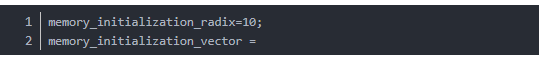

生成文件之后,用notepad++(或UltraEdit)打开,你会看见已经生成好的1024个数据,这时需要在文件的最开始添加下面两句:

radix表示是十进制显示。之后,在文件的最末尾,将最后一个数据后面的逗号改成分号,点击保存。

打开vivado,点击IP Catalog,输入block

双击打开项目,选择Single port ROM

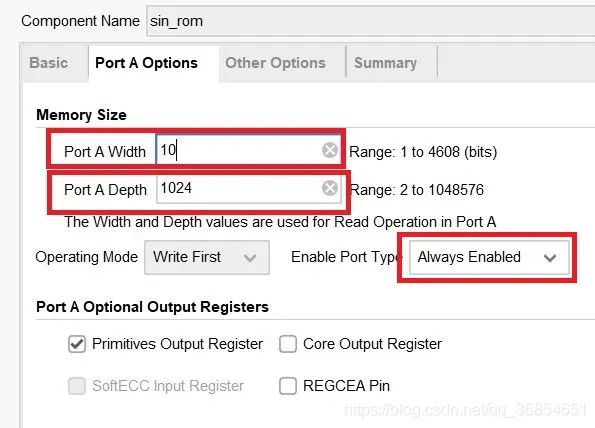

配置要存入的数据位宽和数据深度,我之前生成的是位宽10位,深度1024的数据选择Always Enanbled,让IP核始终处于工作状态

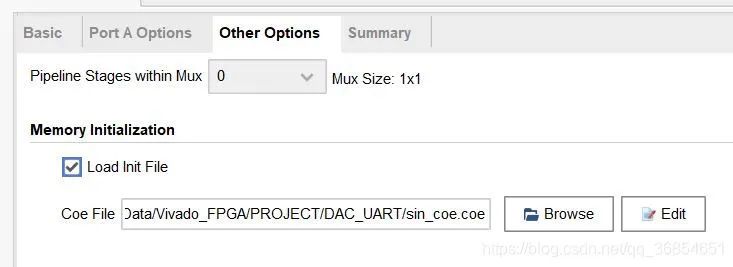

将之前生成好的文件载入IP核

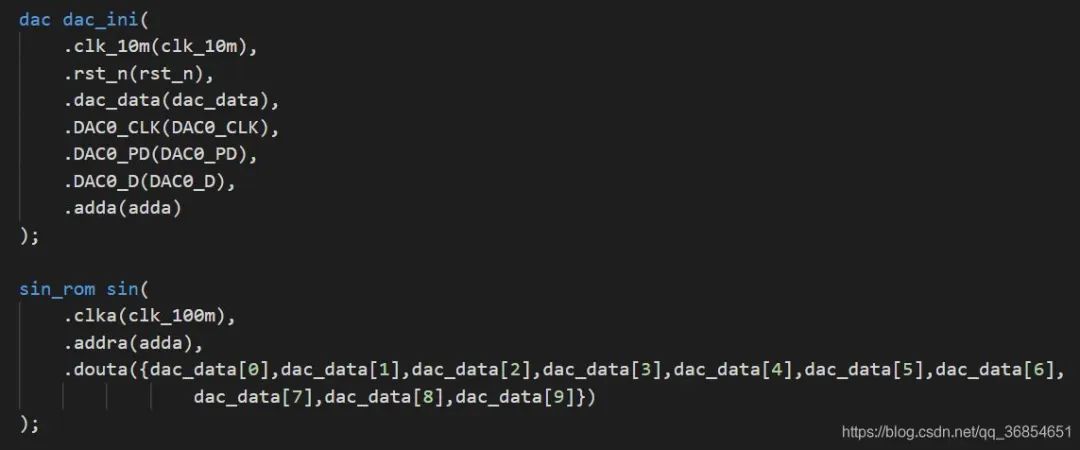

点击OK和Generate,完成IP核配置在代码中调用IP核,我这里DAC是低位在前

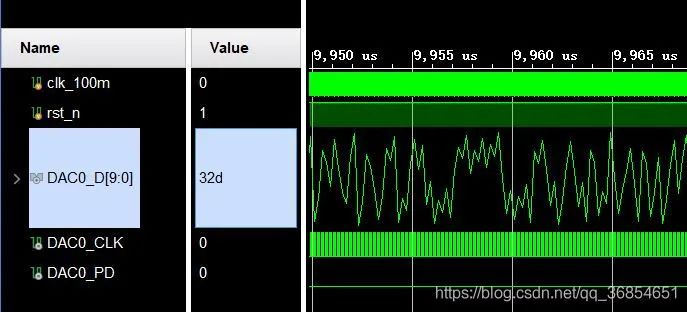

编写好Testbench后,可以在仿真中看到正弦波,我这里因为低位在前,所以波形杂乱。

以上,便是vivado三种常用IP核的调用。编辑:黄飞

-

xilinx FPGA的FFT IP核的调用2016-12-25 0

-

vivado 调用IP核 详细介绍2018-05-15 0

-

详细操作 vivado 调用IP核(附图)2018-05-16 0

-

Vivado IP核锁定的解决办法分享2021-01-08 0

-

vivado有哪几种常用IP核?如何去调用它们2021-07-29 0

-

Xilinx Vivado的使用详细介绍(3):使用IP核2017-02-08 2276

-

了解Vivado中IP核的原理与应用2017-11-15 9145

-

赛灵思Vivado开发套件与IP核的原理作用分析2017-11-28 2005

-

vivado调用IP核详细介绍2018-05-28 37184

-

调用Vivado IP核的方法2018-12-22 4727

-

FPGA实现基于Vivado的BRAM IP核的使用2020-12-29 11674

-

关于Vivado三种常用IP核的调用详细解析2021-04-27 24121

-

一文解析Vivado的三种封装IP的方式2021-08-10 6962

-

VCS独立仿真Vivado IP核的问题补充2023-06-06 1740

全部0条评论

快来发表一下你的评论吧 !