使用隔离式栅极驱动器的设计指南(二):电源、滤波设计与死区时间

描述

点击蓝字 关注我们

本设计指南分为三部分,将讲解如何为电力电子应用中的功率开关器件选用合适的隔离栅极驱动器,并介绍实战经验。上次为大家梳理了隔离式栅极驱动器的介绍和选型指南(详情可点击查看),本文为第二部分,将带大家全面了解使用安森美(onsemi)隔离式栅极驱动器的电源、滤波设计以及死区时间控制。

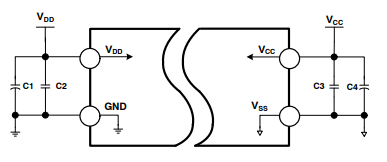

以下是使用隔离式栅极驱动器电源时应注意的一些建议。VDD 和 VCC 的旁路电容对于实现可靠的隔离式栅极驱动器性能至关重要。

建议选择具有适当电压额定值、温度系数和电容容差的低 ESR 和低 ESL 表面贴装多层陶瓷电容 (MLCC)。栅极驱动器的输出偏置电源引脚需要旁路电容,其值至少应为开关器件栅极电容的 10 倍,并且不小于 100 nF;此电容应位于尽可能靠近该器件的地方,以用于解耦。建议使用 2 个电容:一个 100 nF 陶瓷表面贴装电容和一个并联的几微法电容,如图 1 所示。

同样,输入侧的 VDD 和 GND 引脚之间也应放置一个旁路电容。考虑到输入侧的逻辑威廉希尔官方网站 会消耗少量电流,此旁路电容的最小建议值为 100 nF。

图 1. 电源示意图

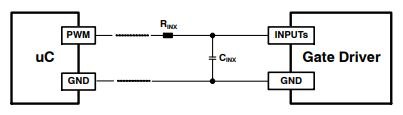

为了获得良好的信号质量和抗扰度,可以在微控制器和栅极驱动器输入之间放置一个输入滤波器 RC 网络,如图 2 所示。

电力电子应用中经常使用的滤波方法有两种:

控制输入端的 RC 滤波器;

具有较短延迟时间的 RC 滤波器与栅极驱动器本身集成的精密滤波器的组合。

RC 值将取决于系统要求的输入频率范围、占空比和时间延迟。

由最大 100 pF 电容和最多 100Ω 电阻构成的小容性滤波器可抑制驱动器输入端的高频噪声。滤波器电容抑制共模噪声。

滤波器电阻有助于保护控制器。串联电阻会限制接地反弹期间流入流出控制器的电流,减弱栅极驱动线的寄生电感(它可能导致振铃),并有助于抑制任何由长输入走线吸收的 EMI。

此 RC 滤波器需要放在尽可能靠近栅极驱动器引脚引线的地方。高压输出威廉希尔官方网站 的共模瞬变噪声可能会干扰低压输入侧。数字控制输入应使用低阻抗信号源以防止出现毛刺或造成意外开关。

图 2. 用于输入信号的 RC 网络示例

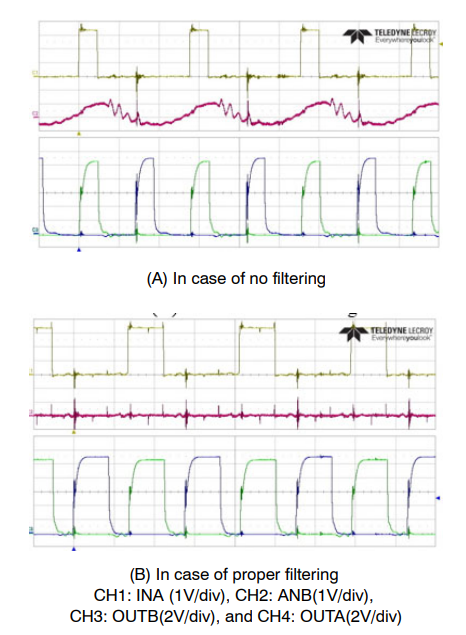

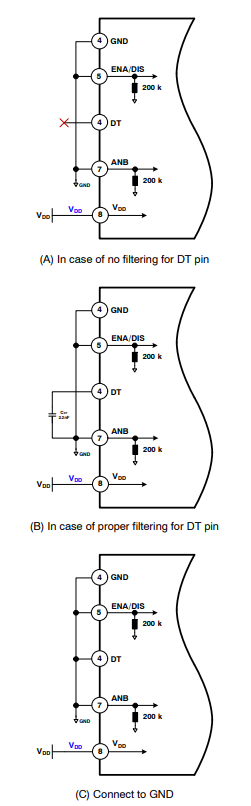

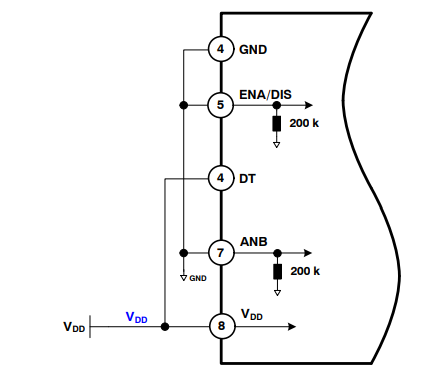

其他输入引脚(如 ANB、DT 和 ENA/DIS)也需要适当滤波,以使系统稳健。由于功率级瞬变电压和电流的电磁干扰 (EMI),输入滤波不当可能导致各种不良影响。

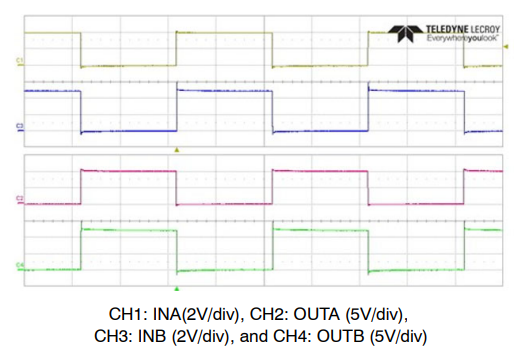

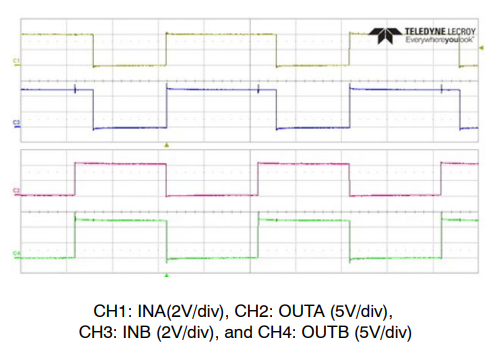

例如,图 3 显示了 ANB 引脚浮空时的工作波形,上方图片没有滤波,下方图片则使用了适当滤波。如实验结果所示,在没有旁路电容的情况下观察到噪声信号,而当靠近此引脚使用 1 nF 以上的旁路电容时,噪声信号消失。

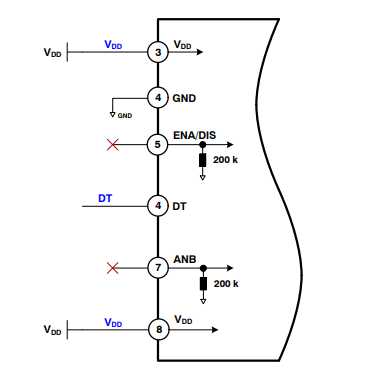

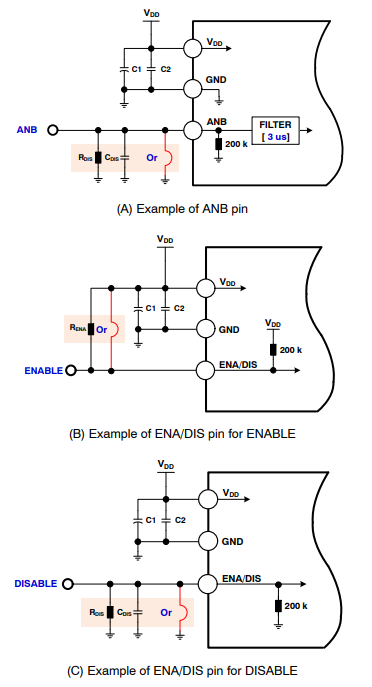

输入信号引脚的阻抗通常为 200 kΩ;禁用 (DISABLE) 时,ANB 和 ENA/DIS 引脚被拉到 GND 引脚,如图 4 所示。但使能 (ENABLE) 时,ENA/DIS 引脚被拉到 VDD 引脚,如图 5 (B) 所示。

图 3. 元件滤波对 ANB 引脚的影响

驱动器引脚的噪声可能会耦合到输入引脚(ANB 和 ENA/DIS)上,导致驱动器对瞬变作出反应,而不是对输入 PWM 信号作出响应。这可能会造成驱动器输入和输出出现不良行为,并且可能会降低系统性能。

此外,如果驱动器的 ANB 和 ENA/DIS 引脚之间的距离较长,那么需要更加注意驱动器的布局和滤波,以避免这种不良行为。

图 4. AND 示例,ENA/DIS 引脚浮空

如果需要 ENA/DIS DISABLE 和 ANB 功能,应使用约 1nF 的低 ESR/ESL 电容,以改善整体系统性能。以下总结了 ENA/DIS 和 ANB 引脚浮空时的注意事项。

ENA/DIS 引脚:如果不使用 ENA/DIS 引脚,应将其直连 VDD 或 GND 引脚以分别实现 ENABLE 或 DISABLE 功能。当使用 ENA/DIS 引脚提供 ENABLE 或 DISABLE 功能时,如果无法将 ENA/DIS 引脚连接到 VDD 或 GND,那么建议将数十 kΩ(如 10 kΩ ~ 47 kΩ)的外部上拉或下拉电阻连接到 VDD 或 GND 引脚,以实现更好的抗扰度,分别如图 5 (B) 和 (C) 所示。

当使用控制器驱动几英寸或更长距离外的 ENA/DIS 引脚时,需要将低 ESR/ESL 的 1 nF 电容放置在引脚附近。

在需要快速禁用响应时间的情况下,应使控制器更靠近驱动器,使用高驱动强度输出,并最大程度地减少栅极驱动环路中的杂散电感。

ANB 引脚:如果不使用 ANB 引脚,应将其直连 GND 引脚,或使用 1 nF 电容。如果无法将 ANB 引脚连接到 GND,那么建议使用数十 kΩ(如 10 kΩ ~ 47 kΩ)的外部下拉电阻,以防止外部干扰导致 ANB 功能意外激活(尽管其内部有 3.3μs 滤波器),如图 5 (A) 所示。

图 5. ANB、ENA/DIS 引脚适当滤波的示例

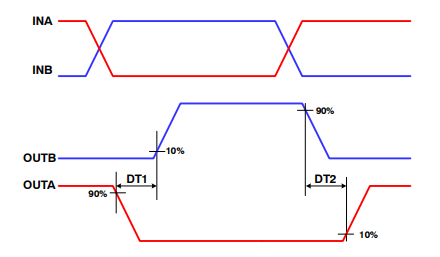

只要两个外部输入信号的死区时间(INA 和 INB 信号之间)比内部设置的死区时间(DT1 和 DT2)短,系统就会自动插入死区时间。否则,如果外部输入信号死区时间大于内部死区时间,则栅极驱动器不会修改死区时间。内部死区时间定义如图 6 所示。

图 6. 内部死区时间定义

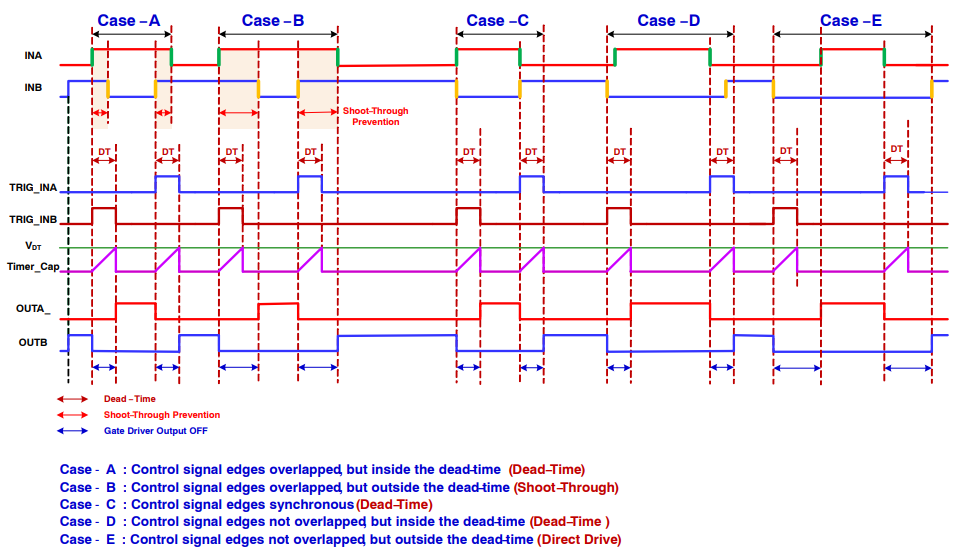

图 7 显示了输入信号同时施加时内部死区时间和防止击穿的定义。

图 7. 内部死区时间定义

图 7. 内部死区时间定义

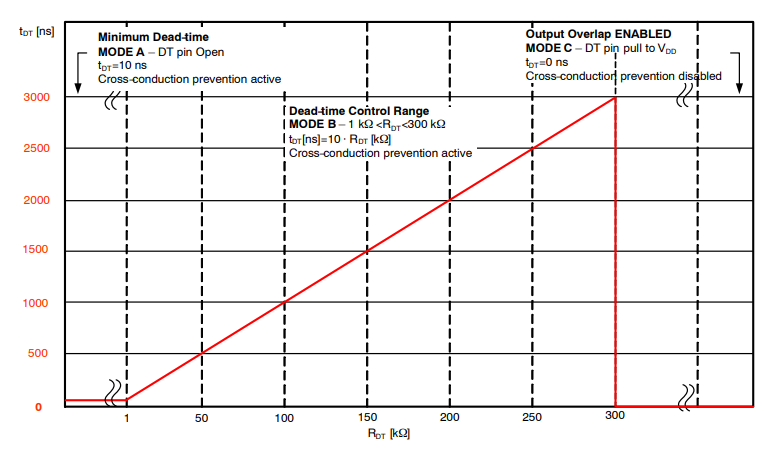

在模式 A 下,当 DT 引脚开路时,最小死区时间 (tDTMIN) 典型值为 10 ns,不允许驱动器两个输出(OUTA 和 OUTB)之间交叉导通。在模式 B下,当 DT 引脚电阻在 1 k 和 300 k 之间时,外部电阻 (RDT) 控制死区时间。

当激活死区时间 (DT) 控制模式时,不允许重叠。

两路输出之间的死区时间 (DT) 根据下式设置:DT(单位为 ns)= 10 × RDT(单位为 kΩ)。

在模式 C下,当 DT 引脚被拉至 VDD 时,允许两个输出重叠,如图 8 所示。

图 8. 死区时间模式控制的时序图

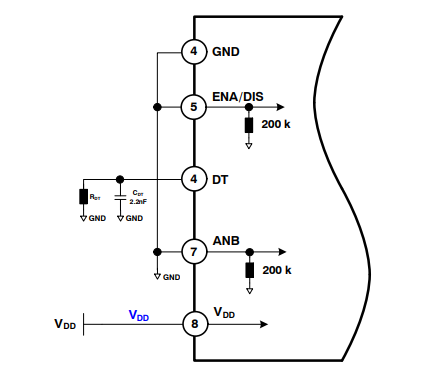

当 DT 引脚浮空时,建议将 DT 引脚直连 GND 引脚,或使用 2.2 nF 电容,分别如图 9 的中间和下方图形所示。

图 9. ANB、ENA/DIS 引脚适当滤波的示例

如图 10 所示,当 DT 引脚浮空时,最小死区时间 (tDTMIN) 典型值为 10 ns,不允许驱动器两个输出(OUTA 和 OUTB)之间交叉导通。

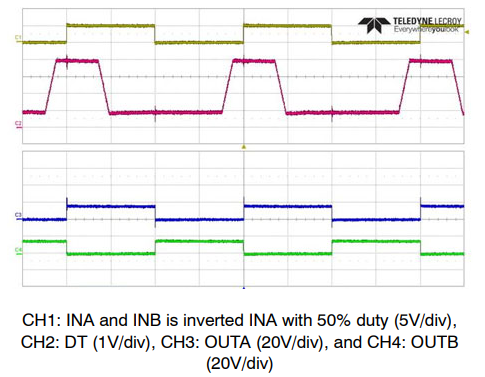

图 10. DT 引脚浮空时的实验波形

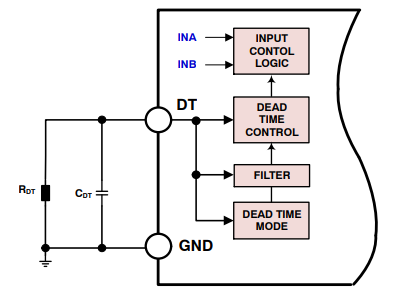

如果通过死区时间控制电阻对死区时间进行编程,应并联放置一个值大于 2.2nF 的电容,以提高快速开关瞬变期间的抗扰度,如图 11 所示。

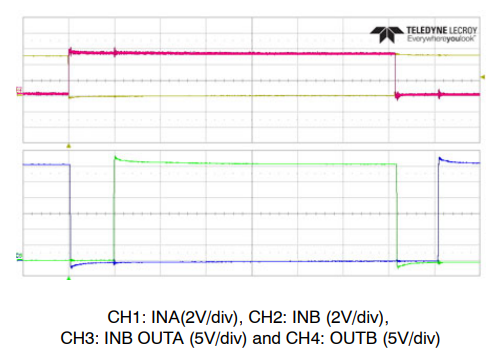

当 DT 引脚电阻在 1 kΩ 和 300 kΩ 之间时,外部电阻 (RDT) 控制死区时间。图 12 显示了 DT 引脚具有 100 kΩ 电阻时的实验结果。

图 11. 死区时间引脚适当滤波的示例

图 12. DT 引脚具有 100 kΩ 电阻时的实验波形

如果无需死区时间,应将死区时间引脚连接到 VDD 以停用 DT 威廉希尔官方网站 ,如图 13 所示,实验结果如图 14 所示。

图 13. 将 DT 引脚连接到 VDD 引脚以停用 DT 威廉希尔官方网站 的示例

图 14. DT 引脚短接 VDD 时的实验波形

死区时间控制功能根据 DT 引脚电压提供三种工作模式。

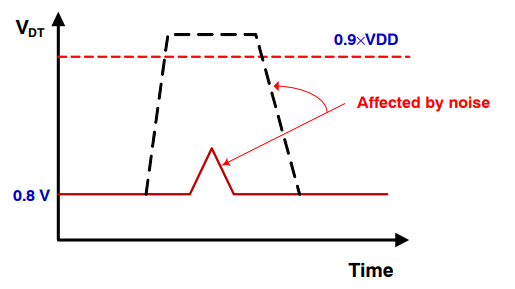

当 DT 引脚浮空时,在浪涌测试期间(如雷击浪涌)DT 引脚上可能有异常噪声。尽管 DT 引脚内部对于开路和短路检测分别有 3μs 和 2μs 的滤波时间,但如果 DT 引脚电压受噪声信号影响而超过额定电压电平,死区时间控制模式仍会变为模式 C,因为死区时间控制模式变更取决于 DT 引脚电压。

例如,如果 DT 引脚电压低于 0.9 × VDD,则当 DT 引脚浮空时,死区时间具有最小值(典型值 10 ns),DT 引脚的稳态电压约为 0.8 V。

如果噪声导致 DT 引脚电压超过 0.9 × VDD 且持续 3μs 以上,死区时间控制模式会被禁用,这意味着两个通道之间没有死区时间,如图 15 所示。

图 15. DT 引脚浮空时的异常波形

因此,建议为 RDT 增加一个 2.2nF 或以上的陶瓷电容 (CDT),并使其靠近芯片,以实现更好的抗扰度和两个通道之间更好的死区时间匹配,如图 16 所示。

主要考量是通过 RDT 的电流用于设置死区时间,此电流随着 RDT 值的增大而减小。

图 16. 死区时间的更详细框图

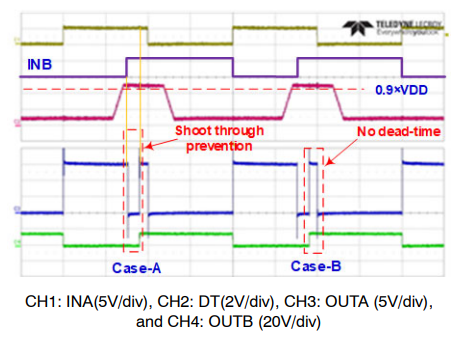

测试结果显示,对于 5 V 情况的 VDD,当 DT 引脚浮空且外部施加的电压低于 0.9 × VDD 时,死区时间控制模式不变,即仍为模式 A,如图 17 所示。

图 17. DT 引脚浮空且外部施加的电压低于 0.9 × VDD 时的实验波形

但是,对于 5 V 情况的 VDD,当 DT 引脚浮空且外部施加的电压高于 0.9 × VDD 并持续 3μs 以上时,死区时间模式从模式 A 变为模式 C,例如图 18 中的情况 B 所示。如情况 A 所示,针对 DT 引脚开路检测,其内部有 3μs 滤波时间,因此死区时间控制模式并未改变,防止击穿功能仍在运行。

第三部分将于下周发布,敬请期待!

意犹未尽?

扫描下方二维码填写信息

获取英文原版完整应用笔记

点个星标,茫茫人海也能一眼看到我

原文标题:使用隔离式栅极驱动器的设计指南(二):电源、滤波设计与死区时间

文章出处:【微信公众号:安森美】欢迎添加关注!文章转载请注明出处。

- 相关推荐

- 安森美

-

实现隔离式半桥栅极驱动器的设计途径2018-09-26 0

-

实现隔离式半桥栅极驱动器的设计基础2018-10-16 0

-

隔离式栅极驱动器揭秘2018-10-25 0

-

隔离式栅极驱动器的揭秘2018-11-01 0

-

采用MP188XX 隔离式栅极驱动器系列构建电源系统2022-09-30 0

-

ADuM4221/ADuM4221-1/ADuM4221-2:隔离式半桥栅极驱动器,死区时间可调,4 A输出数据表2021-03-22 844

-

UG-1857:评估ADuM4221-1隔离式半桥式栅极驱动器,死区时间可调,4 A输出2021-03-22 750

-

使用隔离式栅极驱动器的实用设计指南2022-11-14 472

-

使用隔离式栅极驱动器的设计指南(三):设计要点和PCB布局指南2023-02-11 1963

-

用于EiceDRIVER™隔离栅极驱动器的电源评估板2022-02-20 1106

-

使用隔离式栅极驱动器的设计指南(一)2023-11-28 668

-

隔离式栅极驱动器的影响2024-07-13 147

-

光兼容隔离式栅极驱动器的输入电阻选择指南2024-10-14 71

-

电隔离栅极驱动器选型指南2024-11-11 320

全部0条评论

快来发表一下你的评论吧 !