RTL和门级建模

描述

数字硬件建模SystemVerilog(一)-RTL和门级建模

接下来系列文章会有很多在Verilog中知识点有被提及,关于这两者关系,请查看《谈谈Verilog和SystemVerilog简史,FPGA设计是否需要学习SystemVerilog》。

本文定义了通常用于描述使用SystemVerilog对硬件功能进行建模的详细级别的术语。

抽象

SystemVerilog能够在许多不同的细节级别(称为“抽象级别”)对数字逻辑进行建模。抽象意味着缺乏细节。数字模型越抽象,它所代表的硬件的细节就越少。

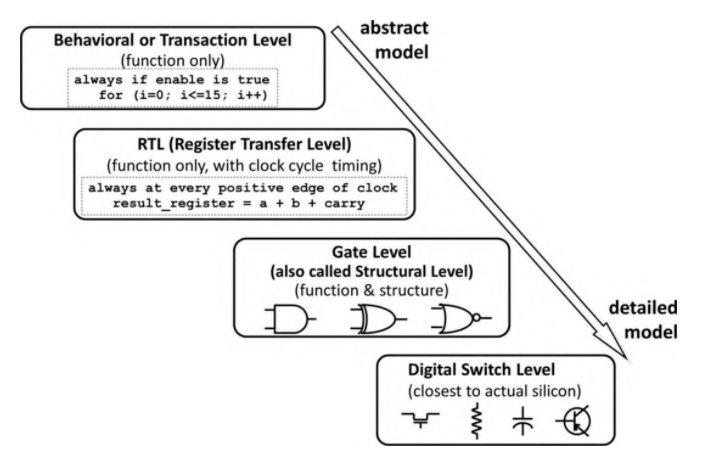

图1-3显示了SystemVerilog中可用的建模抽象的主要级别的详细模型

图1-3:SystemVerilog建模抽象级别

门级建模

SystemVerilog支持使用门级原语对数字逻辑进行建模。数字逻辑门是一个非常接近硅(silicon)实现的详细模型。

SystemVerilog提供了几个内置的门级原语,并允许工程师定义其他原语,这些原语是指用户定义的原语(UDP)。SystemVerilog中的内置原语列在表1-1中:

表1-1:SystemVerilog门级原语

| 原语 | 描述 |

|---|---|

| 与and | 具有2个或更多输入和1输出的与门 |

| 与非门nand | 具有2个或更多输入和1输出的与非门 |

| 或or | 具有2个或更多输入和1个输出的或门 |

| 或非门nor | 具有2个或更多输入和1输出的或非门 |

| 异或门xor | 具有2个或更多输入和1输出的异或门 |

| 异或非门是xnor | 具有2个或更多输入和1输出的异或非门 |

| 缓冲器buf | 具有1个输入和1或更多输出的缓冲门 |

| 反向门not | 具有1输入和1或更多输出的反向门 |

| buffif0 | 三态缓冲门,带“1输入*1输出”和1个激活低启用 |

| bufif1 | 具有1输入、1输出和1激活高启用的三态缓冲门 |

| notif0 | 带1输入、1输出和1低激活的三态反向缓冲门 |

| notif1 | 带1输入、1输出和1高激活的三态反向缓冲门 |

SystemVerilog还为ASIC和FPGA库开发人员提供了通过定义用户定义原语(UDP)添加到内置原语集的方法。UDP以表格格式定义,表格中的每一行列出一组输入值和结果输出值。组合逻辑和顺序逻辑(如触发器)原语都可以定义。

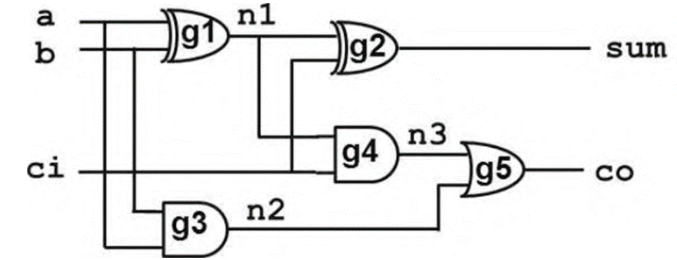

图1-4显示了带进位的1位加法器的门级威廉希尔官方网站 。示例1-1显示了“使用原语对威廉希尔官方网站 建模的SystemVerilog代码”。

图1-4:带进位的1位加法器,用逻辑门表示示例1-1;带进位的1位加法器的SystemVerilog门级模型

`begin_keywords

"1800-2012"

module gate_adder

(input wire a, b, ci,

output wire sum, co

);

timeunit 1ns; timeprecision 100ps;

wire n1, n2, n3;

xor g1 (n1, a, b);

xor

#1.3 g2 (sum, n1, ci);

and g3 (n2, a, b);

and g4 (n3, n1, ci);

or

#(1.5,1.8) g5 (co, n2, n3);

endmodule: gate_adder

`end_keywords

门级原语的语法非常简单:

<>

type

> 〈instance name> (, );

许多门级原语可以具有可变数量的输入。例如,and原语可以表示2输入、3输入或4输入与门,如下所示:

and i1{o1,a,b);//2-输入与门

and i2(o2,a,b,c};//3-输入与门

and i3{o3,a,b,c,d);//4-输入与门

原语的实例名称虽然是可选的,但它是良好的代码注释,它使维护代码和将SystemVerilog源代码与示意图或设计的其他表示形式联系起来变得容易。实例名称是用户定义的,可以是任何合法的SystemVerilog名称。

门级原语可以用传播延迟来建模。如果未指定延迟,则门输入上的更改将立即反映在门输出上。延迟是一个表达式,可以是一个简单的值,如示例1-1中的实例g2,也可以是一个更复杂的表达式,如实例g5。上述代码中的栅极g2的传播延迟为13ns,这意味着当其中一个栅极输入上发生转换时,在栅极输出sum改变之前,这个时间是13ns。门g5将传播延迟分为不同的延迟,用于输出上的上升和下降跃迁。如果co值从0转换为l,延迟为1ns。如果co正在从1转换为0,更改延迟为1.8ns。

门级模型能够以高精度表示实际硅的传播延迟。逻辑门的功能反映了将在硅中使用的晶体管组合的功能,并且门延迟可以反映通过这些晶体管的传播延迟。ASIC和FPGA供应商使用这种精度对特定设备的详细行为进行建模。

门级模型通常由软件工具或专门从事库开发的工程师生成。在RTL级别设计的设计工程师很少(如果有的话)使用门级原语建模。相反,RTL设计者使用门级模型的网表,其中网表是通过合成RTL模型生成的。网表级模型由目标ASIC或FPGA设备的供应商提供。关于门级建模的内容比本文中介绍的要多得多。

开关级建模。SystemVerilog还可以使用开关原语(如pmos、nmos和cmos)、电阻开关原语(如rpmos、cnmos和rcmos)和电容网络在晶体管级对数字威廉希尔官方网站

建模。这种级别的建模可以很好地表示实际的硅实现。然而,由于这些结构只能仿真数字行为,因此很少使用。晶体管、电阻器和电容器都是仿真器件。数字仿真不能准确反映晶体管的行为。开关级建模通常不在SystemVerilog的FPGA设计流程中使用。

RTL模型

一个更抽象的建模级别——也是系列文章的重点——是寄存器传输级别(Register Transfer Levels),或RTL。此级别的建模使用编程语句和运算符表示数字功能。RTL模型是功能模型,不包含有关如何在硅中实现该功能的详细信息。由于这种抽象,复杂的数字功能可以比在详细的门级更快速、更简洁地建模。RTL模型的仿真速度也大大快于门级和开关级模型,这使得验证更大、更复杂的设计成为可能。SystemVerilog为RTL建模提供了两种主要结构:连续赋值(continuous assignments)和always程序块。

连续赋值以assign关键字开始,可以表示简单的组合逻辑。前面的示例1-1说明了1-bit加法器的门级模型。示例1-2显示了如何通过使用连续赋值在更抽象的层次上建模相同的1位加法器功能:

`begin_keywords

"1800-2012"

module rtl_adder

(input logic a, b, ci,

output logic sum, co

);

timeunit 1ns/1ns;

assign {co,sum} = a + b + ci;

endmodule: rtl_adder

`end_keywords

示例1-2:带进位的1位加法器的SystemVerilog RTL模型

RTL建模的一个优点是代码更易于自文档化(self-documenting)。查看示例1-1中的门级模型并识别模型所代表的内容可能很困难,尤其是在没有注释和有意义的名称的情况下。但是,查看示例1-2中RTL模型中的代码并认识到该功能是一个加法器要容易得多。

RTL建模的另一个强大优势是能够处理矢量和数据包。矢量是一个大于一位宽的信号。开关级和门级建模的操作一1位宽的信号,在SystemVerilog中称为标量信号。要对32位加法器进行建模,需要对每个位上运行的开关或门进行建模,这与实际硅中的操作相同。上述示例1-2中的连续赋值语句可以通过改变信号的声明,对任意大小的加法器进行建模。

更复杂的功能可以使用程序块建模。程序块封装了一行或多行编程语句,以及有关何时执行这些语句的信息。RTL级别使用四种类型的always过程:always、always_comb、always_ff和always_latch。

以下示例简明地表示具有寄存器输出的32位加法器/减法器:

`begin_keywords

"1800-2012"

module rtl_adder_subtracter

(input logic clk, // 1-bit scalar input

input logic mode, // 1-bit scalar input

input logic [31:0] a, b, // 32-bit vector inputs

output logic [31:0] sum // 32-bit vector output

);

timeunit 1ns/1ns;

always_ff @(posedge clk) begin

if

(mode == 0) sum <= a + b;

else

sum <= a - b;

end

endmodule: rtl_adder_subtracter

`end_keywords

示例1-3:32位加法器/减法器的SystemVerilog RTL模型

在一个典型的仿真和综合设计流程中,工程师们将花费大部分时间在RTL级别建模和验证RTL功能。

行为级和事务级建模

SystemVerilog过程块可用于在比RTL更高的抽象级别上建模,该抽象通常被称为行为模型(也称为总线功能或算法模型)。行为模型可能看起来与RTL模型非常相似,因为RTL和行为模型都是程序块。行为模型在两个方面与RTL有所不同。

高级抽象是事务级建模。事务模型通常用于验证代码中,并且通常使用SystemVerilog的面向对象编程结构进行建模。

RTL综合编译器无法综合抽象的行为和事务级别,本系列中也没有讨论.

•RTL模型必须遵守严格的语言限制,才能由RTL综合编译器进行合成。行为模型可以使用完整的SystemVerilog语言。

•RTL程序块在单个时钟周期内执行其编程语句,如果是组合逻辑,则在零周期内执行。行为模型过程块可以使用任意数量的时钟周期来执行其语句。

-

关于RTL仿真和门级仿真求助~2016-08-06 0

-

关于功能验证、时序验证、形式验证、时序建模的论文2011-12-07 0

-

RTL级代码和仿真代码的区别2012-07-21 0

-

RTL级仿真与门级仿真2015-08-08 0

-

RTL级的功能仿真结果和系统级建模仿真的结果比较2015-12-08 0

-

【小白入门笔记】 小脚丫实现38译码器——模块建模和门级建模初探2017-09-16 0

-

【FPGA学习】Verilog HDL 语言的描述语句之门级建模形式2018-09-20 0

-

什么是IP开发及FPGA建模?2019-08-01 0

-

Verilog HDL为门级威廉希尔官方网站 建模的能力详解2021-03-05 6481

-

RTL级设计的基本要素和步骤是什么2023-01-17 10364

-

FPGA基础设计之使用逻辑门和连续赋值对威廉希尔官方网站 建模2023-02-08 587

-

基于Verilog的开关级建模2023-03-30 1545

-

X态如何通过RTL级和门级仿真模型中的逻辑进行传播呢?2023-04-20 2070

-

ESL事务级建模语言简介2023-11-02 722

全部0条评论

快来发表一下你的评论吧 !