高端SerDes集成到FPGA中的挑战

描述

在过去的几十年里,电子通信行业一直是 FPGA 市场增长背后的重要推动力,并将继续保持下去。这背后的一个主要原因是 FPGA 中内置了许多不同的高速接口,以支持各种通信标准/协议。实现这些标准所涉及的底层输入-输出 PHY 技术是串行器-解串器 (SerDes) 技术。FPGA 作为一项技术从一开始就很复杂且具有挑战性,甚至在考虑高速接口之前也是如此。SerDes PHY 设计本身就很复杂且具有挑战性。当这两者结合在一起时,实施会变得更加棘手,这通常是将最先进的 SerDes 设计整合到 FPGA 中的原因。但如果现状可以改变呢?这是 Alphawave IP 和 Achronix 之间合作努力的目标,其结果于 10 月在台积电 OIP william hill官网 上公布。

将高端 SerDes 集成到 FPGA 中的挑战

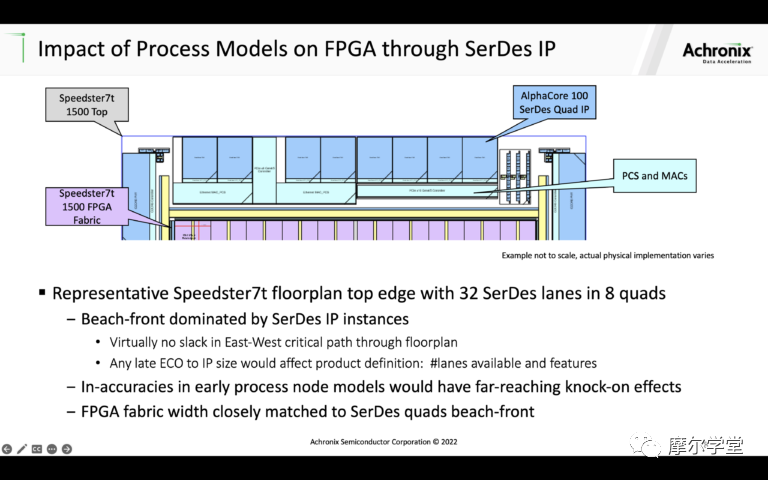

SerDes 和 FPGA 结构之间的相互依赖性可能会给集成芯片带来布局规划挑战。除了布局挑战之外,即使结构和 SerDes 之间金属堆叠选择的微小差异也可能对这些组件中的任何一个的功率、性能和面积 (PPA) 产生不利影响。

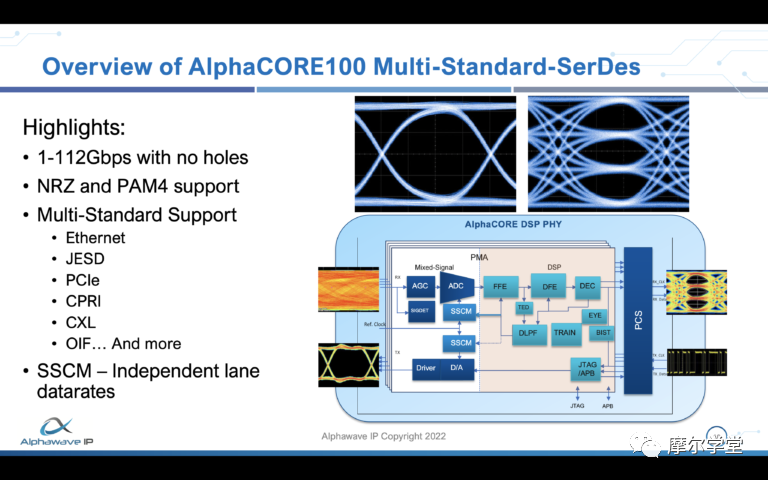

FPGA 必须支持大量线路速率和协议以及具有不同电气通道要求的协议变体。线路速率范围从 1Gbps 到 112Gbps,使用 NRZ 或 PAM4 信号方案来提供速度性能。这种组合要求给用于模拟的建模带来了沉重的负担。每个线路速率/协议组合都需要根据高精度模型在硅前和硅后进行验证。

成功集成的要求

无论是 SerDes 还是 FPGA 结构,都会进行架构增强,这将影响 SerDes 与 FPGA 结构的集成。为避免在集成时出现意外,需要尽早讨论架构并达成一致,以便可以开发适当的模拟模型进行验证。过于乐观的模型会迫使架构发生根本变化,而悲观的模型会提供 PPA 无竞争力的解决方案。这两种情况都不可取。

SerDes IP 供应商和 FPGA 集成商之间的密切合作需要尽早开发准确的模型。还需要密切合作以确保最佳布局规划、电源规划、凸点图规划、时序等。

Alphawave IP 和 Achronix 合作的范围

Achronix 的高端 FPGA 支持 1GbE 到 400GbE、PCIe Gen5 等多标准协议,包括支持非标准速度(例如 82Gbps)的自定义协议。SerDes 112 Gbps 使用与 56Gbps SerDes 不同的架构,并使用 PAM4 信令方案。该设计使用数字 ADC,并且是围绕基于 DSP 的架构构建的。

合作的目标是实现 Alphawave IP 的 AlphaCORE100 多标准 SerDes 与 Achronix 的 Speedster7t FPGA 结构的成功集成。

测试芯片

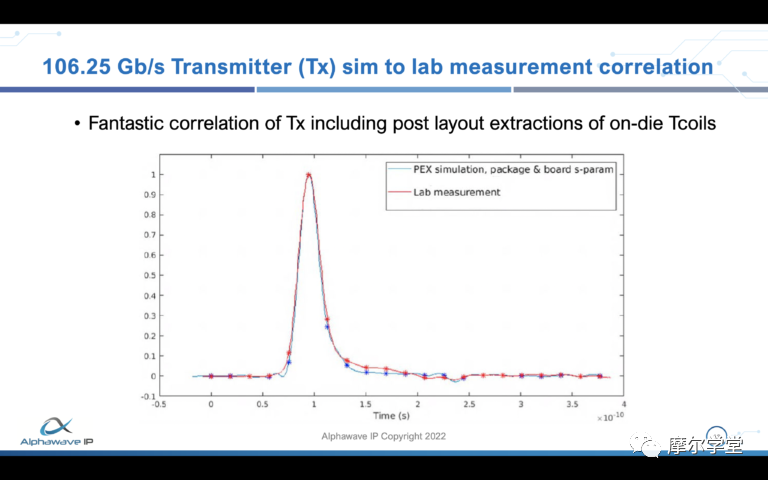

构建了一个测试芯片来验证早期的 sim 模型。测试芯片采用 TSMC 的 N7 工艺实现,包括四个数据通道、完整的 AFE、数字 PLL 和 DLL、BIST 以及用于表征的附加测试威廉希尔官方网站 。

成功的结果

如下图所示,基于通过协作开发的早期模型的仿真结果与实验室中的测试芯片测量结果非常相关。高精度模型使 Achronix 能够使用 Alphawave IP 的 AlphaCore100 SerDes IP 生产一次成功的 Speedster7t FPGA,以支持 PCIe Gen5x16 和 Gen5x8 以及 400GbE。

完整仿真的结果也与实验室针对各种信道损耗条件的 BER 测量结果密切相关。

审核编辑:汤梓红

-

中高端FPGA如何选择2024-04-24 0

-

ASP4644在FPGA SERDES供电中的应用2024-08-16 0

-

FPGA SERDES接口威廉希尔官方网站 怎么实现?2019-10-23 0

-

请问超高速SerDes在芯片设计中的挑战是什么?2021-06-17 0

-

SerDes是怎么工作的2021-07-28 0

-

SERDES在数字系统中高效时钟设计方案2012-02-16 5970

-

教你如何进行Xilinx SerDes调试2013-03-15 10787

-

基于京微雅格低功耗FPGA的8b/10b SERDES的接口设计2015-02-02 2359

-

基于FPGA芯片的SERDES接口威廉希尔官方网站 设计2019-05-24 4864

-

FPGA与IOT的快速发展 SerDes接口技术大显身手2020-07-28 1319

-

Xilinx 7 系列FPGA中的Serdes总结2020-12-31 1473

-

SerDes的基本结构2022-10-31 1892

-

浅析高端SerDes集成到FPGA中的挑战2023-02-22 1242

-

SerDes是怎么设计的?(一)2023-10-16 1484

全部0条评论

快来发表一下你的评论吧 !