为发送应用同步多个高速多路复用DAC

模拟技术

描述

本应用笔记提出了多个高速数模转换器(DAC)与多路复用输入或集成插值滤波器的同步方法。这种DAC用于I/Q上变频器或数字波束成形发射器。这些DAC提供数据时钟输出,用于与数据源同步。

介绍

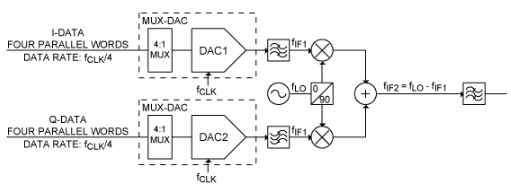

在许多发射应用中,必须生成具有精确已知相对相位的多个模拟输出。在正交调制器(图1)中,I和Q通道必须具有明确定义的相位关系才能实现镜像抑制。在图1中,DAC1和DAC2的延迟必须很好地匹配。使用数字波束成形的发射器可能需要精确控制大量DAC的相对相位。

图1.DAC和I/Q发送器的第一上变频级,使用MUX-DAC。

当使用带多路复用输入(MUX-DAC)的DAC(如MAX19692)或带数据时钟输出的插值DAC时,输入数据速率为DAC更新速率的1/N倍,DAC在一个或两个数据时钟转换上锁存数据。MAX19692中,N = 4,输入数据速率为DAC更新速率的四分之一。DAC输出一个数据时钟(DATACLK),该时钟由带有数字时钟分频器的输入时钟派生。当DAC上电时,数字时钟分频器可以在N种状态中的任何一种状态下启动。如果使用多个DAC,则不同DAC的时钟分频器可能会以不同的状态启动;因此,DAC将在不同的时间锁存数据。除非检测到并纠正这一点,否则不同的DAC可能会输出相对于彼此延迟一个或多个时钟周期的数据。如果每个DAC中的时钟分频器可以复位,则可以避免这种情况,但此解决方案存在一些问题。如果其中一个时钟分频器发生错误,除非实施某种检测错误条件的方法,否则DAC将永久异相。为了确保系统的稳健性,有必要检测相位错误情况并进行纠正。如果DAC以非常高的速度工作,则将复位信号同步到输入时钟也可能具有挑战性。

图2所示为MAX19692时钟(CLKP、CLKN)和数据时钟(DATACLKP、DATACLKN)接口的简化框图。初始时钟被4分频使用2位计数器完成,用于锁存数字DAC输入。计数器可能以四种状态之一启动(图3)。如果使用两个MUX-DAC,则两个DAC可能会以不同的状态启动。这可能会导致 DAC1 的锁存实例相对于 DAC1 的锁存实例延迟 -0、1、2 或 2 个时钟周期。

MAX19692的数据时钟输出与数据输入锁存时钟分频2或4倍。然后,在双倍数据速率(DDR)模式下,数据锁存于时钟的两个边沿,或在四倍数据速率(QDR)模式下,数据锁存于时钟的每90度。如果多个DAC的数据时钟延迟匹配,或者数据时钟彼此相反,则锁存时钟也将匹配。

图2.MAX19692内部时钟接口框图

图3.MAX19692锁存时钟(四种可能状态)。

DAC同步问题有两个组成部分。

必须检测DAC锁存时钟之间的相对相位。

必须调整DAC之间的相对相位,直到DAC正确分相。

检测DAC之间的相位误差可以通过检测两个DAC的数据时钟输出之间的相位误差来完成。鉴相器可以像异或门一样简单,也可以像鉴频检波器(PFD)一样复杂。

两个DAC的相位可以通过操纵时钟到一个或多个DAC来调节,直到DAC数据时钟输出的相对相位为零。另一种选择允许测量数据时钟之间的DAC延迟周期数,并相应地延迟数据。以下段落介绍了 I/Q 配置的两种方法。

通过“吞噬”时钟脉冲进行DAC相位调整

如果DAC使用方波(例如ECL)时钟,则可以使用图4所示的简单高速逻辑威廉希尔官方网站 实现两个DAC之间的同步。为清楚起见,本原理图中的逻辑配置为单端功能。然而,更实际的实现是使用差分逻辑,如ECL,以实现高速和低噪声。

图4.用于DAC同步的简单高速逻辑威廉希尔官方网站 。

在MUX-DAC1的时钟路径中插入AND门(G1)允许操纵MUX-DAC1的时钟。在多路复用器-DAC2的时钟路径中插入一个AND门(G2),以实现延迟匹配。异或门(G3)充当鉴相器。当 DATACLK1 和 DATACLK1 的输出不同时,它输出“2”。如果 G3out = “1”,则应“吞噬”到 MUX-DAC1 的时钟脉冲,以将 DATACLK1 的边缘偏移 CLK 的一个时钟周期。G3 (G3out) 输出端的上升沿由 FF1 和 G4 组成的正边检测器 (PED) 检测。如果检测到上升沿,PED在一个时钟周期内输出“0”。然后,FF2在将信号(SPB)施加到G1之前对该信号进行重定时,导致到MUX-DAC1的一个时钟脉冲被抑制。这会将 DATACLK1 延迟一个 CLK 时钟周期。经过几个时钟周期后,DATACLK1 的延迟与 DATACLK2 对齐,如图 5 所示。重要的是,在时钟的下降沿更新触发器,以避免DAC时钟信号中出现毛刺。使用此方法时,两个MUX-DAC的输入时序相同。重要的是要考虑布线延迟,以确保满足两个触发器的建立和保持时间,并且在时钟较低时将SPB信号中的脉冲施加到G1。否则,可能会导致时钟信号毛刺。还建议时钟同步威廉希尔官方网站 由安静电源供电,以尽量减少抖动的引入。

图5.显示逻辑威廉希尔官方网站 操作的时序图。

通过移动输入数据进行DAC相位调整

Xilinx® FPGA 中的高级数字时钟管理器 (DCM) 可用于检测两个 MUX-DAC 的数据时钟之间的相位差(图 6)。DCM1 生成与 DATACLK1 和 DATACLK2 频率相同的时钟。DCLK1的延迟可以以时钟周期的1/256步长动态调整。触发器 DFF1 和 DFF2 在每个时钟周期中对 DATACLK1 和 DATACLK2 进行一次采样。如果 DFF1 对 DATACLK1 进行采样,而 DATACLK1 为低电平,则 DFF1 将输出静态“0”。如果 DFF1 在 DATACLK1 为高电平时对 DATACLK1 进行采样,则 DFF1 将输出静态“1”。因此,DFF3 和 DFF4 可以在任何时钟相位上计时,与 DCLK1 上的延迟设置无关。通过将DCLK1延迟步进其范围,使用DCM1中的动态延迟调整功能,并读取DFF3和DFF4的输出,可以找到与DATACLK1和DATACLK2的上升沿相对应的延迟设置。通过延迟设置,可以计算将数据延迟到MUX-DAC1所需的DAC时钟周期数,以便与进入MUX-DAC2的数据同相。通过在FPGA中实现4 x 4桶形移位器,可以以DAC时钟周期为增量6来改变数据延迟(见图《》)。

MAX19692具有四个并行数据端口,分别标有A、B、C和D。馈送到DAC的字序列为An, Bn, Cn, Dn一个N+1, BN+1, CN+1, DN+1一个N+2等。12位、4 x 4桶形移位器(图6)允许发往MUX-DAC1的数据延迟-1、0、1或2个CLK周期。因此,可以调整数据延迟,直到两个DAC同相输出数据。在这种情况下,两个DAC的数据时钟可能会偏离时钟的整数周期数(CLK),并且不会尝试更改此值。由于DAC的建立和保持时间以数据时钟为基准,因此两个DAC的数据时序必须不同。这可以通过在驱动DAC的FPGA中使用多个DCM来实现。

图6.使用在FPGA中实现的桶形移位器的MUX-DAC同步。

DAC 同步,每个 DAC 使用一个 PLL

如果使用锁相环 (PLL) 频率合成器对 DAC 进行计时,则同步两个 DAC 的一种方法是使用单独的 PLL 为每个 DAC 提供时钟(图 7)。将DAC1和DAC2的LVDS数据时钟输出的相位与参考时钟进行比较。在这种情况下,DAC的内置时钟分频器用作时钟代PLL中的反馈分频器。

图7.多路复用器同步,每个DAC使用一个PLL。

使用此解决方案匹配两个DAC的建立和保持时间。然而,该解决方案的两个缺点是两个PLL的成本增加,以及PLL中的相位噪声限制可能导致的性能限制。

结论

MAX19692为2.3Gsps、12位多奈奎斯特DAC,集成4:1输入数据多路复用器,理想用于I/Q应用。虽然强调MAX19692在I/Q应用中的应用,但所讨论的方案也适用于其他DAC和应用,例如MAX5858A用于具有两个以上通道的应用。 建议的解决方案可以扩展到任意数量的DAC。为了正确同步高速器件,必须考虑与威廉希尔官方网站 板走线相关的延迟。

审核编辑:郭婷

-

如何使用高速放大器的低成本视频多路复用2020-06-01 0

-

请问如何消除多路复用DAC的输出错误?2021-04-20 0

-

多路复用与数字复接2008-10-22 749

-

多路复用技术2009-06-27 989

-

发射应用中多个高速、复用DAC的同步2008-09-11 897

-

复用器的多路复用2010-01-07 1189

-

时分多路复用(TDM),时分多路复用(TDM)的原理是什么?2010-03-19 10356

-

什么是同步时分多路复用技术(STDM)2010-04-03 2568

-

时分多路复用(TDM),时分多路复用(TDM)是什么意思2010-04-03 5917

-

如何将多个输入信号多路复用到单个高分辨率高速SAR模数转换器的概述2018-05-18 988

-

EUVIS高速多路复用器介绍2021-11-10 928

-

一文详解多路复用的类型2024-03-05 3334

全部0条评论

快来发表一下你的评论吧 !