汇编语言结构与8086概述

描述

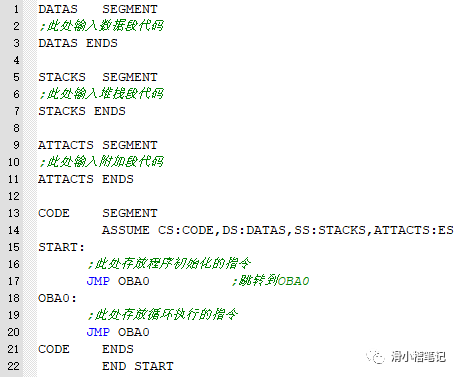

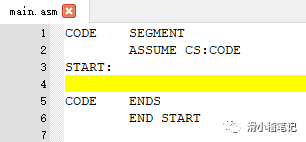

1.1 汇编语言基本结构模板

汇编语言的基本框架由这四部分组成,如果某个段没有代码,可以将与该段有关的代码删除。

1.2 8086 CPU简介

Intel8086是一个由Intel于1978年所设计的16位微处理器芯片,是x86架构的鼻祖。不久之后,Intel 就推出了 Intel 8088 (一个拥有8根外部数据总线的微处理器)。它是以8080和8085的设计为基础,拥有类似的寄存器组,但是数据总线扩充为16位。总线界面单元透过6字节预存的队列位指令给执行单元,所以取指令和执行是同步的,8086 CPU有20条地址线,可直接寻址1MB的存储空间,每一个存储单元可以存放一个字节的二进制信息。

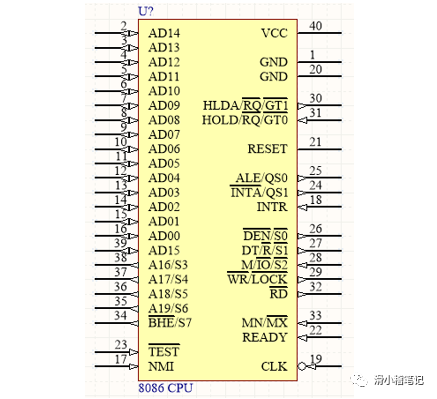

1.2.1 8086引脚详解

(1) 地址/数据复用AD0~AD15 :双向三态门结构,采用分时的方法传送地址或数据的复用引脚。根据不同时钟周期的要求,决定当前是传送要访问的存储单元或I/O端口的低16位地址,还是传送16位数据,或是处于高阻状态;

(2) 地址状态S3~S6 :地址/状态信号,三态门,采用分时的方法传送地址或状态的复用引脚。其中A19~A16为20位地址总线的高4位地址,S6~S3是状态信号。S6表示CPU与总线连接的情况,S5指示当前中断允许标志IF的状态。S4,S3的代码组合用来指明当前正在使用的段寄存器。S4与S3的代码组合及对应段寄存器的情况;

(3) 允许总线高8位数据传送/状态信号BHE/S7 :输出三态,为总线高8位数据允许信号,当低电平有效时,表明在高8位数据总线D15 ~D8上传送1个字节的数据。S7为设备的状态信号;

(4) 时钟脉冲输入端口CLK :用于输入工作脉冲,8086的脉冲为5MHz的方波信号;

(5) 准备就绪信号READY :高电平有效;

(6) 最大最小工作模式选择端MN/MX :高电平为最小工作模式,低电平为最大工作模式;

(7) 读信号RD :低电平有效;

(8) 等待测试控制信号TEST :输入,低电平有效。信号用来支持构成多处理器系统,实现8086 CPU与协处理器之间同步协调的功能,只有当CPU执行WAIT指令时才使用;

(9) 可屏蔽中断请求信号INTR :高电平有效,8086 CPU在每条指令执行到最后一个时钟周期时,都要检测INTR引脚信号。INTR为高电平时,表明有I/O设备向CPU申请中断,若IF=1,CPU则会响应中断,停止当前的操作,为申请中断的I/O设备服务;

(10) 非屏蔽中断请求信号NMI :高电平有效,当NMI引脚上有一个上升沿有效的触发信号时,表明CPU内部或I/O设备提出了非屏蔽的中断请求,CPU会在结束当前所执行的指令后,立即响应中断请求;

(11) 复位信号RESET :高电平有效。RESET信号有效时,CPU立即结束现行操作,处于复位状态,初始化所有的内部寄存器。复位后各内部寄存器的状态,当RESET信号由高电平变为低电平时,CPU从FFFF0H地址开始重新启动执行程序

最小工作模式下使用的引脚

(1) 存储器和I/O端口选择控制信号M/IO :信号指明当前CPU是选择访问存储器还是访问I/O端口。为高电平时,访问存储器,表示当前要进行CPU与存储器之间的数据传送。为低电平时,访问I/O端口,表示当前要进行CPU与I/O端口之间的数据传送;

(2) 写信号WR :低电平有效。信号有效时,表明CPU正在执行写总线周期,同时由信号决定是对存储器还是对I/O端口执行写操作;

(3) 可屏蔽中断响应信号INTA :低电平有效;

(4) 地址锁存允许信号ALE :高电平有效。CPU利用ALE信号可以把AD15~AD0地址/数据、A19/S6~A16/S3地址/状态线上的地址信息锁存在地址锁存器中;

(5) 数据发送接收信号DT/R :三态门结构,用来控制数据传送的方向。高电平时,CPU发送数据到存储器或I/O端口;低电平时,CPU接收来自存储器或I/O端口的数据;

(6) 数据允许控制信号DEN :三态,低电平有效信号,用作总线收发器的选通控制信号。当为低电平时,表明CPU进行数据的读/写操作;

(7) 总线保持请求信号HOLD :高电平有效。在DMA数据传送方式中,由总线控制器8237A发出一个高电平有效的总线请求信号,通过HOLD引脚输入到CPU,请求CPU让出总线控制权。

(8) 总线保持响应信号HLDA :高电平有效。HLDA是与HOLD配合使用的联络信号。在HLDA有效期间,HLDA引脚输出一个高电平有效的响应信号,同时总线将处于浮空状态,CPU让出对总线的控制权,将其交付给申请使用总线的8237A控制器使用,总线使用完后,会使HOLD信号变为低电平,CPU又重新获得对总线的控制权。

最大工作模式下使用的引脚

(1) 总线周期状态信号S2,S1,S0 :低电平有效。它们表明当前总线周期所进行的操作类型,代码组合及其对应操作见下表

| S2 | S1 | S0 | 执行的操作 |

|---|---|---|---|

| 0 | 0 | 0 | 中断响应 |

| 0 | 0 | 1 | 读IO端口 |

| 0 | 1 | 0 | 写IO端口 |

| 0 | 1 | 1 | 暂停 |

| 1 | 0 | 0 | 取指 |

| 1 | 0 | 1 | 读存储器 |

| 1 | 1 | 0 | 写存储器 |

| 1 | 1 | 1 | 无效 |

(2) 总线请求允许信号输入/总线请求允许输出信号RQ和GT :低电平有效。该信号用以取代最小模式时的HOLD/HLDA两个信号的功能,是特意为多处理器系统而设计的。当系统中某一部件要求获得总线控制权时,就通过此信号线向8086 CPU发出总线请求信号,若CPU响应总线请求,就通过同一引脚发回响应信号,允许总线请求,表明8086 CPU已放弃对总线的控制权,将总线控制权交给提出总线请求的部件使用。RQ/GT0优先级高于RQ/GT1;

(3) 总线封锁信号LOCK :低电平有效。信号有效时,表示此时8086 CPU不允许其他总线部件占用总线;

(4) 指令队列状态信号QS1和QS0 :QS1和QS0信号的组合可以指示总线接口部件BIU中指令队列的状态,以便其他处理器监视、跟踪指令队列的状态。

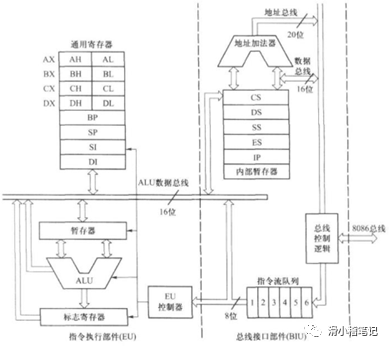

1.2.2 8086内部结构框图

总线接口单元BIU构成

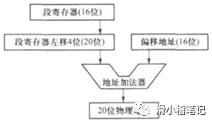

(1) 地址加法器 :用于形成20位的物理地址,将段寄存器提供的段基址左移4位,再加上16位的偏移地址生成,送往外部总线,用于寻址内存单元,其工作原理如图所示。

(2) 4个16位的代码段寄存器 ,分别为代码段寄存器CS,数据段寄存器DS,堆栈段寄存器SS,扩展段寄存器ES,其中:

代码段寄存器CS:用于存放当前程序所在段—代码段的首地址;

数据段寄存器DS:用于存放当前程序所用数据段的段首地址;

堆栈段寄存器SS:用于存放当前程序所用堆栈段的段首地址;

扩展段寄存器ES:用于存放辅助数据(字符串操作的目的区地址)所在段的段首地址。

(3) 指令指针寄存器IP :用于存放下一条指令的偏移地址;

(4) 一个6字节的指令队列缓冲器 :当执行单元EU正在执行指令且不需要占用总线时,BIU会主动的执行预取指令操作,将所取的指令按先后次序存入指令队列缓冲器中,队列遵循“先入先出”原则,并按顺序取到EU中执行;

(5) 总线控制部件 :用于产生并发出控制信号。

执行单元EU组成

(1) 算术逻辑单元ALU :用于进行算术运算与逻辑运算;

(2) 4个16位通用寄存器AX,BX,CX,DX :用于保存操作数或者运算结果;

(3) 4个16位专用寄存器 :只能以字的形式操作,常用于段内寻址时提供偏移地址,分别为:堆栈指针寄存器SP,基址指针寄存器BP,源变址寄存器SI和目的变址寄存器DI;

(4) 一个16位的标志寄存器FR :又称为程序状态寄存器PSW,用于存放控制标志和反应CPU运行的状态特征,标志寄存器内容如下图所示:

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| OF | DF | IF | TF | SF | ZF | AF | PF | CF |

OF:溢出标志位

0:没有溢出

1:数据溢出

DF:方向标志位

0:向前

1:向后

IF:中断标志位

0:禁止中断

1:允许中断

TF:陷阱标志位

SF:符号标志位

0:正数

1:负数

ZF:零标志位

0:不是0

1:全0

AF:辅助进位标志位

0:关闭辅助

1:开启辅助

PF:奇偶标志位

0:偶数

1:奇数

CF:进位标志位

1.2.3 8086的工作时序图

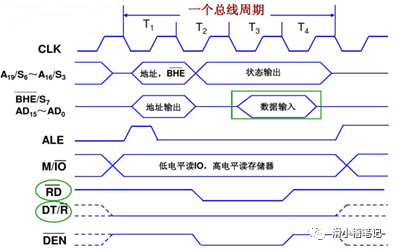

在8086CPU中,一个最基本的总线周期由4个时钟周期组成,即T1,T2,T3,T4一共4个状态,当CPU需要等待时,可以插入1个或多个等待状态Tw。

最小工作模式下的读时序

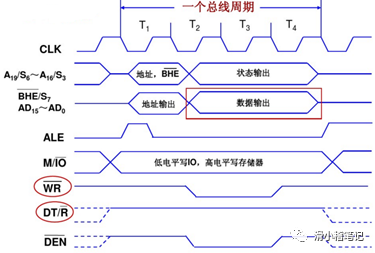

最小工作模式下的写时序

总线写操作时序与读操作时序基本相似,但是存在几个不同点:

(1)CPU不是输出RD信号,而是输出WR信号;

(2)DT/R整个总线周期都是高电平,表示总线周期为写周期,在接有数据总线收发器的系统中,用来控制数据传输方向;

(3)AD15~AD0在T2到T4状态输出数据,输出地址与输出数据为同一方向,无需像读周期那样要高阻态做缓冲,所以T2状态无高阻态。

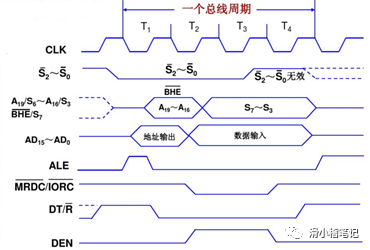

最大工作模式下的读时序

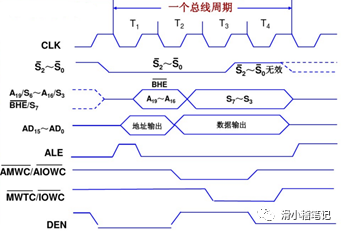

最大工作模式下的写时序

最大工作模式与最小工作模式时序的区别:

(1) 控制信号ALE、DEN和DT/R :最大模式中,ALE、DEN和DT/R由总线控制器8288发出,DEN高电平有效,最小模式中,ALE、DEN和DT/R由8086 CPU直接发出,DEN是低电平有效;

(2) 命令信号MRDC、MWTC、AMWC、IORC、IOWC和状态信号S2,S1,S0 :由于在最大方式下必须使用总线控制器8288,因此在其时序图中必然出现访问存储器和IO接口的命令信号。

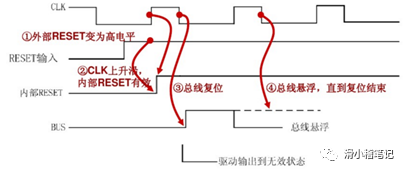

复位时序

条件:检测到RESET引脚为上升沿。

复位逻辑威廉希尔官方网站 :用CLK来与外部RESET同步,内部RESET信号要在时钟的上升沿到来时才有效

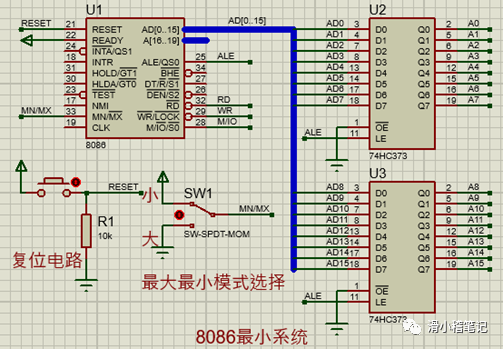

1.5 8086最小系统搭建

图中的8086 CPU只需要注意以下几个事情即可:

(1)8086是高电平复位,所以正常运行时需要将21脚接低电平,图中的复位威廉希尔官方网站 当按键没有按下的时候,用一个10K的下拉电阻将该引脚强制拉低,当按键按下的时候,21脚会变为高电平,此时8086进入复位模式,抬起按键后,8086停止复位,进入工作模式;

(2)33脚是最大最小工作模式选择引脚,当该引脚接VCC时,8086工作在最小工作模式,当该引脚接GND时,8086则工作在最大工作模式,一般默认其工作在最小工作模式;

(3)图中利用74HC373作为地址锁存,由于8086 CPU首先发送地址信息,然后发送数据,所以,当8086在T1和T2时刻发送地址时,利用ALE的下降沿脉冲锁存地址,确保其余的器件能够检测到地址信息。(注:由于8086具有20根地址线,最大寻址空间为1M,在仿真图中只是用了其中的低16位);

(4)将8086的RD,WR,ALE和M/IO端口引出作为控制线;

(5)由于8086在仿真中已经设计了一个5MHz的时钟源,所以不需要绘制时钟信号输入,在实际设计中,需要外接5MHz的时钟源。

(6)INTA是8086的一个外部中断引脚,可以单独使用,或者配合中断芯片来扩展中断的个数,最大可支持256个中断。

1.6 Protuse 8.6环境搭建

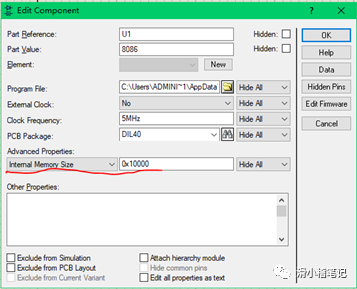

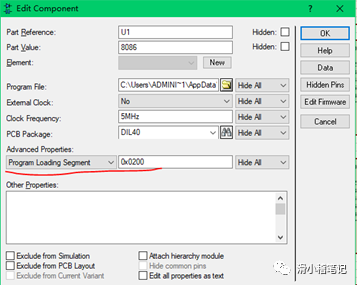

1.6.1 仿真8086 CPU配置

(1)放置8086 CPU,74HC373等需要的器件,然后连接对应的引脚;

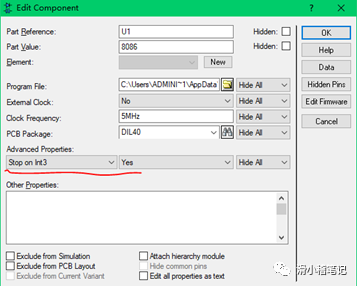

(2)设置8086CPU的参数,双击8086会弹出参数对话框,此时需要设置三个参数:Internal Memory Size为1000H,Program Loading Segment为200H,Stop On Int3为Yes,如下图所示:

1.6.2 程序编写配置

(1)点击如图所示的按钮创建一个源文件SourceCode;

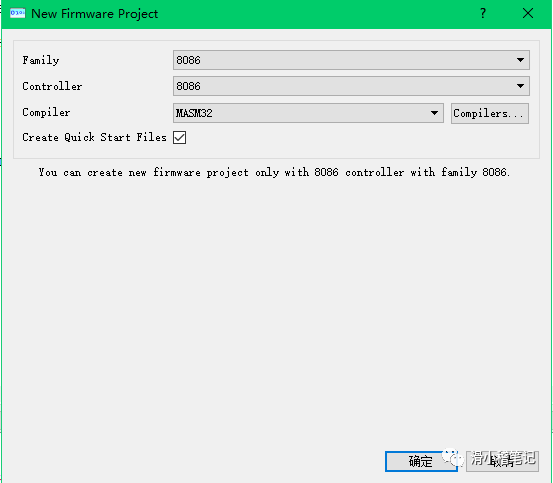

(2)点击菜单栏中Project->CreateProject,然后在弹出对话框进行设置:

① Family中选择8086

② Compiler中选择MASM32(如果显示MASM32未安装,直接点击DownLoad下载安装即可)。

③ 然后点击确定,即可创建一个8086的工程,输入如下图所示的代码后点击运行即可编译成功并运行程序。

注:汇编的源文件后缀是.asm格式

-

如何利用EMU8086仿真系统实现汇编语言程序的编写和编译?2022-01-18 0

-

什么是汇编语言2022-02-24 0

-

汇编语言程序设计下载2008-10-21 728

-

汇编语言静态分析工具设计与应用2009-06-19 503

-

汇编语言自学教程2010-03-15 1722

-

汇编语言程序结构2008-09-28 2866

-

Linux中的汇编语言2011-04-07 610

-

Assemble汇编语言威廉希尔官方网站2011-07-07 529

-

ARM汇编语言官方手册(中文)2015-12-28 3764

-

汇编语言例2015-12-31 696

-

汇编语言学习课件_汇编语言程序组织2015-12-31 668

-

16位和32位微处理器指令系统与汇编语言编程2015-12-31 690

-

汇编语言程序设计自学教程2016-04-06 841

-

汇编语言结构化设计程序教程2021-03-26 598

-

单片机汇编语言的结构/数据类型/汇编指令2023-07-07 2975

全部0条评论

快来发表一下你的评论吧 !