求一种Ti60F100高速IO实现HDMI环出方案

描述

xilinx和altera都有通过IO驱动HDMI的方案,支持的分辨率各有不同,这跟不同系列的FPGA性能是相关的。

易灵思的钛金系列FPGA是采用16nm工艺的,属于高性能FPGA,它支持1.5G LVDS及高速的IO,这成为了实现HDMI自环的基础。并通过本实验验验证了Ti60F100来实现了1080p60的接收与发送的可行性。

我们先来了解下TMDS的电气特性。

TMDS电气特性

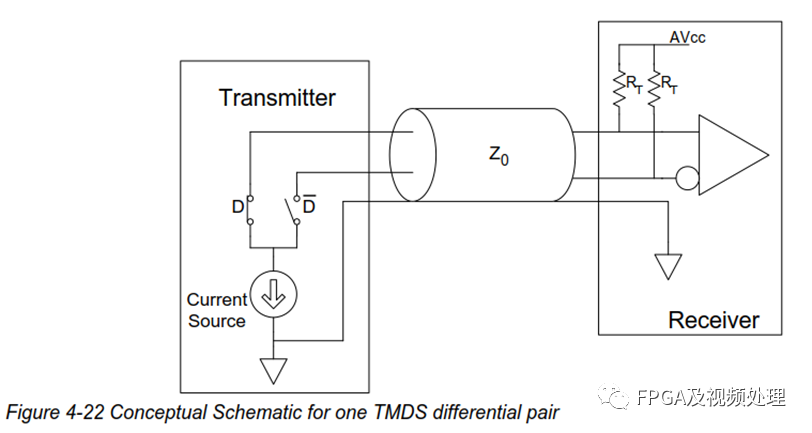

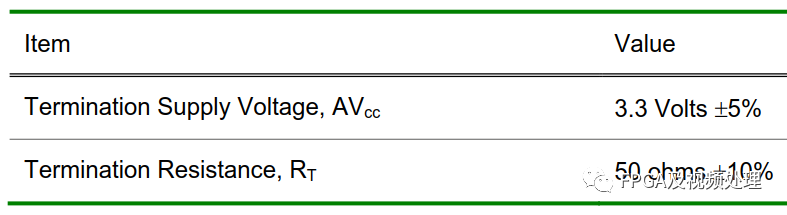

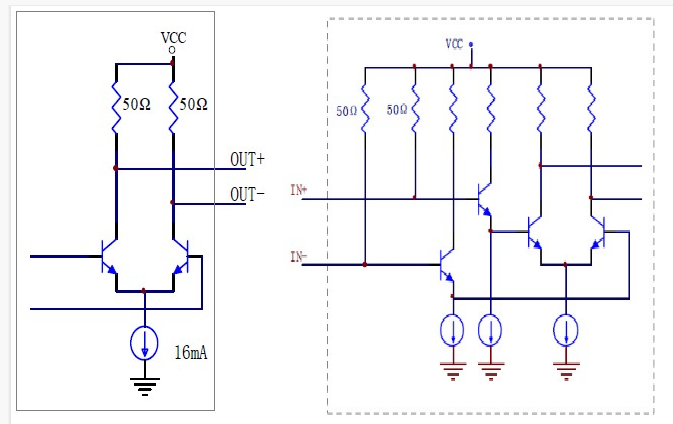

TMDS利用电流驱动技术在直流耦合传输线接收端产生低压差分信号。链路参考电压AVcc设置差分信号的高电压电平,而低电压电平由HDMI源端的电流源和接收终端电阻(RT)决定。终端电阻(RT)和电缆的特性阻抗(Z0)必须匹配。

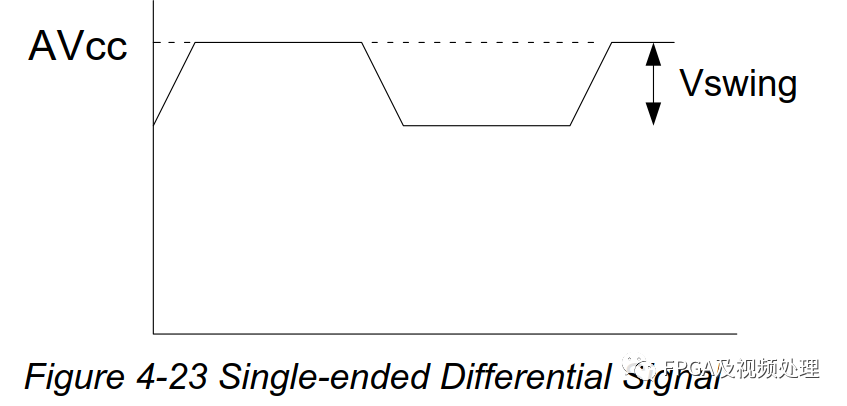

对于差分信号的一端,标称高电平电压为AVcc,标称低电平电压为(AVcc - Vswing)。

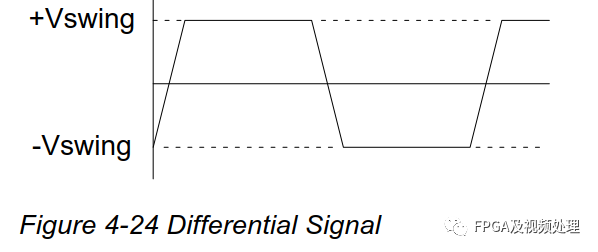

差分对上的摆幅是一端摆幅的两倍,2*Vswing ,约为1000mV(VP-VN,分别指TMDS差分对的P端或者N端)。

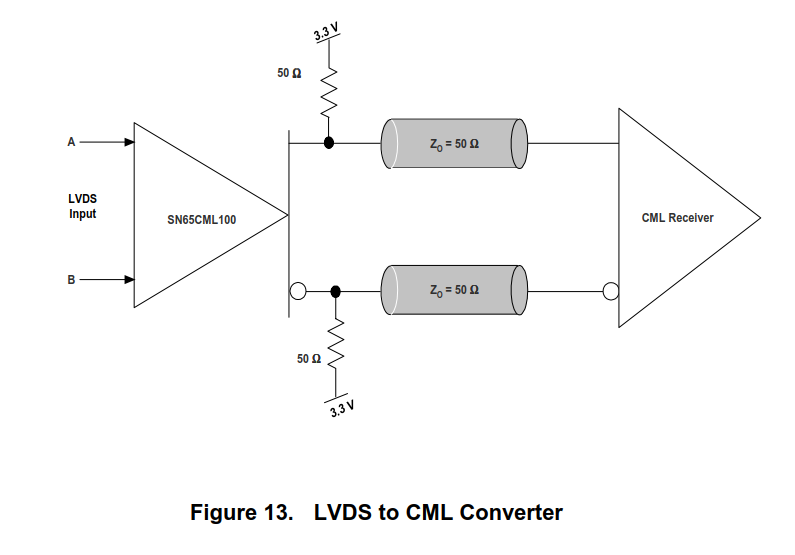

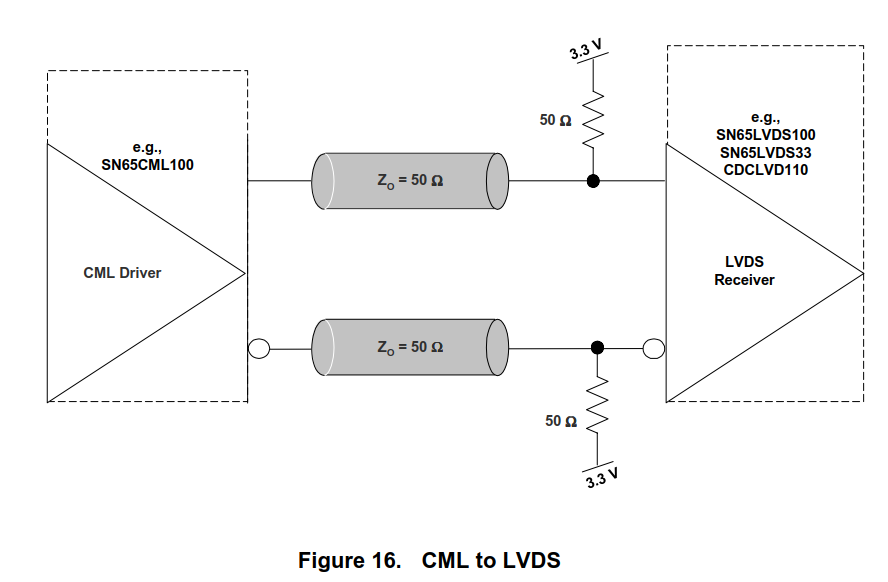

从框图上看TMDS电平更符合或者说接近CML的电平标准。在源端都有一个恒流源。而且差分对高电低电平的实现也都是通过源端一端导通一端截止来实现,只是HDMI的上拉通过接收端来实现。在接收端都对输入信号上拉到了50欧,其余部分也可以认为相同。

所以LVDS与CML的电平转换成为了硬件设计的理论基础。

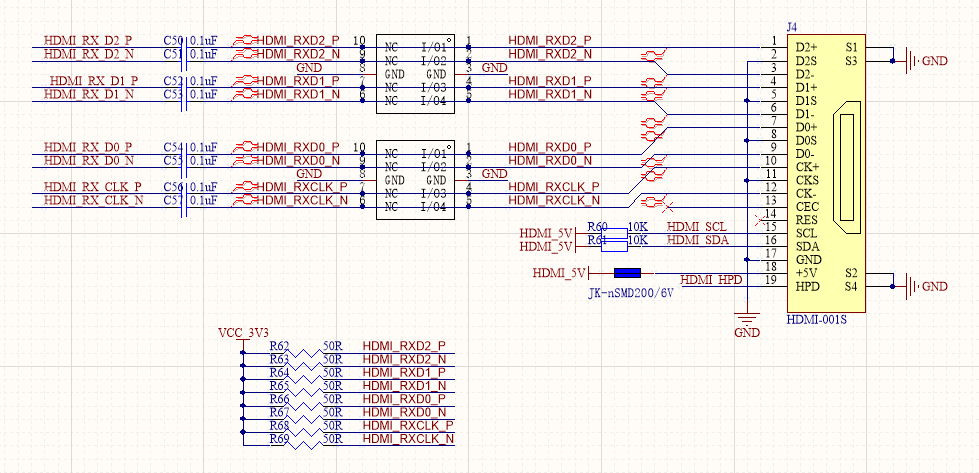

本次验证通过Ti60F100来实现。硬件采用炫览科技开发的demo板。

测试环境为输入采用1.5M HDMI线,输出采用3M HMDI。测试分辨为1080p60fps和720p60fps.

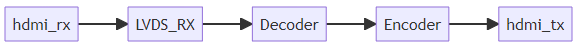

HDMI接收过程

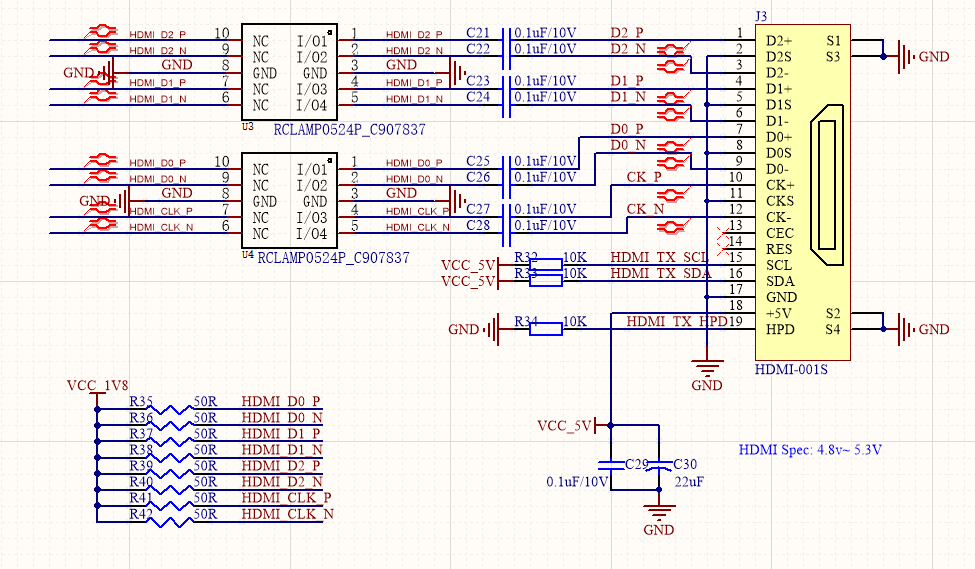

HDMI接收端通过50R电阻上拉,再通过电容耦合连接到FPGA。

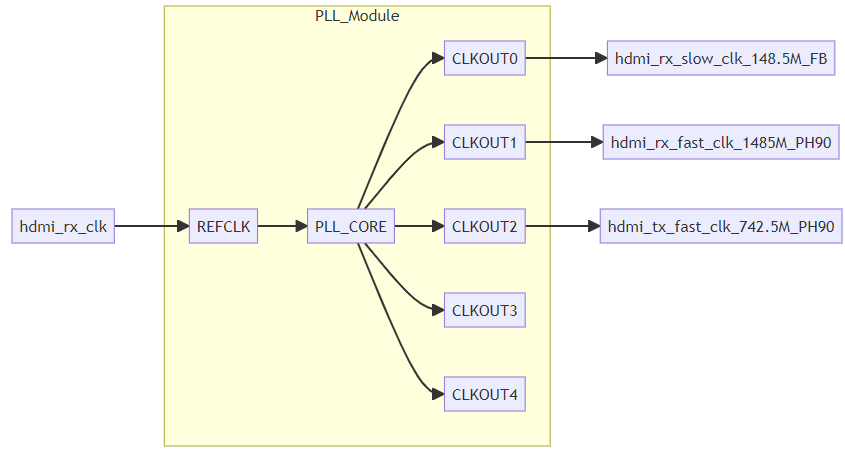

时钟方案如下:

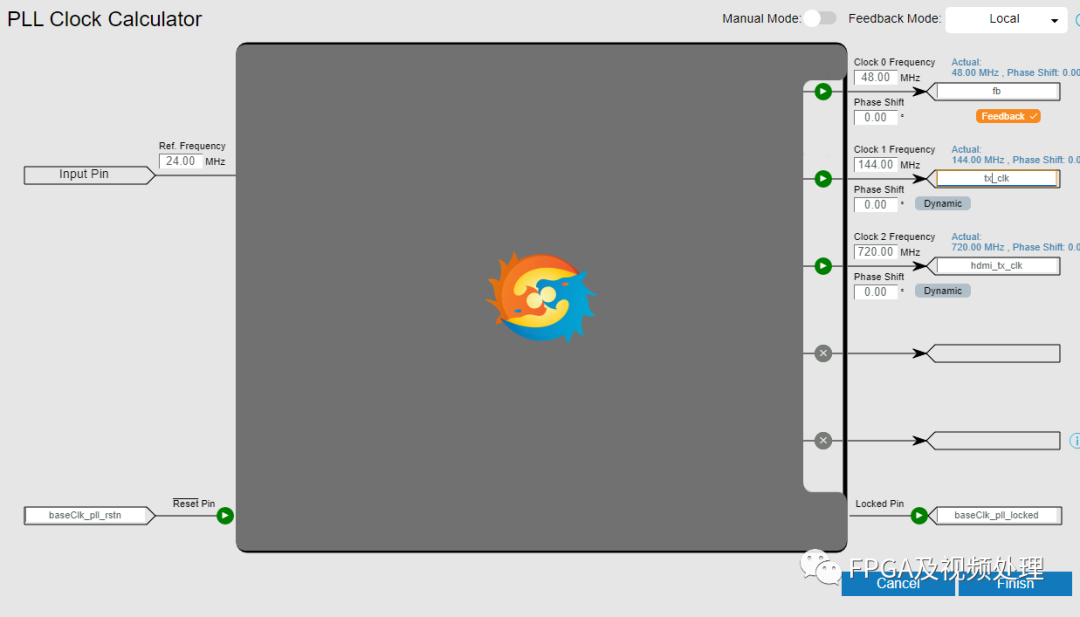

HDMI接收时钟经过PLL产生串行时钟742.5M用于1080p串行数据采集。通过LVDS实现串并换转换成10位并行数据同步到148.5M的时钟上。

实现过程如下:

HDMI发送处理

与LVDS转CML的电平转换相似,只不过这里都使用了交流耦合。有时间再尝试DC耦合方式。

另外从IO的和锁相环性能的角度出发,我们试验了以下两种方案:

方案一 :通过单端实现伪TMDS差分

理论基础是:

TMDS差分传动技术是一种利用2个引脚间电压差来传送信号的技术。传输数据的数值("0"或者"1")由两脚间电压正负极性和大小决定。即,采用2根线来传输信号,一根线上传输原来的信号,另一根线上传输与原来信号相反的信号。这样接收端就可以通过让一根线上的信号减去另一根线上的信号的方式来屏蔽电磁干扰,从而得到正确的信号。

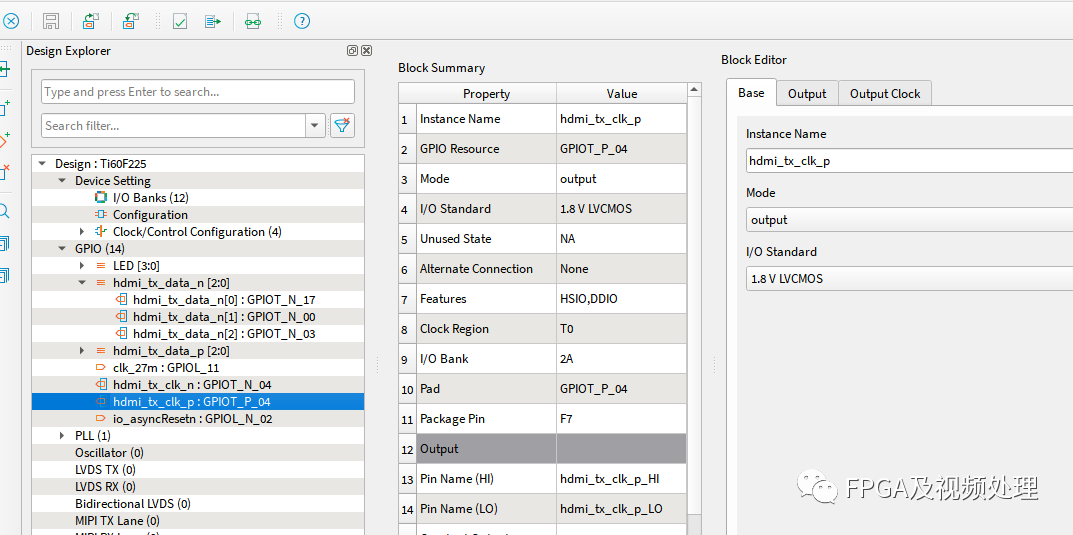

按照上面的原理我们把HDMI的4对差分对通过单端来实现。我们分别对HDMI的三对数据和一对时钟用LVCMOS 1.8V电平实现。并勾选DDIO选项。

时钟的设置如下。由于锁相环的限制,内部处理时钟为144,数据位宽为10位,接口上通过时钟双沿采样,时钟为720。测试分辨率为1080p@58Hz,画面输出正常。如果通过时钟用25M的话,快速时钟为750M应该也是可以的。

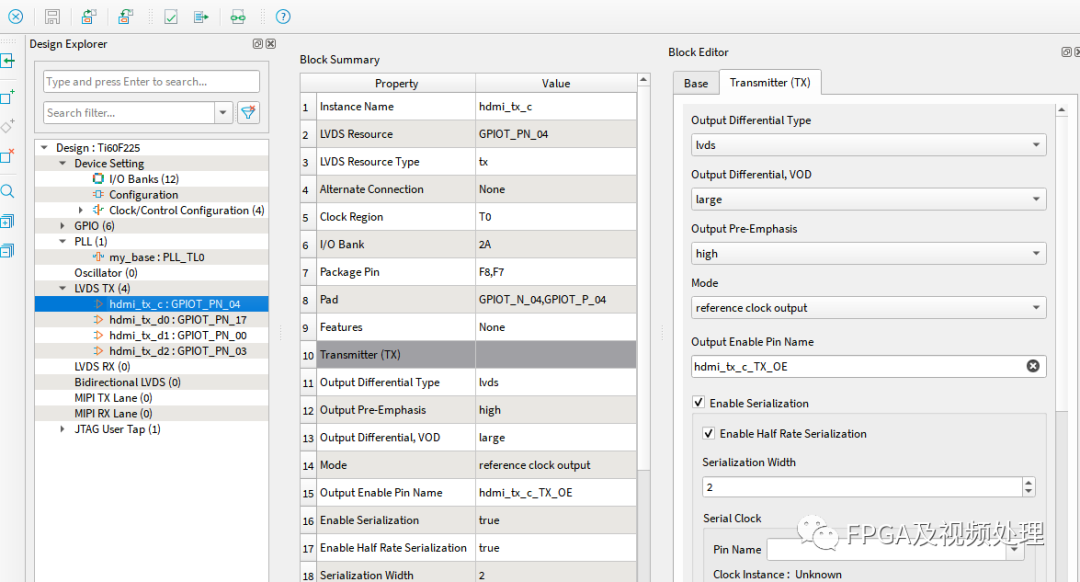

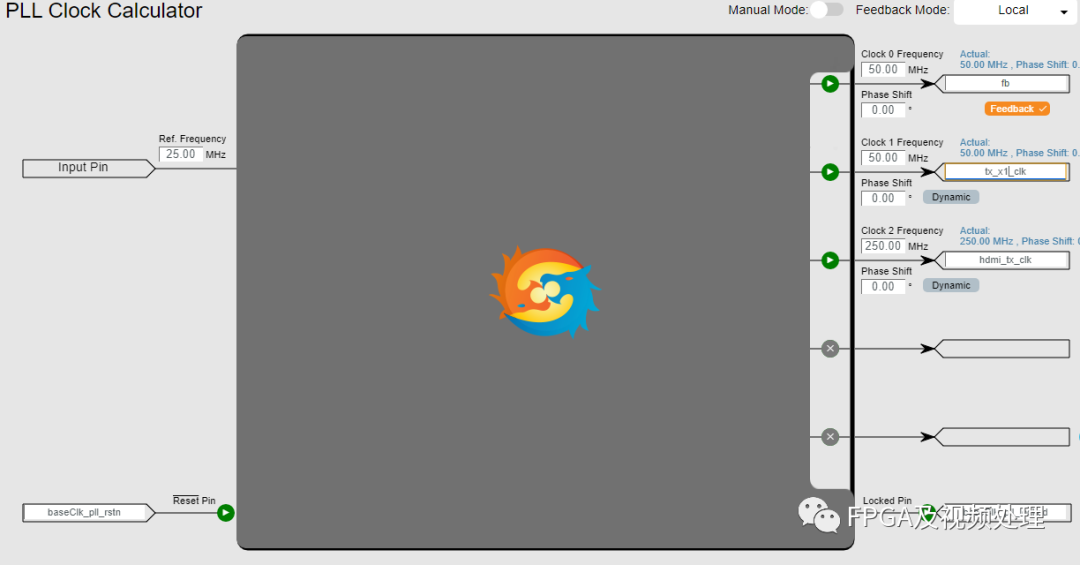

方案二:通过LVDS实现替代TMDS差分对

在interface中例化4对LVDS输出。并通过PLL产生对应的并行与串行时钟。

另外关于5V接收与发送,HPD和DDC的处理都相对比较简单,在这里就不详细展开了。

审核编辑:刘清

-

求大神分享一种高速突发模式误码测试仪的FPGA实现方案2021-04-29 0

-

求一种锁相环位同步提取威廉希尔官方网站 的设计方案2021-04-29 0

-

求一种低成本高速USB接口的设计方案2021-05-10 0

-

求一种CO2144 10-100BaseT参考设计方案2021-05-25 0

-

求一种HDMI转VGA音视频数据转换芯片方案2021-05-28 0

-

如何去实现一种高速通信接口的设计?2021-06-02 0

-

求一种DisplayPort到DVI / HDMI信号转换适配器方案2021-06-03 0

-

如何去实现一种STM32环境监控系统的设计呢2021-11-26 0

-

求一种基于STM32的Modbus主机实现方案2021-12-10 0

-

一种高速串行视频接口TIDA-00137参考设计2022-09-19 0

-

一种基于TMS320F2812的交流电机控制方案的实现2016-03-30 563

-

Ti60F100用片内flash启动RISCV程序不能成功的解决办法2023-02-15 1648

-

易灵思Ti60F100驱动LCD屏案例2023-07-10 1098

-

4K60 HDMI 输入与环出的音视频采集卡LCC380数据手册2024-04-14 273

-

Ti60F100 内外flash操作方案2024-05-20 1569

全部0条评论

快来发表一下你的评论吧 !