触发器发展史及类型(上)

电子说

描述

在电子学中,触发器(Flip-Flop)或锁存器(latch)是具有两种稳定状态并可用于存储状态信息的威廉希尔官方网站 ,专业术语双稳态多谐振荡器(多谐振荡器是一种电子威廉希尔官方网站 ,用于实现各种简单的两态设备,例如张弛振荡器、定时器和触发器,bistable multivibrator)。该威廉希尔官方网站 可以通过施加到一个或多个控制输入的信号来改变状态,并将具有一个或两个输出。它是时序逻辑中的基本存储元素。触发器和锁存器是计算机、通信和许多其他类型系统中使用的数字电子系统的基本组成部分。

触发器的线路图由逻辑门组合而成,其结构均由SR锁存器派生而来(广义的触发器包括锁存器)。触发器可以处理输入、输出信号和时序脉波(CK)之间的相互影响。这里的触发器特指flip-flop,flip-flop一词主要是指具有两个状态相互翻转,例如编程语言中使用flip-flop buffer(翻译作双缓冲)

触发器和锁存器用作数据存储元件。触发器是一种存储单个位(二进制位)数据的设备;它的两个状态之一代表“一”,另一个代表“零”。这种数据存储可用于存储状态,这种威廉希尔官方网站 在电子学中被描述为时序逻辑。在有限状态机中使用时,输出和下一个状态不仅取决于其当前输入,还取决于其当前状态(因此也取决于先前的输入)。它还可用于脉冲计数,以及将可变定时输入信号与某个参考定时信号同步。

触发器可以是电平触发(异步、透明或不透明)或边沿触发(同步或时钟)。触发器一词历来泛指电平触发和边沿触发威廉希尔官方网站 ,它们使用门存储单个数据位。最近,一些作者保留术语“触发器”专门用于讨论时钟威廉希尔官方网站 。简单的通常称为透明闩锁。[1] [2]使用这个术语,电平敏感触发器称为透明锁存器,而边沿触发触发器简称为触发器。使用任一术语,术语“触发器”指的是存储单个数据位的设备,但术语“锁存器”也可以指使用单个触发器存储任意数量的数据位的设备。术语“边缘触发”和“电平触发”可用于避免歧义。[3]

当启用电平触发锁存器时,它变得透明,但边沿触发触发器的输出仅在单一类型的时钟边沿(正向或负向)上改变。

触发器发展历史

来自 Eccles 和 Jordan 1918 年专利的触发器原理图,一个被绘制为具有正反馈路径的级联放大器,另一个被绘制为对称交叉耦合对1918 年,英国物理学家s William Eccles 和 F. W. Jordan发明了第一台电子触发器。它最初被称为Eccles-Jordan 触发威廉希尔官方网站 ,由两个有源元件(真空管)组成。该设计用于 1943 年的英国Colossus 密码破译计算机 ,即使在引入集成威廉希尔官方网站 之后,这种威廉希尔官方网站 及其晶体管版本在计算机中也很常见。早期的触发器被称为触发威廉希尔官方网站 或多谐振荡器。

根据美国喷气推进实验室( Jet Propulsion Laboratory)的工程师 PL Lindley 的说法,下面详述的触发器类型(SR、D、T、JK)首先在 1954 年由 Montgomery Phister 的加州大学洛杉矶分校计算机设计课程中讨论,然后出现在他的《数字计算机的逻辑设计》一书。Lindley 当时在 Eldred Nelson 手下的 Hughes Aircraft 工作,他创造了术语 JK 来表示当两个输入都打开时会改变状态的触发器(逻辑上的“1”)。其他名字是菲斯特创造的。它们与下面给出的一些定义略有不同。在设计逻辑系统时,Nelson 将以下字母分配给触发器输入:#1:A & B,#2:C & D,#3:E & F,#4:G & H,#5:J & K. Nelson在 1953 年提交的专利申请中使用了符号“ j -input”和“ k -input”。

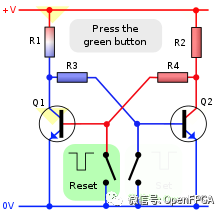

基于双极结型晶体管的传统(简单)触发器威廉希尔官方网站 触发器可以是简单的(透明的或异步的)或同步的。在硬件描述语言(HDL)的上下文中,简单的语言通常被描述为锁存器,而时钟控制的语言被描述为触发器。

简单的触发器可以围绕一对交叉耦合的反相元件构建:真空管、双极晶体管、场效应晶体管、反相器和反相逻辑门都已用于实际威廉希尔官方网站 。

时钟设备是专门为同步系统设计的;此类设备会忽略其输入,除非在专用时钟信号(称为时钟、脉冲或选通)的转换中。时钟使触发器根据转换时输入信号的值改变或保持其输出信号。一些触发器在时钟的上升沿改变输出,另一些在下降沿改变输出。

由于初级放大级是反相的,因此可以将两个级连续连接(作为级联)以形成所需的同相放大器。在这种配置中,每个放大器可以被视为另一个反相放大器的有源反相反馈网络。因此,尽管威廉希尔官方网站 图通常绘制为对称的交叉耦合对(这两幅图最初都在 Eccles-Jordan 专利中引入),但两个级在同相环路中连接。

触发器类型

触发器可以分为常见的类型:SR(“set-reset”)、D(“data”或“delay”)、T(“toggle”)和JK。特定类型的行为可以通过所谓的特征方程来描述,该方程导出“next”(即,在下一个时钟脉冲之后)输出。

复位锁存器

当使用静态门作为构建块时,最基本的锁存器是简单的SR 锁存器,其中 S 和 R 代表 set 和 reset。它可以由一对交叉耦合的NOR或NAND 逻辑门构成。存储的位出现在标记为 Q 的输出上。

基于双极结型晶体管的传统(简单)触发器威廉希尔官方网站 ## SR NOR锁存器

SR 锁存器的动画,由一对交叉耦合的NOR 门构成。红色和黑色分别表示逻辑“1”和“0”。当 R 和 S 输入均为低电平时,反馈将 Q 和 ~Q 输出保持在恒定状态, ~Q 是Q的补码。如果 S ( Set ) 脉冲高电平而 R ( Reset ) 保持低电平,则 Q 输出强制为高,当 S 回到低时保持高;同样,如果在 S 保持低电平时 R 脉冲为高电平,则 Q 输出被强制为低电平,并在 R 恢复为低电平时保持低电平。

SR 锁存操作真值表

注意:X 表示don't care ,即 0 或 1 都是有效值。

R = S = 1 组合称为受限组合或禁止状态,因为两个 NOR 门随后输出零,它打破了逻辑方程 Q = not (~Q)。这种组合在两个输入可能同时变低的威廉希尔官方网站 中也不合适(即从受限转换到保持)。根据门之间的传播时间关系(竞争条件),输出将锁定在 1 或 0。

SR NOR锁存器的工作原理。

SR 锁存器动画。黑色和白色分别表示逻辑“1”和“0”。

- S = 1,R = 0:设置

- S = 0,R = 0:保持

- S = 0,R = 1:复位

- S = 1,R = 1:不允许

从受限组合 (D) 到 (A) 的转变会导致不稳定状态。

为了克服受限组合,可以将门添加到将转换(S, R) = (1, 1)为非受限组合之一的输入。那可以是:

Q = 1 (1, 0) – 称为S(主控)锁存器 Q = 0 (0, 1) – 称为R(主控)锁存器

这几乎在每个可编程逻辑控制器中都完成了。

保持状态 (0, 0) – 称为E-latch

或者,可以进行受限组合以切换输出。结果是JK 锁存器。

SR NOR锁存器的工作原理### SR NOR锁存器的特征方程为:

另一个表达式是:

SR NAND 锁存器

由交叉耦合的NAND 门构成的SR锁存器。下面显示的威廉希尔官方网站 是一个基本的 NAND 锁存器。输入通常指定为 S 和 R,分别表示 set 和 reset。由于 NAND 输入通常必须为逻辑 1 以避免影响锁存动作,因此在该威廉希尔官方网站 中输入被认为是反相的(或低电平有效)。

即使在控制输入信号发生变化后,威廉希尔官方网站 也使用反馈来“记住”并保持其逻辑状态。当 S 和 R 输入都为高电平时,反馈将 Q 输出保持在之前的状态。

SR锁存器真值表

SR NAND 锁存器的符号## SR AND-OR 锁存器

一个 SR AND-OR 锁存器。浅绿色表示逻辑“1”,深绿色表示逻辑“0”。锁存器当前处于保持模式(无变化)。从教学的角度来看,将 SR 锁存器绘制为一对交叉耦合组件(晶体管、门、管等)对于初学者来说通常很难理解。一种教学上更容易理解的方法是将锁存器绘制为单个反馈回路,而不是交叉耦合。下面是一个 SR 锁存器,它带有一个带有一个反相输入的AND门和一个OR门。请注意,锁存功能不需要反相器,而是使两个输入都处于高电平有效状态。

SR AND-OR 锁存器真值表

请注意,SR AND-OR 锁存器具有明确定义 S = 1、R = 1 的优点。在上述版本的 SR AND-OR 锁存器中,它优先于 R 信号而不是 S 信号。如果需要 S 优先于 R,这可以通过将输出 Q 连接到 OR 门的输出而不是 AND 门的输出来实现。

SR AND-OR 锁存器更容易理解,因为两个门都可以单独解释。当 S 或 R 均未设置时,或门和与门都处于“保持模式”,即它们的输出是来自反馈回路的输入。当输入 S = 1 时,或门的输出变为 1,而与来自反馈回路的其他输入无关(“set模式”)。当输入 R = 1 时,与门的输出变为 0,而与来自反馈回路的其他输入无关(“reset模式”)。由于输出 Q 直接连接到 AND 门的输出,因此 R 优先于 S。绘制为交叉耦合门的锁存器可能看起来不太直观,因为一个门的行为似乎与另一个门交织在一起。

请注意,SR AND-OR 锁存器可以使用逻辑转换转换为 SR NOR 锁存器:将 OR 门的输出和 AND 门的第二个输入反相,并在这两个添加的反相器之间连接反相 Q 输出;根据德摩根定律,两个输入反转的与门等效于或非门。

JK 锁存器

JK 锁存器的使用频率远低于 JK 触发器。JK 锁存器遵循以下状态表:

JK锁存器真值表

因此,JK 锁存器是一个 SR 锁存器,当通过 11 的输入组合时,它会触发其输出(在 0 和 1 之间振荡)。与 JK 触发器不同,JK 锁存器的 11 输入组合是不是很有用,因为没有指示切换的时钟。

门控锁存器(闩锁)和条件透明

闩锁设计为透明的。也就是说,输入信号的变化会导致输出的立即变化。当另一个输入(“enable”输入)未被断言时,可以将附加逻辑添加到简单的门控锁存器以使其不透明或不透明。当多个门控锁存器彼此跟随时,使用相同的使能信号,信号可以一次通过所有这些锁存器传播。然而,通过一个透明高锁存器和一个透明低(或不透明高)锁存器,实现了主从触发器。

门控 SR 锁存器

与非门控 SR 锁存器(时钟 SR 触发器)。注意反相输入。

由AND门(左侧)和NOR门(右侧)构成的门控 SR 锁存器威廉希尔官方网站 图。可以通过将第二级 NAND 门添加到反相SR 锁存器(或将第二级与门添加到直接SR 锁存器)来制作同步 SR 锁存器(有时是时钟 SR 触发器)。额外的 NAND 门进一步反转输入,因此SR锁存器变为门控 SR 锁存器(并且 SR 锁存器将转换为具有反转使 能的门控SR锁存器)。

当 E 高( enable 真)时,信号可以通过输入门到达封装锁存器;除了 (0, 0) = hold之外的所有信号组合,然后立即在 (Q, ~Q ) 输出上再现,即锁存器是透明的。

E 低(enable 假)时,锁存器关闭(不透明)并保持上次 E 为高时的状态。

使能输入有时是时钟信号,但更常见的是读或写选通信号。当使能输入是时钟信号时,锁存器被称为对电平敏感(对时钟信号的电平),而不是像下面的触发器那样 对边沿敏感。

门控 SR 锁存器真值表

门控 SR 锁存器的符号## 门控 D 锁存器

该锁存器利用了以下事实:在门控 SR 锁存器的两个有效输入组合(01 和 10)中,R 是 S 的补码。输入 NAND 级将两个 D 输入状态(0 和 1)转换为这两个输入通过反转数据输入信号来组合下一个SR锁存器。使能信号的低状态产生无效的“11”组合。因此,门控 D 锁存器可被视为单输入同步 SR 锁存器。此配置可防止应用受限输入组合。它也被称为透明锁存器、数据锁存器或简单的门控锁存器。它有一个数据输入和一个启用信号(有时称为时钟或控制)。透明这个词来自这样一个事实,即当使能输入打开时,信号直接通过威廉希尔官方网站 传播,从输入 D 到输出 Q。门控 D 锁存器也对时钟电平敏感或使能信号。

D存器通常用作 I/O 端口或在异步系统中,或在同步两相系统(使用两相时钟的同步系统)中,其中两个在不同时钟相位上运行的锁存器会阻止数据透明性,就像在主机中一样——从触发器。

锁存器可用作集成威廉希尔官方网站 ,通常每个芯片具有多个锁存器。例如,74HC75是7400 系列中的四通D锁存器。

下面的真值表显示,当enable / c lock输入为0时,D输入对输出没有影响。当 E/C 为高时,输出等于 D。

门控 D 锁存器真值表

门控 D 锁存器的符号

基于SR NAND 锁存器 的门控 D 锁存器

基于 SR NOR 锁存器的门控 D 锁存器

动画门控 D 锁存器。黑色和白色分别表示逻辑“1”和“0”。

- D = 1,E = 1:设置

- D = 1,E = 0:保持

- D = 0,E = 0:保持

- D = 0,E = 1:复位

传输晶体管逻辑中的门控 D 锁存器,类似于 CD4042 或 CD74HC75 集成威廉希尔官方网站 中的锁存器。## 厄尔锁存器(厄尔闩锁)Earle latch

经典的门锁设计有一些不受欢迎的特性。它们需要双轨逻辑或逆变器。输入到输出的传播可能需要多达三个门延迟。输入到输出的传播不是恒定的——一些输出需要两个门延迟,而另一些需要三个。

一个成功的替代品是厄尔闩锁。它只需要一个数据输入,它的输出需要两个恒定的门延迟。此外,在某些情况下,Earle 锁存器的两个门级可以与驱动锁存器的威廉希尔官方网站 的最后两个门级合并,因为许多常见的计算威廉希尔官方网站 都有一个 OR 层,然后是 AND 层作为它们的最后两个级别. 合并锁存功能可以实现没有额外门延迟的锁存。这种合并通常用于流水线计算机的设计,事实上,它最初是由 John G. Earle 开发的。

厄尔闩锁没有危险。如果省略中间的与非门,则得到极性保持锁存器,这是常用的,因为它需要较少的逻辑。但是,它容易受到逻辑风险的影响。有意偏斜时钟信号可以避免这种危险。

Earle 锁存器使用互补使能输入:使能低电平有效 (E_L) 和使能高电平有效 (E_H)

厄尔闩锁动画。黑色和白色分别表示逻辑“1”和“0”。

- D = 1,E_H = 1:设置

- D = 0,E_H = 1:复位

- D = 1,E_H = 0:保持

-

恒压变压器的发展史2008-07-29 0

-

蓝牙耳机发展史2019-10-22 0

-

Linux系统发展史及版本更迭2020-04-29 0

-

5G的发展史2020-12-24 0

-

硬件:Intel CPU发展史 精选资料推荐2021-07-26 0

-

萌新求助,求关于ARM发展史及各时期内核的知识点2021-10-22 0

-

unix系统发展史2009-01-18 1854

-

3G发展史2009-10-29 753

-

声卡的发展史2009-12-26 1398

-

触发器的类型转换2010-08-23 4837

-

触发器发展史及类型(下)2023-03-23 6889

-

触发器的类型介绍2023-03-23 17313

-

触发器的触发顺序是什么2024-02-05 1172

-

电阻柜的发展史2024-03-08 469

-

边沿触发器的类型有哪些2024-08-11 805

全部0条评论

快来发表一下你的评论吧 !