浅析MOS 晶体管的核心概念

电子说

描述

MOS 晶体管正在按比例缩小,以最大限度地提高其在集成威廉希尔官方网站 内的封装密度。这导致氧化层厚度的减少,进而降低了 MOS 器件的阈值电压。在较低的阈值电压下,泄漏电流变得很大,并有助于功耗。这就是为什么我们必须了解 MOS 晶体管中各种类型的泄漏电流的原因。

在我们尝试了解各种漏电流组件之前,让我们先重新回顾一下 MOS 晶体管的核心概念。这将有助于我们更好地了解该主题。

重新审视 MOS 晶体管结构

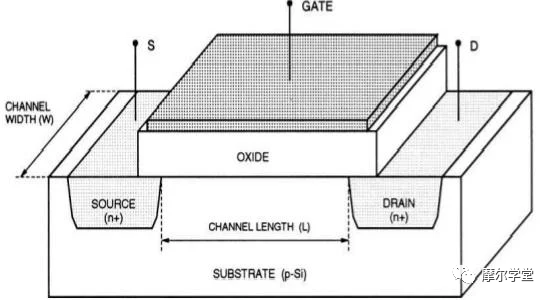

MOS晶体管结构由金属、氧化物和半导体结构(因此,MOS)组成。

考虑具有 p 衬底和 n+ 扩散阱作为漏极和源极端子的 NMOS 晶体管。氧化层由SiO 2制成并生长在漏极和源极之间的沟道上。栅极端子由n+掺杂的多晶硅或铝制成。

图 1. NMOS 晶体管的鸟瞰图。所有图片来自 SM Kang, Y. Leblebici, CMOS 数字集成威廉希尔官方网站 , TMH, 2003, ch.3, pp:83-93

在无偏置条件下,漏极/源极和衬底界面处的 pn 结是反向偏置的。晶体管的能带图如图2所示。

图 2. 无偏 NMOS 晶体管的能带图

如您所见,金属、氧化物和半导体的费米能级相互对齐。由于氧化物-半导体界面处的电压降,Si 能带存在弯曲。内建电场的方向是从金属到氧化物再到半导体,电压降的方向与电场的方向相反。

这种电压降是由于金属和半导体之间的功函数差异而发生的(部分电压降发生在氧化物上,其余部分发生在 Si-SiO 2界面上)。功函数是电子从费米能级逃逸到自由空间所需的能量。

积累

接下来,假设栅极有负电压,源极的漏极和衬底接地。由于负电压,基板中的空穴(多数载流子)被吸引到表面。这种现象称为积累。衬底中的少数载流子(电子)被推回深处。对应的能带图如下。

图 3.栅极端负电压 NMOS 晶体管的能带图

由于电场的方向是从半导体到氧化物再到金属,所以能带向相反方向弯曲。此外,请注意费米能级的变化。

耗尽和耗尽区

或者,考虑栅极电压刚好大于零。空穴被排斥回基板中,并且通道耗尽了任何移动电荷载流子。这种现象称为耗尽,并创建了比无偏条件更宽的耗尽区域。

图 4. NMOS 中的耗尽区

图 5. 图 4 所示 NMOS 耗尽区的相应能带图

由于电场是从金属到氧化物再到半导体,所以能带向下弯曲。

表面反转

如果进一步增加栅极处的正电压,则衬底中的少数载流子(电子)被吸引到沟道表面。这种现象称为表面反转,而表面刚好反转的栅极电压称为阈值电压 (V th )。

图 6. NMOS 晶体管的表面反转

图 7.图 6 所示 NMOS 晶体管的相应能带图

电子在源极和漏极之间形成一个传导通道。如果随后从零电位开始增加漏极电压,则漏极电流 (I d ) 开始在源极和漏极之间流动。能带进一步向下弯曲并在半导体-氧化物界面处弯曲。

这里,本征费米能级小于 p 型衬底的费米能级。这支持了这样的观点,即在表面,半导体是 n 型的(在 n 型材料的能带图中,本征费米能级的能级低于施主能级)。

-

晶体管之间的差异2016-06-07 0

-

概述晶体管2019-05-05 0

-

MOS晶体管2009-11-05 3724

-

P沟MOS晶体管2009-11-07 933

-

N沟MOS晶体管2009-11-09 2313

-

CMOS晶体管,CMOS晶体管是什么意思2010-03-05 3784

-

增强型MOS晶体管,增强型MOS晶体管是什么意思2010-03-05 2448

-

MOS晶体管的应用2019-04-19 7725

-

浅析MOS管介绍与应用2021-11-13 1296

-

MOS晶体管的工作原理2023-02-03 1585

-

MOS管和晶体管的概念2023-02-17 2392

-

了解短通道MOS晶体管中的漏电流元件2023-05-03 1751

-

晶体管和mos管的区别是什么?2023-08-25 6610

-

数字威廉希尔官方网站 的基础概念:MOS晶体管2024-07-29 766

全部0条评论

快来发表一下你的评论吧 !