Chiplet和先进封装——后摩尔时代芯片演进的全新道路

描述

摩尔定律极限将至

随着摩尔定律的飞速发展,芯片制程早已大步迈入了 10nm 以下,一路发展至 7nm、5nm,并触达了现阶段业界普遍认为的物理极限——3nm。在进入 10nm 的大关后,工艺迭代的速度已经放缓,先进工艺的高昂成本问题也令制造商和终端消费者感到头疼。

除了面临先进工艺的成本挑战,在摩尔定律逼近极限的“后摩尔时代”,半导体行业也无法再继续通过微缩晶体管来提升芯片性能,行业亟需新的技术路线来满足对芯片性能日益增长的需求,而这也正是 Chiplet 和先进封装的“用武”之处。

接下来,我们将通过阐述定义来进一步揭开 Chiplet 和先进封装的奥秘,以内存为例,为您解读后摩尔时代的芯片发展趋势。

Chiplet、UCIe 与异构集成

Chiplet 一般指预制好的、具有特定功能的、可用来组合集成的晶片,也叫芯粒,其技术重点在于将不同的芯片连接在一起并进行封装。在这个过程中,芯片之间的连接由于异构性、互操作性以及数据完整度等问题面临着诸多挑战。

因此,2022 年 3 月 ,英特尔、AMD、Arm、高通、三星、台积电等科技巨头联合成立了 UCIe 产业联盟,共同推出了开放的行业互联标准,使芯片制造商能够轻松地将不同类型的芯片集成到同一芯片系统中。

作为知名的内存供应商,华邦电子也在前不久加入了 UCIe 产业联盟,与联盟伙伴共同助力高性能 Chiplet 接口标准的推广与普及。

如今大家争相探讨的异构集成,全称为异构异质集成,包含了异构与异质双重含义。其中,制造商将如 3nm、5nm、7nm 甚至 28nm 和 45nm 等不同工艺制程、不同功能、不同制造商的 Chiplet 集成到一起,被称作异构集成。而为了设计出小尺寸、低成本、设计灵活、系统性能出色的芯片产品,制造商还会将诸如硅、氮化镓、碳化硅、磷化铟等不同材质的 Chiplet 集成在一起,这被称作异质集成。

UCIe 标准的建立为异构芯片提供了高带宽、低延迟、高电源效率和高性价比的封装内连接,从而满足整个计算系统的需求。

Chiplet 与先进封装

现阶段,业内对先进封装的共识是 2.5D/3D 以及 WLCSP 晶圆级封装,它们可在单位体积内集成更多的功能单元,以内存为例,先进封装可大幅增加内存容量。同时,这些功能单元的互连更短、密度更高,进一步提升合封后的芯片性能。

Chiplet 与先进封装是两个不同的概念,但在某种程度上它们却紧密相连——目前,行业内大多数的 Chiplet 是通过先进封装技术将不同工艺制造的芯片进行集成的。然而在采用 2.5D/3D 这样的垂直堆叠方式集成 Chiplet 芯片时,将面临几大关键挑战:

封装技术

随着业界对小型化的需求愈演愈烈,芯片必须保证在更小的封装空间内对更小尺寸的 Chiplet 芯片进行封装,因此对封装技术的要求极高;

连接设计

芯片堆叠的顺序、走线方式都会影响合封芯片的性能,因此需要最佳的设计方式来降低整体风险;

热管理

将芯片堆叠在一起后,散热问题更为严峻,高温会影响芯片的性能与寿命,因此需要采取更尖端的散热技术来避免高温导致的性能下降甚至是封装失效;

另一方面,合封后的系统级芯片性能与集成在其中的 Chiplet 芯片性能息息相关。因此必须采用具备如下特质的裸片才能保证最终的芯片性能。

高度可靠

尽管在单个 Chiplet 芯片良率高达 98% 的情况下,合封后的产品良率也会大幅下降,此外还可能会与其他芯片相互干扰,但提升裸片(die)的可靠性仍旧可在某种程度上提升合封芯片的可靠性;

散热合理

合封后,每个裸片与外界进行热传递的面积急剧缩小,发热量会进一步提高,因此必须尽可能降低裸片本身的散热,才能将合封芯片的发热控制在合理范围内;

高温稳定

合封芯片的发热远高于单一裸片的发热量,为此,裸片需要具备较好的高温下稳定性,才能保证芯片性能在温度升高的环境中不受损;

更低功耗

系统级芯片的功耗受 Chiplet 芯片的功耗影响极大,为满足用得低功耗需求,需要进一步降低裸片的自身功耗。

华邦的 KGD 和先进封装

KGD 产品

作为业界知名的 KGD 供应商,华邦早在 2008 年就已开始向客户提供诸多优质 KGD 产品,包括 DDR、LPDDR、HYPERRAM、NOR Flash 等,并可根据客户的不同需求灵活定制,进一步帮助客户提升成本和空间效益。

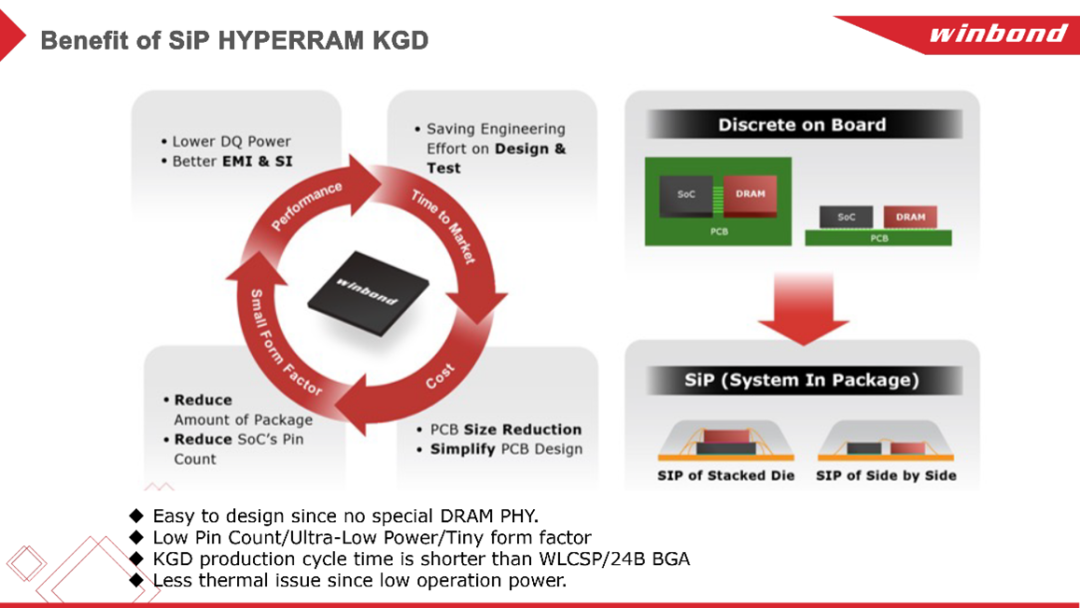

其中,凭借独到的性能优势,HYPERRAM 3.0 KGD 一经推出就席卷市场并备受好评。HYPERRAM KGD 的引脚更少、体积更小、设计更为简洁,因此能够更轻松地与客户产品合封,同时得益于 HYPERRAM 的超低功耗,还可显著降低合封后的发热风险。

先进封装

在深耕 KGD 产品的同时,华邦还致力于先进封装技术的革新,采用TSV(Through Silicon Via)硅通孔技术进一步提升 DRAM 的性能与容量。目前华邦已经推出了全新的3D TSV DRAM(又名 CUBE) KGD 产品,兼具高带宽与低功耗,能够确保 2.5D/3D 多芯片封装的能效,为客户带来优质的定制化内存解决方案。

此外华邦的 3DCaaS 一站式服务平台,在为客户提供优质 KGD 产品外,还将与合作伙伴共同为客户带来诸多工艺上的支持与产品技术咨询,例如针对多芯片优化的 2.5D、3D 后段工艺和 Silicon-Cap、interposer 技术等附加服务。

随着新能源汽车、5G、可穿戴设备等领域的不断发展,对芯片性能的需求也越来越高。然而随着后摩尔时代的到来,采用先进封装技术的 Chiplet 则成为了芯片微缩化进程的“续命良药”。除 UCIe 产业联盟外,众多头部制造商也在围绕 3D 封装建立全新的生态联盟,从封装角度为 Chiplet 的发展保驾护航。华邦也将竭诚发挥自身在 KGD 产品和先进封装领域的技术优势,为业界提供优质的定制化内存解决方案,让芯片在“长高”的路上越走越远。

审核编辑 :李倩

-

根据“后摩尔时代”芯片行业如何发展?2017-06-27 0

-

IC在后摩尔时代的挑战和机遇2010-02-21 1227

-

后摩尔时代Chiplet技术的演进与挑战2020-07-14 5030

-

后摩尔时代集成威廉希尔官方网站 产业特性及发展趋势2021-01-10 10397

-

聚焦后摩尔时代,后摩尔时代集成威廉希尔官方网站 产业如何突破2022-04-08 1578

-

光芯片走向Chiplet,颠覆先进封装2022-08-24 2224

-

普莱信智能孟晋辉出席CSPT 2022,共探后摩尔时代的封装技术2022-11-16 1024

-

先进封装Chiplet的优缺点与应用场景2023-06-13 1113

-

全球首个符合ASIL-D的车规级Chiplet D2D互连IP流片2023-06-15 489

-

SiP封装技术将制霸“后摩尔时代”?利尔达首款SiP模组应运而生!2022-07-20 925

-

Chiplet关键技术与挑战2023-07-17 1252

-

后摩尔时代芯片互连新材料及工艺革新2023-08-25 923

-

Chiplet,怎么连?2023-09-20 844

-

后摩尔定律时代,Chiplet落地进展和重点企业布局2023-12-21 1546

-

Chiplet在先进封装中的重要性2024-12-10 272

全部0条评论

快来发表一下你的评论吧 !