浅谈宽带RF接收机架构

电子说

描述

外差接收机作为接收机方案的标准选择已有数十年历史。 近年来,模数转换器 (ADC) 采样速率的迅速提高、嵌入式数字处理的采纳以及匹配通道的集成,为接收机架构提供了几年前尚被认为是不切实际的其他选择。

本文比较三种常用接收机架构的优势和挑战:外差接收机、直接采样接收机和直接变频接收机。 还会讨论关于杂散,系统噪声和动态范围的额外考虑。 本文的意图并非要褒扬某种方案而贬抑其他方案,相反,本文旨在说明这些方案的优点和缺点,并鼓励设计人员按照工程准则选择最适合特定应用的架构。

架构比较

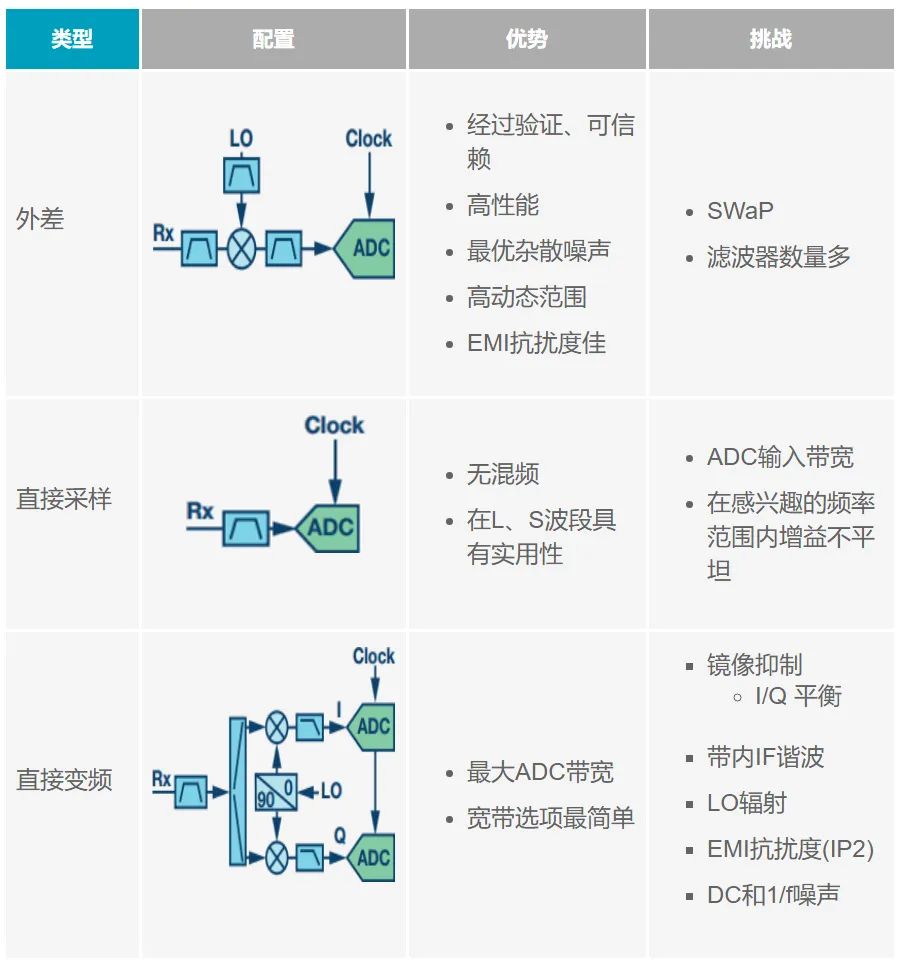

表1比较了外差、直接采样和直接变频三种架构。 同时显示了每种架构的基本拓扑和一些利弊。

表1. 接收机架构比较

外差方法久经检验,性能出色。 实施原理是混频到中频 (IF)。 IF需选择足够高的频率,使得实际滤波器在工作频段中能够提供良好的镜像抑制和LO隔离。 当有超高动态范围ADC可用时,增加一个混频级以降低频率也很常见。 此外,接收机增益分布在不同的频率上,这使得高增益接收机发生振荡的风险非常小。 通过适当的频率规划,外差接收机可以实现非常好的杂散能量和噪声性能。 遗憾的是,这种架构是最复杂的。 相对于可用带宽,其需要的功耗和物理尺寸通常是最大的。 此外,对于较大分数带宽,其频率规划可能非常困难。 在当前追求小尺寸、低重量、低功耗 (SWaP) 并希望获得宽带宽的背景下,这些挑战难度很大,导致设计人员不得不考虑其他可能的架构选项。

直接采样方法已被业界追求许久,其障碍在于很难让转换器工作于直接射频采样所需的速率并且实现大输入带宽以及实现大输入带宽。 在这种架构中,全部接收机增益都位于工作频段频率,如果需要较大接收机增益,布局布线必须非常小心。 如今,在L和S波段的较高奈奎斯特频段,已有转换器可用于直接采样。 业界在不断取得进展,C波段采样很快就会变得实用,后续将解决X波段采样。

直接变频架构对数据转换器带宽的使用效率最高。数据转换器在第一奈奎斯特频段工作,此时性能最优,低通滤波更为简单。两个数据转换器配合工作,对I/Q信号进行采样,从而提高用户带宽,同时又不会有交织难题。对于直接变频架构,困扰多年的主要挑战是维持I/Q平衡以实现合理水平的镜像抑制、LO泄漏和直流失调。近年来,整个直接变频信号链的先进集成加上数字校准已克服了这些挑战,直接变频架构在很多系统中已成为非常实用的方法。

频率规划视角

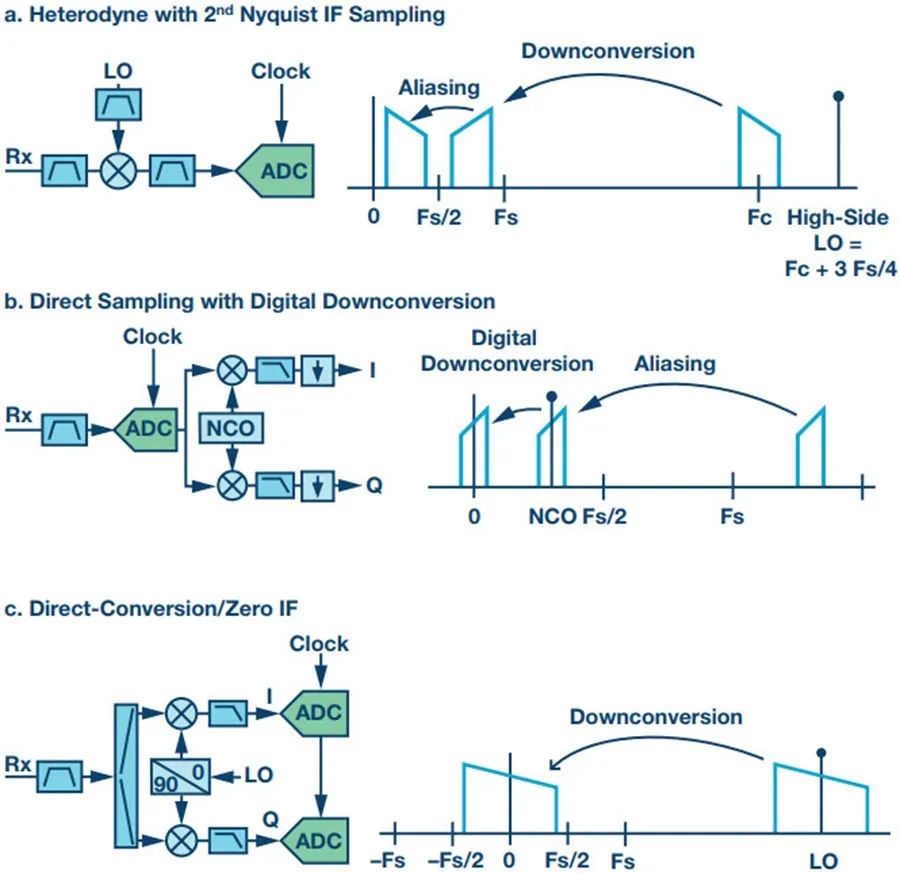

图1显示了三种架构的框图和频率规划示例。图1a为外差接收机示例,高端LO将工作频段混频到ADC的第二奈奎斯特区。信号进一步混叠到第一奈奎斯特区进行处理。图1b为直接采样接收机示例。工作频段在第三奈奎斯特区进行采样并混叠至第一奈奎斯特区,然后将NCO置于频段中心,数字下变频到基带,再进行滤波和抽取,数据速率降低到与通道带宽相称的水平。图1c为直接变频接收机示例。双通道ADC与正交解调器对接,通道1对I(同相)信号进行采样,通道2对Q(正交)信号进行采样。

图1. 频率规划示例。

许多现代ADC同时支持所有三种架构。例如,AD9680是一款具备可编程数字下变频功能的双通道1.25 GSPS ADC。此类双通道ADC支持双通道外差架构和直接采样架构,一对转换器合作则可支持直接变频架构。

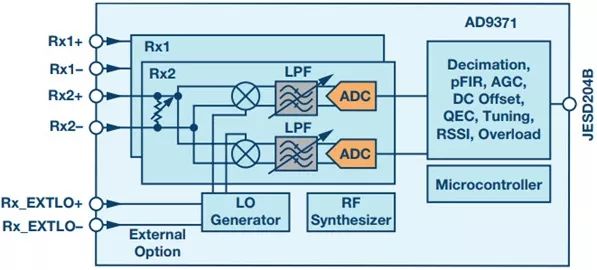

采用分立实施方案时,直接变频架构的镜像抑制挑战可能相当难以克服。通过提高集成度并结合数字辅助处理,I/Q通道可以很好地匹配,从而大幅改善镜像抑制。最近发布的AD9371的接收部分是一个直接变频接收机,如图2所示,注意它与图1c的相似性。

图2. AD9371的接收部分:单片直接变频接收机。

杂散噪声

任何采用频率转换的设计都需要作出很大努力来使不需要的带内折频最小化。这是频率规划最微妙的地方,涉及到可用元件与实际滤波器设计的平衡。某些杂散折叠问题在此略作说明,如需详细解释,请设计人员参阅参考文献。

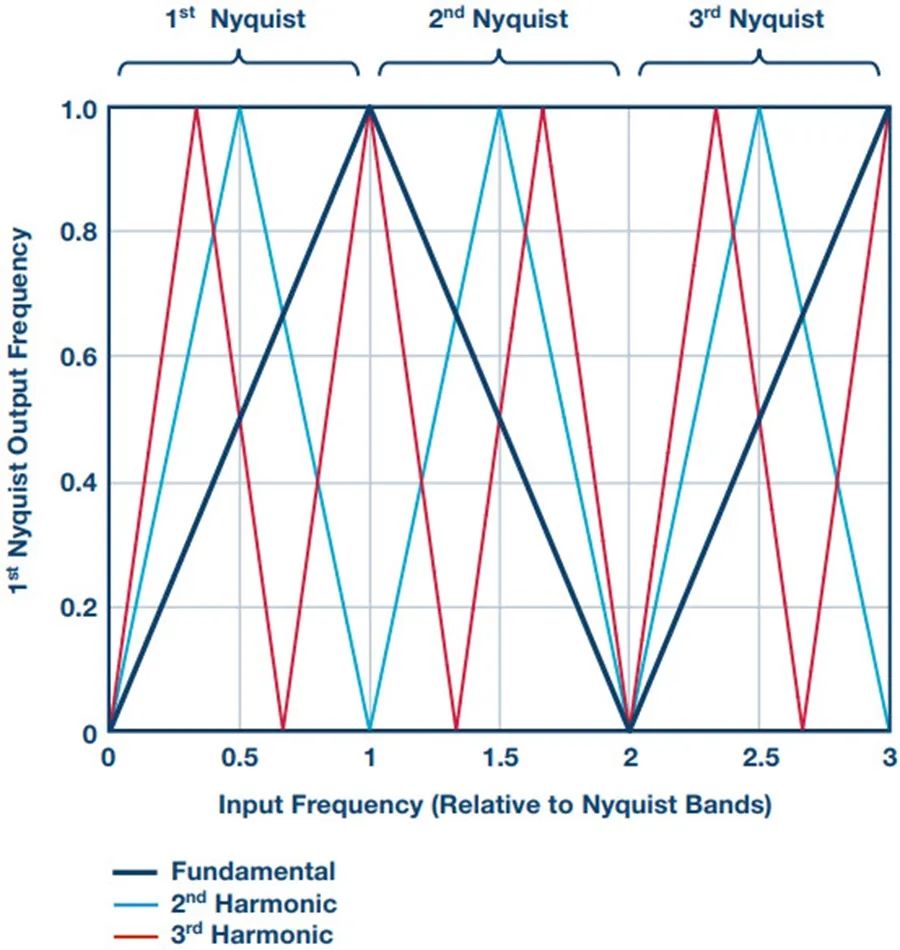

图3显示了ADC输入频率和前两个谐波的折叠与输入频率(相对于奈奎斯特频段)的关系。 当通道带宽远小于奈奎斯特带宽时,接收机设计人员的目标是选择适当的工作点以将折叠的谐波置于通道带宽之外。

图3. ADC折频

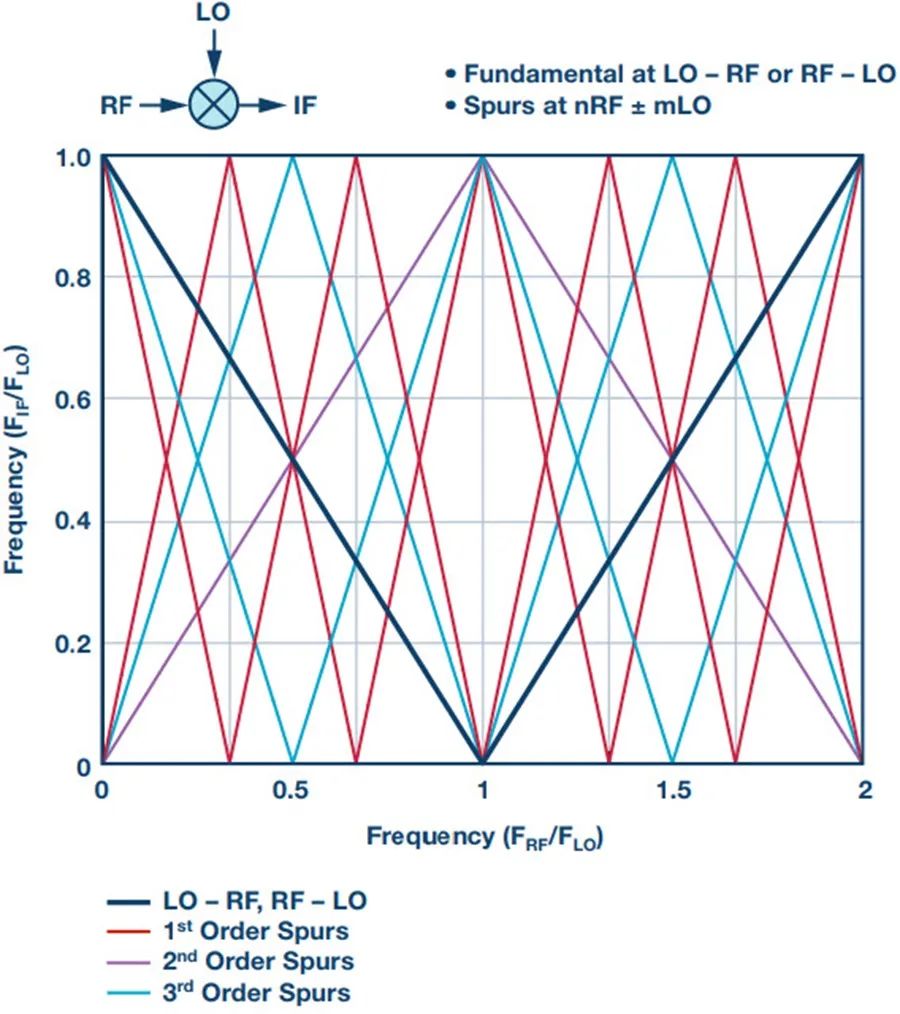

接收机下变频混频器会增加复杂性。 任何混频器都会在器件内引起谐波。 这些谐波全都混在一起,产生其他频率。 图4显示了这种影响。

图4. 下变频混频器杂散

图3和图4仅显示了截止三阶的杂散。 实践中还有其他更高阶的杂散,设计人员需要处理由此而来的无杂散动态范围问题。 对于较窄的小数带宽,细致精当的频率规划可以克服混频器杂散问题。 随着带宽增加,混频器杂散问题成为重大障碍。 由于ADC采样频率提高,有时候使用直接采样架构来降低杂散会更切合实际。

接收机噪声

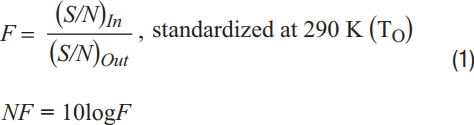

接收机设计的很多工作是花在最小化噪声系数 (NF) 上面。 噪声系数衡量信噪比的降低程度。

器件或子系统噪声系数的影响是使输出噪声功率高于热噪声水平,即被噪声系数放大。

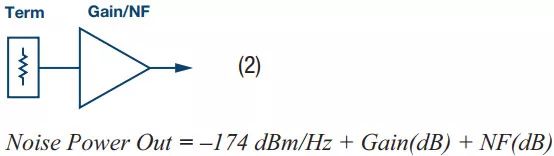

级联噪声系数计算如下:

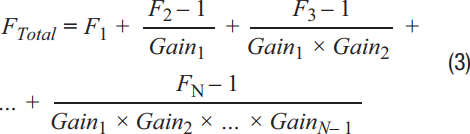

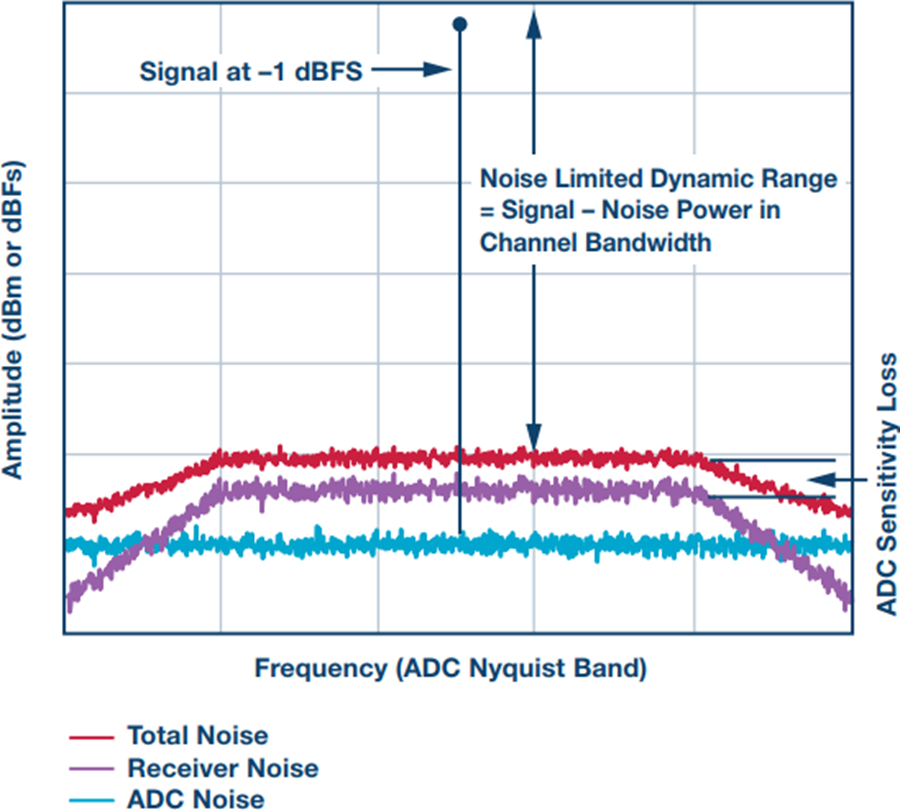

ADC之前的接收机增益的选择以及所需ADC SNR的确定,是接收机总噪声系数与瞬时动态范围平衡的结果。 图5为要考虑的参数的示意图。 为了便于说明,接收机噪声折算到ADC前端抗混叠滤波器之前,即被滤波之后的噪声。 ADC噪声显示为平坦的白噪声,目标信号显示为–1 dBFS的连续波 (CW) 信号音。

图5. 接收机 + ADC噪声

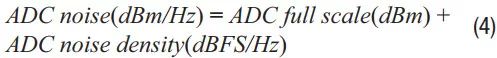

首先需要常用单位,即dBm或dBFS。 根据转换器满量程电平和转换器噪声密度,可将ADC噪声从dBFS换算为dBm。 此外,噪声功率与带宽成比例,故而需要一个常用带宽单位。 某些设计人员使用通道带宽,这里我们归一化到1 Hz带宽,噪声功率为/Hz。

总噪声计算如下:

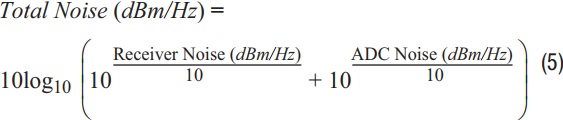

这就引出了ADC灵敏度损失概念。 ADC灵敏度损失用于衡量由ADC噪声引起的接收机噪声性能降低程度。 为使此降幅最小,接收机噪声需要远高于ADC噪声。 限制来自动态范围,较大接收机增益会限制能接收而不会使ADC饱和的最大信号。

因此,接收机设计人员总是要面对动态范围与噪声系数平衡的挑战。

结语

本文简述了外差、直接采样和直接变频三种接收机架构,重点讨论了每种架构的优势和挑战。 本文还介绍了接收机设计的最新趋势和考虑。 对更高带宽的普遍渴望,结合GSPS数据转换器的进步,将使许多不同的接收机设计在未来很长时间内百花齐放。

作者:Peter Delos ADI公司航空航天和防务部的技术主管, 前洛克希德马丁公司工程师。 为多个雷达和电子战计划开发接收机/激励器和频率合成器。 这段经验包括架构定义、详细设计、快速原型开发、制造、现场安装和协调多个工程专业。 他的工作引领了相控阵接收器/激励器从集中式架构到阵列上数字波束合成系统的转变。

审核编辑:汤梓红

-

什么是宽带RF接收机架构方案?2019-09-19 0

-

接收机架构之子威廉希尔官方网站 制作2008-10-15 577

-

宽带数字接收机的信道化设计2010-03-09 2204

-

短波宽带接收机信道化的仿真实现2011-09-30 943

-

超宽带雷达多通道接收机技术2016-12-29 919

-

宽带RF接收机架构方案综述2017-06-06 852

-

宽带RF接收机架构方案的综述2017-08-11 4036

-

三种常用接收机架构的优势和挑战及方案说明2020-10-13 1192

-

雷达接收机的噪声洗漱和灵敏度解析2020-11-16 5279

-

宽带RF接收机架构选项综述2023-01-04 1656

-

射频接收机的架构学习2023-02-24 1443

-

雷达接收机噪声系数定义 接收机噪声系数是多少2023-07-21 2960

-

低中频接收机架构的组成2023-08-24 1574

-

射频接收机的架构介绍2023-10-30 841

全部0条评论

快来发表一下你的评论吧 !