电子万年历设计方案(2)

描述

4.1 系统核心部分——闪电存储型器件AT89S52

4.1.1 AT89S52具有下列主要性能:

8KB可改编程序Flash存储器(可经受1000次的写入/擦除周期)

全静态工作:0Hz~24MHz

三级程序存储器保密

128×8字节内部RAM

32条可编程I/O线

2个16位定时器/计数器

6个中断源

可编程串行通道

片内时钟振荡器

4.1.2 AT89S52的引脚及功能

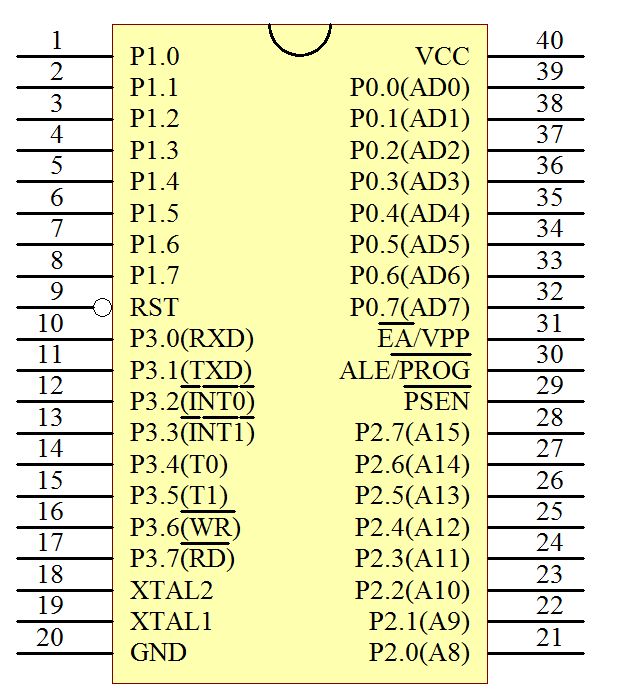

AT89S52单片机的管脚说明如图4-2所示。

(图4-2 AT89S52的管脚)

(1) 主要电源引脚

①VCC 电源端

②GND 接地端

(2) 外接晶体引脚XTAL1和XTAL2

①XTAL1 接外部晶体的一个引脚。在单片机内部,它是构成片内振荡器的反相放大器的输入端。当采用外部振荡器时,该引脚接收振荡器的信号,既把此信号直接接到内部时钟发生器的输入端。

②XTAL2 接外部晶体的另一个引脚。在单片机内部,它是上述振荡器的反相放大器的输出端。采用外部振荡器时,此引脚应悬浮不连接。

(3) 控制或与其它电源复用引脚RST、ALE//PROG、/PSEN和/EA/VPP

①RST 复位输入端。 当振荡器运行时,在该引脚上出现两个机器周期的高电平将使单片机复位。

②ALE//PROG 当访问外部存储器时,ALE(地址锁存允许)的输出用于锁存地址的低位字节。即使不访问外部存储器,ALE端仍以不变的频率(此频率为振荡器频率的1/6)周期性地出现正脉冲信号。因此,它可用作对外输出的时钟,或用于定时目的。然而要注意的是:每当访问外部数据存储器时,将跳过一个ALE脉冲。在对Flash存储器编程期间,该引脚还用于输入编程脉冲(/PROG)。

③/PSEN 程序存储允许(/PSEN)输出是外部程序存储器的读选通信号。当AT89S52/LV52由外部程序存储器取指令(或常数)时,每个机器周期两次/PSEN有效(既输出2个脉冲)。但在此期间内,每当访问外部数据存储器时,这两次有效的/PSEN信号将不出现。

④/EA/VPP 外部访问允许端。要使CPU只访问外部程序存储器(地址为0000H~FFFFH),则/EA端必须保持低电平(接到GND端)。当/EA端保持高电平(接VSS端)时,CPU则执行内部程序存储器中的程序。

(4)输入/输出引脚 P0.0~P0.7、P1.0~P1.7、P2.0~P2.7 和P3.0~P3.7

①P0端口(P0.0~ P0.7) P0是一个8位漏极开路型双向I/O端口。作为输出口用时,每位能以吸收电流的方式驱动8个TTL输入,对端口写1时,又可作高阻抗输入端用。

②P1端口(P1.0~ P1.7) P1是一个带有内部上拉电阻的8位双向I/O端口。P1的输出缓冲器可驱动(吸收或输出电流方式)4个TTL输入。对端口写1时,通过内部的上拉电阻把端口拉到高电位,这时可用作输入口。作输入口时,因为有内部的上拉电阻,那些被外部信号拉低的引脚会输出一个电流。

③P2端口 (P2.0~P2.7) P2是一个带有内部上拉电阻的8位双向I/O端口。P2的输出缓冲器可驱动(吸收或输出电流方式)4个TTL输入。对端口写1时,通过内部的上拉电阻把端口拉到高电位,这时可用作输入口。P2作输入口使用时,因为有内部的上拉电阻,那些被外部信号拉低的引脚会输出一个电流。 ④P3端口(P3.0~P3.7) P3口管脚是8个带内部上拉电阻的双向I/O口,可接收输出4个TTL门电流。当P3口写入“1”后,它们被内部上拉为高电平,并用作输入。作为输入,由于外部下拉为低电平,P3口将输出电流,这是由于上拉的缘故。

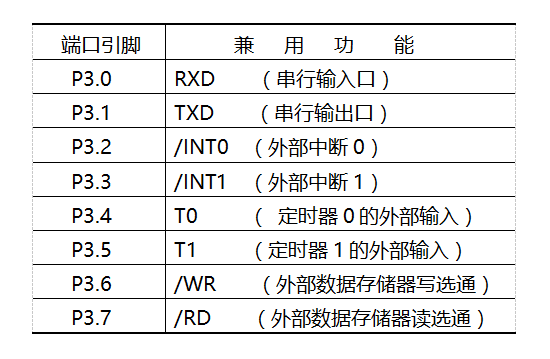

P3口也可作为AT89S52的一些特殊功能,这些特殊功能见表4-1。

(表4-1 P3端口的特殊功能)

-

电子万年历设计与制作资料2012-08-20 0

-

电子万年历设计2012-08-20 0

-

电子万年历2012-11-13 0

-

万年历威廉希尔官方网站 图2013-08-05 0

-

电子万年历带农历显示2015-01-08 0

-

万年历2016-03-20 0

-

万年历 仿真2016-07-08 0

-

求一种基于STM32的智能万年历设计方案2021-09-29 0

-

基于51单片机电子万年历论文2016-01-20 1095

-

电子万年历资料2016-05-03 689

-

毕业设计-电子万年历设计2016-11-03 1080

-

万年历protues仿真 实时时钟仿真 12864万年历仿真 52017-01-14 2505

全部0条评论

快来发表一下你的评论吧 !