LVPECL配置方式介绍

描述

前一篇文案介绍了LVDS,本篇介绍LVPECL(Low Voltage Positive Emitter Coupled Logi) 低压正射极耦合逻辑, 源自发射极耦合逻辑(ECL),采用正电源。

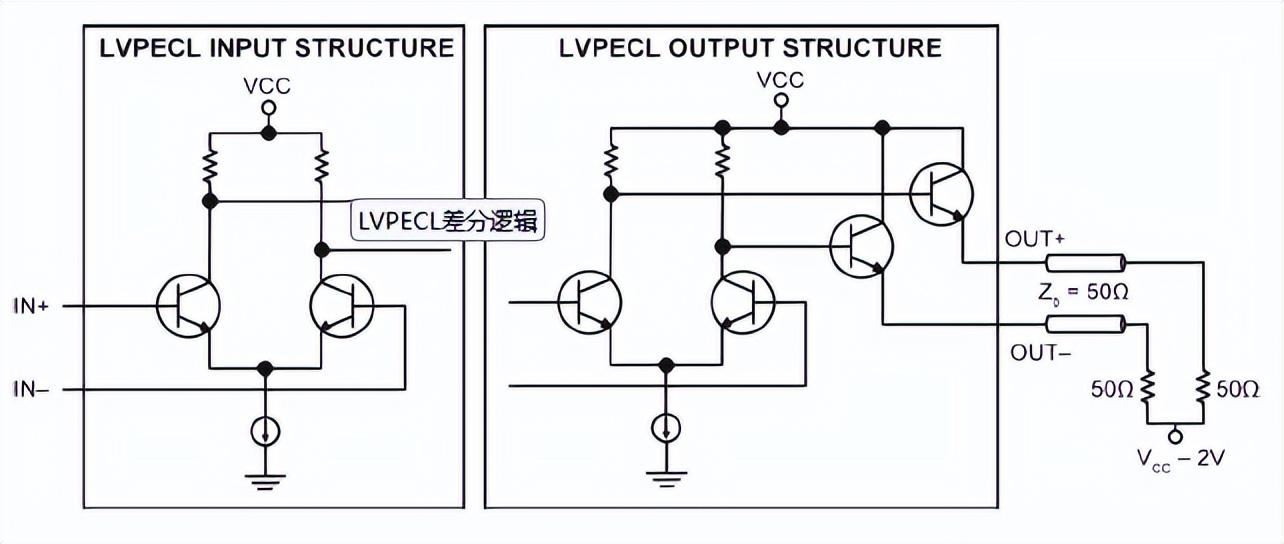

输入是具有高输入阻抗的电流开关差分对。

输出由差分对放大器组成,驱动一对射极跟随器。如下:

缺点是功耗相对较高以及有时需要提供单独的终接电压轨

技术能实现超过10Gbps的高数据率。

LVPECL输入与输出端功能框图

1.LVPECL内部工作原理

LVPECL差分输出端分别50Ω传输阻抗至Vcc-2V和输出总线OUT + / OUT-输出为中间电平为:Vcc-1.3V,导致近似的直流电流为14mA。

2.LVPECL端接匹配网络

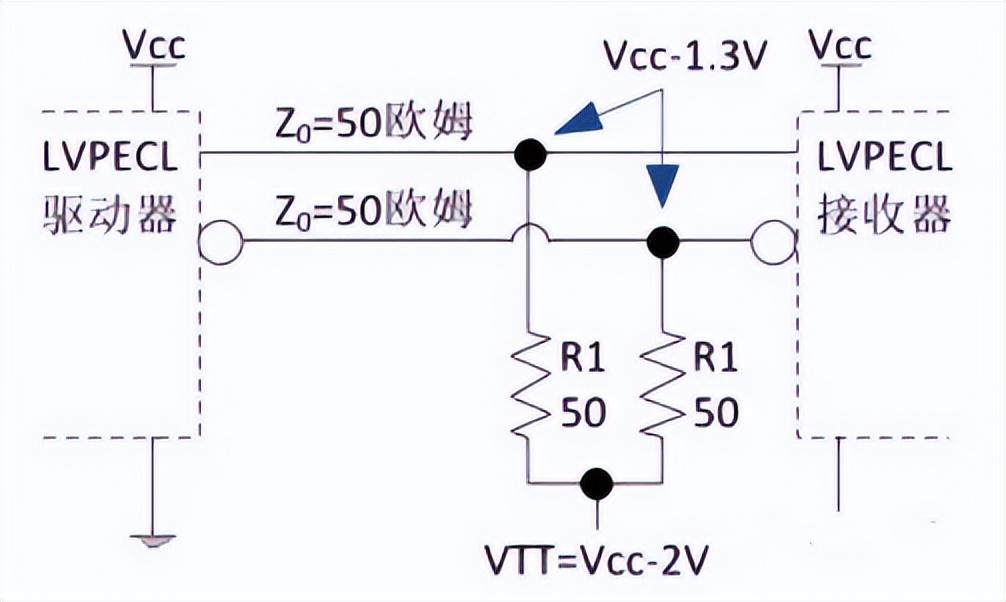

最简单的LVPECL匹配方式就是在接收器的输入侧需要一个参考电压:Vcc-2V,如下

典型配置方式

额外的电源需求会增加威廉希尔官方网站 的复杂度和成本,本案介绍几种常用端接方式(参见:浅谈LVDS、CML、LVPECL三种差分逻辑电平之间的互连-电子发烧友),如下为推荐:

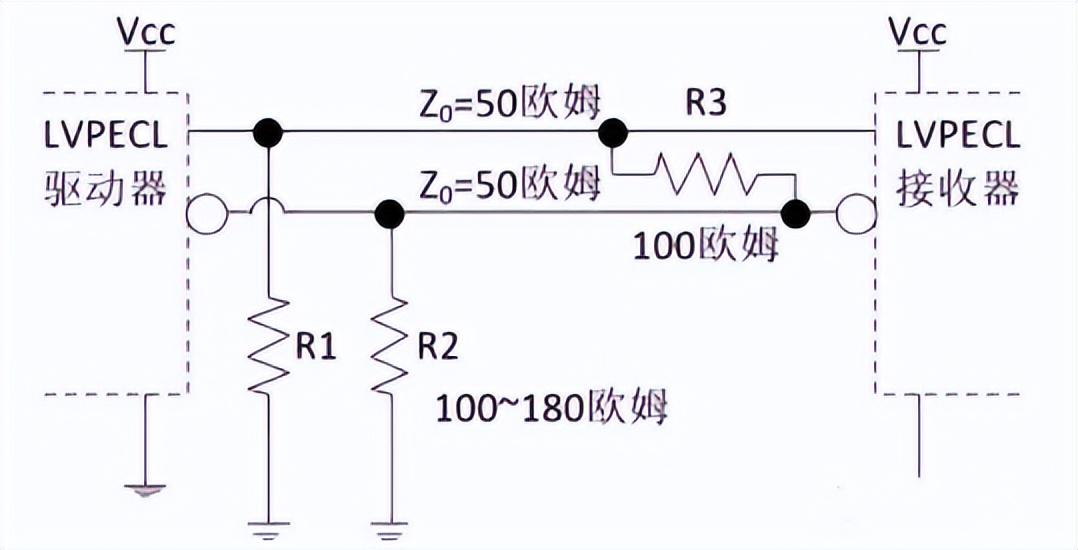

直流耦合三电阻方式

R1=140~200欧姆(Vcc:3.3V),R1=270~330欧姆(Vcc: 5V),R2=100欧姆。R1为输出门提供偏置电流,R2为交流信号提供匹配。输入门的直流电平偏置直接利用输出门的直流电平(Vcc-1.3V),并不需要外来的上下拉电阻来提供。R2一个电阻必须放在离输入门比较近的地方,R1放置的地方可以比较随便。

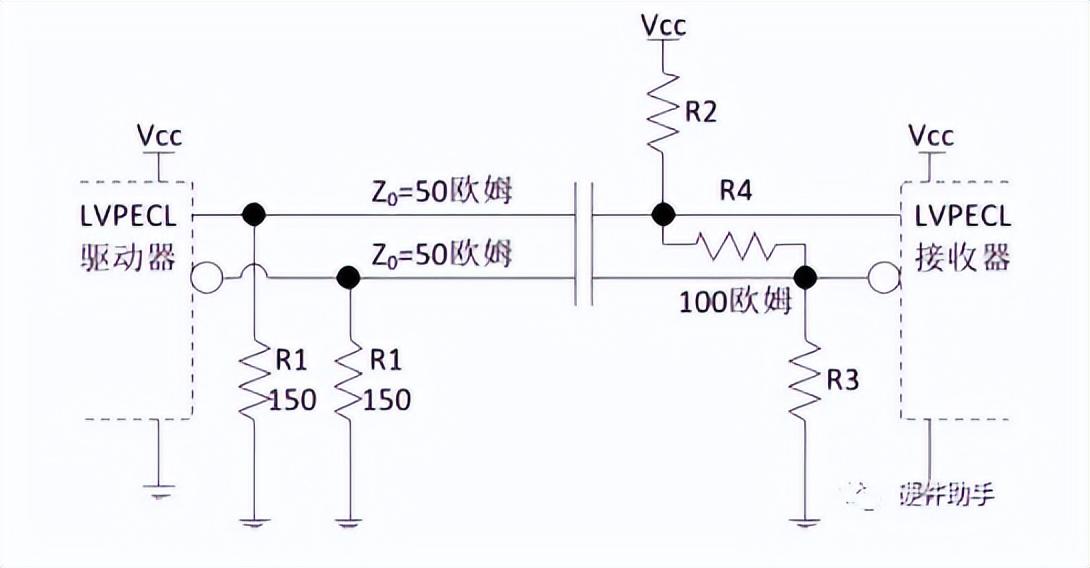

交流耦合

R1=140~200欧姆,属于直流偏置电阻。C1为耦合电容,可以放在线上的任何一个地方。R4=100欧姆,属于交流匹配电阻,一定要放在末端。R2、R3为K级别的电阻,必须满足R3/(R2+R3)=(VCC-1.3V)/VCC的比值就可以了,这两个电阻是为输入端提供直流电平,所以对PCB上的位置没有特殊要求。

-

如何将Virtex 5 LVPECL_25连接到另一个设备的3.3v lvpecl?2020-06-12 0

-

STM32F103封装方式与功能配置2016-08-03 21548

-

HMC6832a_LVPECL IBIS Model2021-03-11 508

-

DA3482的LVPECL输入接口威廉希尔官方网站 配置图,这里差分线分别连150欧的电阻接地有什么作用?2024-12-20 0

-

LVPECL驱动器终端设计介绍2019-07-08 0

-

如何使用BLVDS或其他驱动Kintex LVPECL输入的方法的信息?2020-07-19 0

-

LVPECL终端的设计考虑因素有哪些?2021-04-13 0

-

如果ad9680的clk和sysref信号采用lvpecl格式输入,交流耦合的话前端网络如何设计?2023-12-06 0

-

简谈PCIe的软件配置方式2019-07-29 7762

-

AD级联的工作方式配置和AD双排序的工作方式配置详细说明2019-12-23 1013

-

智能硬件产品有哪些_智能硬件网络配置方式2020-04-28 3748

-

设计LVPECL终端需要考虑那些原因2020-09-30 516

-

LVDS、CML、LVPECL不同逻辑电平之间的互连(二)2020-12-20 24910

-

HMC6832a_LVPECL IBIS模型2021-06-01 382

-

LVPECL与LVPECL之间是如何进行连接的?LVPECL到CML的连接?2023-08-28 2732

全部0条评论

快来发表一下你的评论吧 !