MOS晶体管漏电流的6个原因

描述

漏电流会导致功耗,尤其是在较低阈值电压下。了解MOS晶体管中可以找到的六种泄漏电流。

在讨论MOS晶体管时,短通道器件中基本上有六种类型的漏电流元件:

反向偏置PN结漏电流

亚阈值漏电流

漏极引起的屏障降低

V千 滚落

工作温度的影响

隧道进入和穿过栅极氧化层泄漏电流

热载流子从基板注入栅极氧化物引起的泄漏电流

栅极感应漏极降低 (GIDL) 引起的漏电流

在继续之前,请确保您熟悉 MOS晶体管的基本概念 这将使您为以下信息做好准备。

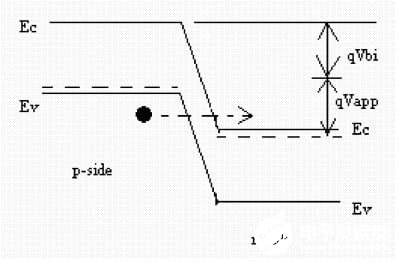

1. 反向偏置pn结漏电流

MOS晶体管中的漏极/源极和基板结在晶体管工作期间反向偏置。这会导致器件中出现反向偏置漏电流。这种漏电流可能是由于反向偏置区域中少数载流子的漂移/扩散以及雪崩效应引起的电子-空穴对的产生。pn结反向偏置漏电流取决于掺杂浓度和结面积。

对于漏极/源极和衬底区域的重掺杂pn结,带间隧穿(BTBT)效应主导反向偏置漏电流。在带间隧穿中,电子直接从p区的价带隧穿到n区的导带。BTBT对于大于10的电场可见6 V/厘米。

图 1.

MOS 晶体管反向偏置 pn 结中的带间隧穿。所有图片均由 K.Roy 等人提供,“

深亚微米 CMOS 威廉希尔官方网站 中的泄漏电流机制和泄漏减少技术

”;过程。 IEEE,卷。 91,第 2 期,2003 年 2 月。

请注意,在本文的上下文中,我们将隧道现象定义为即使电子能量远小于势垒时也会发生。

2.亚阈值漏电流

当栅极电压小于阈值电压(V千)但大于零,则称晶体管偏置在亚阈值或弱反转区域。在弱反演中,少数载体的集中度很小,但不为零。在这种情况下,对于 |VDS|>0.1V,整个压降发生在漏极-基板pn结两端。

漏极和源极之间的电场分量,平行于Si-SiO2 接口,很小。由于这种可忽略不计的电场,漂移电流可以忽略不计,亚阈值电流主要由扩散电流组成。

漏极诱导屏障降低 (DIBL)

亚阈值漏电流主要是由于漏极引起的势垒降低或DIBL。在短通道器件中,漏极和源极的耗尽区域相互作用,降低了源极处的潜在屏障。然后,源极能够将电荷载流子注入通道表面,从而产生亚阈值漏电流。

DIBL在高漏极电压和短通道器件中很明显。

V千 滚落

由于通道长度缩短,MOS器件的阈值电压降低。这种现象称为V千 滚降(或阈值电压滚降)。在短通道器件中,漏极和源极耗尽区域进一步进入通道长度,耗尽一部分通道。

因此,需要较低的栅极电压来反相通道,从而降低阈值电压。对于较高的漏极电压,这种现象很明显。阈值电压的降低会增加亚阈值漏电流,因为亚阈值电流与阈值电压成反比。

工作温度的影响

温度在漏电流中也起着一定的作用。阈值电压随着温度的升高而降低。或者,换句话说,亚阈值电流随着温度的升高而增加。

3. 隧道进入和穿过栅极氧化层泄漏电流

在短通道器件中,薄栅氧化层会导致SiO两端的高电场2 层。低氧化物厚度和高电场导致电子从基板隧穿到栅极,从栅极隧穿到栅极氧化物从栅极到基板,从而产生栅极氧化物隧穿电流。

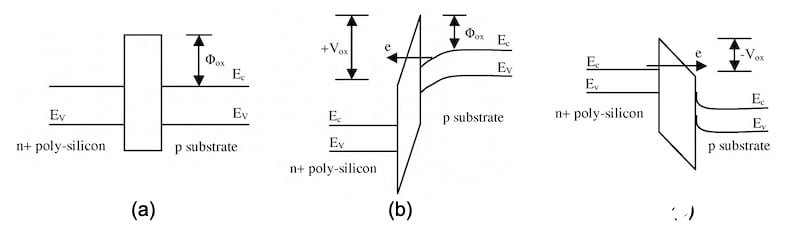

考虑如图所示的能量带图。

图2.

MOS晶体管的能带图

(一)

平带,

(二)

正栅极电压,以及

(三)

负栅极电压

第一张图,图2(a),是一个扁平带MOS晶体管,即其中没有电荷。

当栅极端子正偏置时,能量带图发生变化,如图2(b)所示。强倒置表面隧道中的电子进入或通过SiO的隧道2 产生栅极电流的层。

另一方面,当施加负栅极电压时,电子从n+多晶硅栅极隧道进入或通过SiO。2 产生栅极电流的层,如图2(c)所示。

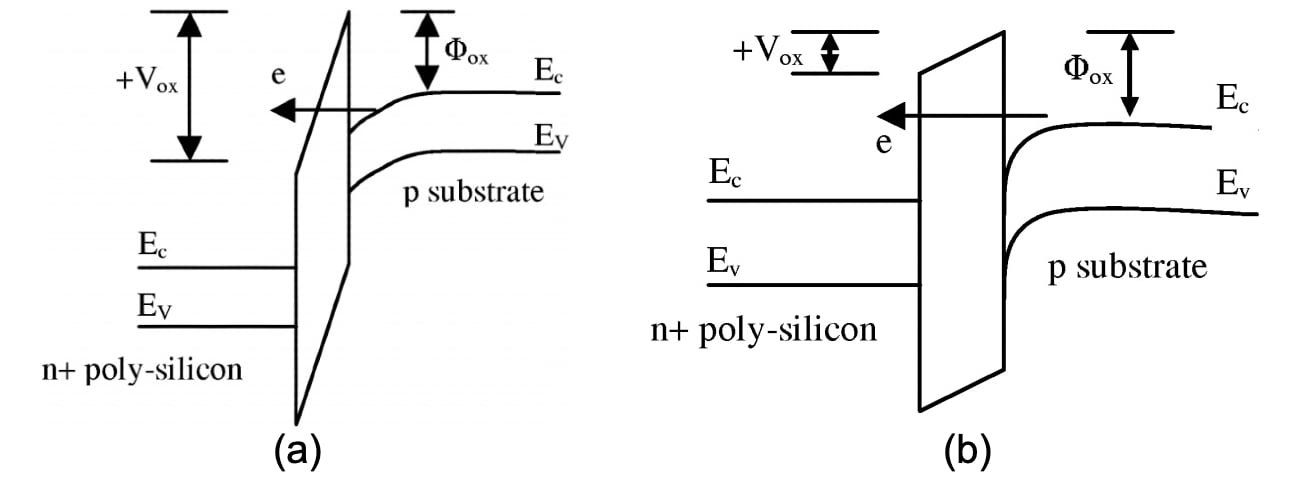

福勒-诺德海姆隧道和直接隧道

栅极和基板之间主要有两种类型的隧道机制。它们是:

福勒-诺德海姆隧道,其中电子隧道穿过三角形势垒

直接隧穿,电子穿过梯形势垒

图3.

显示能量带图

(一)

福勒-诺德海姆隧道穿过氧化物的三角形势垒和

(二)

通过氧化物的梯形电位势垒直接隧道

您可以在上面的图3(a)和3(b)中看到两种隧道机制的能量带图。

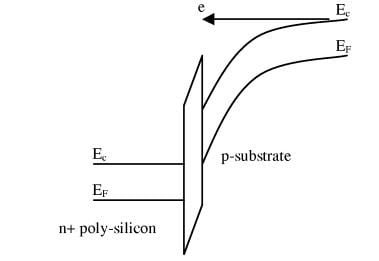

4. 热载流子从基板注入栅极氧化物引起的泄漏电流

在短通道器件中,基底氧化物界面附近的高电场激励电子或空穴,它们穿过衬底氧化物界面进入氧化层。这种现象被称为热载体注入。

图4.

描述电子由于高电场而获得足够能量并越过氧化物势垒电位(热载流子注入效应)的能量带图

这种现象比空穴更容易影响电子。这是因为与空穴相比,电子的有效质量和屏障高度较小。

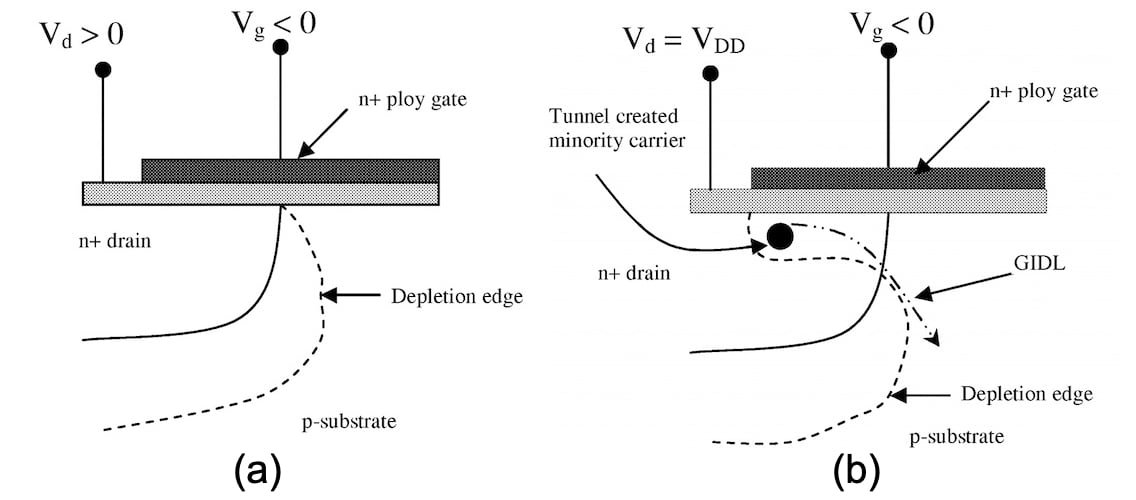

5. 栅极感应漏极降低(GIDL)引起的漏电流

考虑具有p型衬底的NMOS晶体管。当栅极端子处有负电压时,正电荷仅在氧化物-衬底界面处积聚。由于基板上累积的空穴,表面表现为比基板掺杂更多的p区。

这导致沿排水基板界面的表面耗尽区域更薄(与块体中耗尽区域的厚度相比)。

图5.

(一)

沿表面在排水-基底界面处形成薄耗尽区和

(二)

由雪崩效应和BTBT产生的载流子引起的GIDL电流

由于稀薄的耗尽区域和较高的电场,会发生雪崩效应和带间隧穿(如本文第一部分所述)。因此,栅极下方漏极区域中的少数载流子产生,并通过负栅极电压推入基板。这会增加漏电流。

6. 穿孔效应引起的漏电流

在短通道器件中,由于漏极和源极靠近,两个端子的耗尽区会聚集在一起并最终合并。在这种情况下,据说发生了“穿孔”。

穿通效应降低了大多数载体从源头上的潜在障碍。这增加了进入基板的载流子数量。其中一些载流子被漏极收集,其余的则产生漏电流。

您现在应该熟悉与MOS晶体管相关的六种泄漏电流。如果您对这些概念有其他疑问,请在下面发表评论。

-

概述晶体管2019-05-05 0

-

3.3v,100mA电源开关控制用晶体管还是MOS管?2019-10-23 0

-

MOS管的漏电流是什么意思2021-09-28 0

-

MOS管的漏电流2021-10-12 0

-

什么是晶体管 晶体管的分类及主要参数2023-02-03 0

-

MOS晶体管2009-11-05 3724

-

MOS晶体管的应用2019-04-19 7725

-

浅析MOS 晶体管的核心概念2023-03-24 2627

-

探究MOS晶体管中各种类型的泄漏电流的原因2023-03-24 8925

-

了解短通道MOS晶体管中的漏电流元件2023-05-03 1752

-

MOS晶体管中各种类型的泄漏电流的原因2023-10-31 2129

-

MOS管中漏电流产生的主要六大原因2024-03-27 5436

-

MOS管泄漏电流的类型和产生原因2024-10-10 1849

-

MOS管泄漏电流,各种漏电流及减小泄露方法介绍2024-11-19 619

全部0条评论

快来发表一下你的评论吧 !