一文浅析半导体后端工艺

制造/封装

描述

半导体制作工艺可分为前端和后端:前端主要是晶圆制作和光刻(在晶圆上绘制威廉希尔官方网站 );后端主要是芯片的封装。随着前端工艺微细化技术逐渐达到极限,后端工艺的重要性愈发突显。作为可以创造新附加价值的核心突破点,其技术正备受瞩目。

此系列文章将以《提高半导体附加价值的封装与测试》一书内容为基础,详细讲解后端工艺。

#1 半导体后端工艺

制作半导体产品的第一步,就是根据所需功能设计芯片(Chip)。然后,再将芯片制作成晶圆(Wafer)。由于晶圆由芯片反复排列而成,当我们细看已完成的晶圆时,可以看到上面有很多小格子状的结构,其中一个小格子就相当于一个芯片。芯片体积越大,每个晶圆可产出的芯片数量就越少,反之亦然。

半导体设计不属于制程工序,半导体产品的制程工序大体可分为晶圆制作、封装和测试。其中,晶圆制作属于前端(Front End)工艺;封装和测试属于后端(Back End)工艺。晶圆的制作工艺中也会细分前端和后端,通常是CMOS制程工序属于前端,而其后的金属布线工序属于后端。

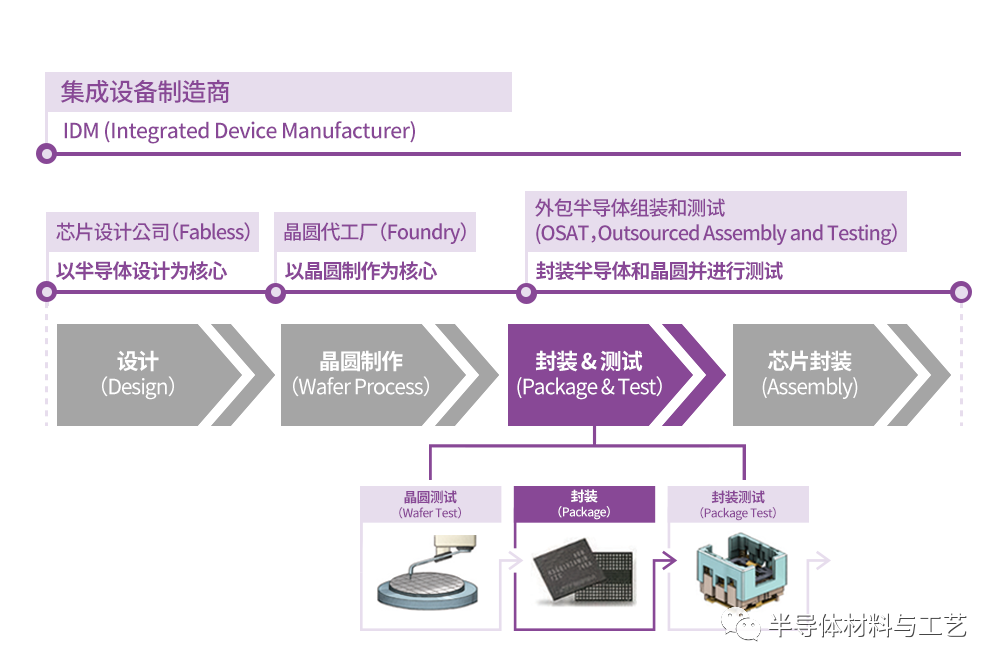

▲ 图1:半导体制作流程与半导体行业划分(ⓒHANOL出版社/photograph.SENSATA)

图1展示了半导体制程工艺及其行业的划分。只从事半导体设计的产业运作模式被称作芯片设计公司(Fabless),该模式的典型代表有高通(Qualcomm)、苹果(Apple)等。负责晶圆制作的制造商被称为晶圆代工厂(Foundry),他们根据Fabless公司的设计制作晶圆,其中最典型的代表要台积电(TSMC)了,DB HiTek、Magnachip等韩企也采用这一模式。经Fabless设计和Foundry制造的晶圆还需经过封装和测试,专门负责这两道工艺的企业就是外包半导体组装和测试(OSAT,Outsourced Assembly and Testing),其典型代表有ASE、JCET、星科金朋(Stats Chippac)、安靠(Amkor)等。此外,还有像SK海力士这样集半导体设计、晶圆制造、封装和测试等多个产业链环节于一身的集成设备制造商(IDM,Integrated Device Manufacturer)。

如图1所示,封装和测试工艺的第一步就是晶圆测试。封装后,再对封装进行测试。

半导体测试的主要目的之一就是防止不良产品出厂。一旦向客户提供不良产品,客户对我们的信任就会大打折扣,进而导致公司销售业绩的下降,还会引发赔偿等资金上的损失。因此,我们必须在产品出厂前对其进行细致的全面检测。半导体测试须根据产品的各种特性,对其各参数进行测试,以确保产品的品质和可靠度。当然,这需要时间、设备和劳动力上的投入,产品的制造成本也会随之增加。因此,众多测试工程师正致力于减少测试时间和测试参数。

#2 测试的种类

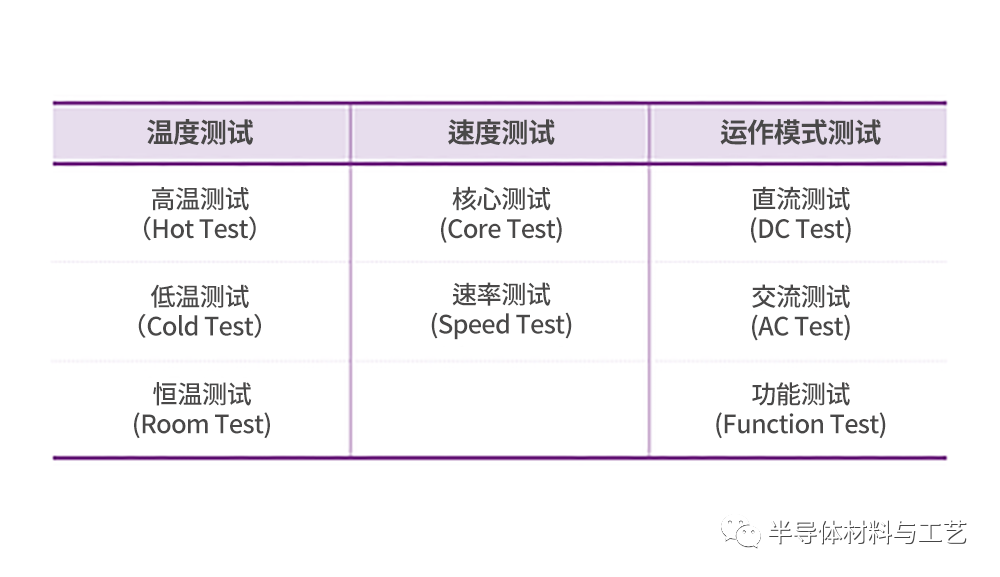

▲ 表1: 测试分类(ⓒ HANOL出版社)

测试工艺可依据不同的测试对象,分为晶圆测试和封装测试;也可根据不同的测试参数,分为温度、速度和运作模式测试等三种类型(见表1)。

温度测试以施加在试验样品上的温度为标准:在高温测试中,对产品施加的温度比产品规格1 所示温度范围的上限高出10%;在低温测试中,施加温度比规格下限低10%;而恒温测试的施加温度一般为25℃。在实际使用中,半导体产品要在各种不同的环境中运作,因此必须测试产品在不同温度下的运作情况以及其温度裕度(Temperature Margin)。以半导体存储器为例,高温测试范围通常为85~90℃,低温测试范围为-5~-40℃。

1 规格(Spec): specification的缩写,指产品配置,即制造产品时在设计、制作方法上或对所需特性的各种规定。

速度测试又分为核心(Core)测试和速率测试。核心测试主要测试试验样品的核心运作,即是否能顺利实现原计划的目标功能。以半导体存储器为例,由于其主要功能是信息的存储,测试的重点便是有关信息存储单元的各项参数。速率测试则是测量样品的运作速率,验证产品是否能按照目标速度运作。随着对高速运转半导体产品需求的增加,速率测试目前正变得越来越重要。

运作模式测试细分为直流测试(DC Test)、交流测试(AC Test)和功能测试(Function Test):直流测试验证直流电流和电压参数;交流测试(AC Test)验证交流电流的规格,包括产品的输入和输出转换时间等运作特性;功能测试则验证其逻辑功能是否正确运作。以半导体存储器为例,功能测试就是指测试存储单元(Memory cell)与存储器周围威廉希尔官方网站 逻辑功能是否能正常运作。

#3 晶圆测试

晶圆测试的对象是晶圆,而晶圆由许多芯片组成,测试的目的便是检验这些芯片的特性和品质。为此,晶圆测试需要连接测试机和芯片,并向芯片施加电流和信号。

完成封装的产品会形成像锡球(Solder Ball)一样的引脚(Pin),利用这些引脚可以轻而易举完成与测试机的电气连接。但在晶圆状态下,连接两者就需要采取一些特殊的方法,比如探针卡(Probe Card)。

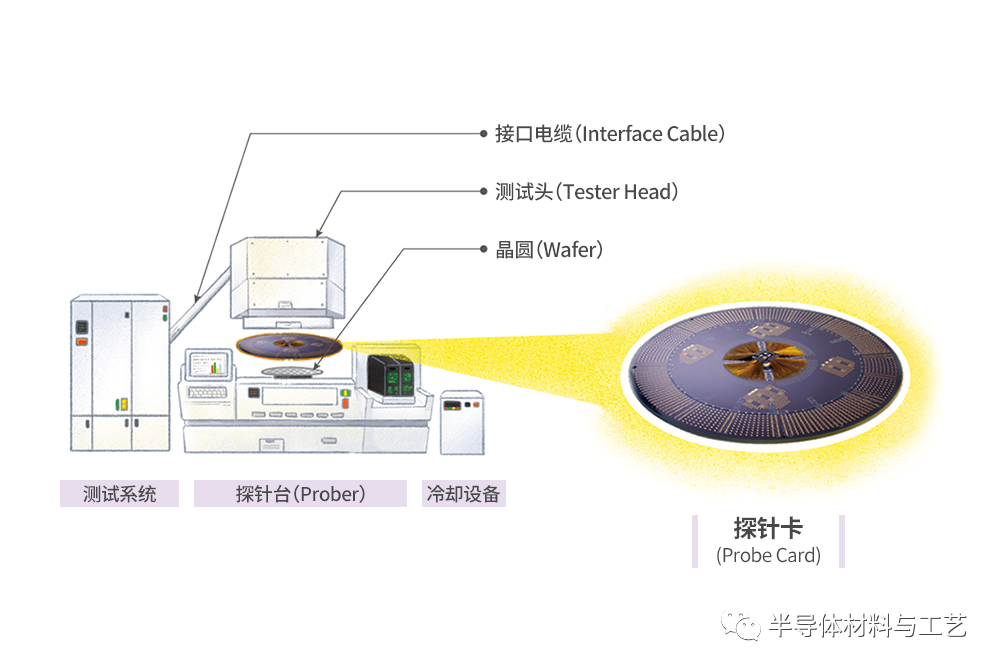

如图2所示,探针卡是被测晶圆和测试机的接口,卡上有很多探针2可以将测试机通讯接口和晶圆的焊盘直接连接起来,卡内还布置了很多连接探针与测试机的连接线材。探针卡固定在测试头上,晶圆探针台通过使探针卡与晶圆焊盘点精准接触,完成测试。

2 探针: 与晶圆焊盘进行电气连接和直接接触的针状物。

▲ 图2 : 晶圆测试系统模式图(ⓒ HANOL出版社/photograph.Formfactor)

将晶圆正面朝上装载后,再把图2右侧的探针卡反过来使针尖朝下,实现与晶圆焊盘的准确对位。这时,温度调节设备根据测试所需温度条件,施加相应温度。测试系统通过探针卡传送电流和信号,并导出芯片讯号,从而读取测试结果。

探针卡要根据被测芯片的焊盘布局和晶圆芯片排布制作,即探针与被测晶圆焊盘布局要一致。而且,要按照芯片排列,反复排布探针。其实,在实际操作中,仅凭一次接触是无法测试晶圆的所有芯片的。因此,在实际量产过程中要反复接触2~3次。

一般来讲,晶圆测试依次按照“电气参数监控(EPM) → 晶圆老化(Wafer Burn in) → 测试 → 维修(Repair) → 测试”顺序进行。下面,我们来详细讲解一下晶圆测试的具体工序。

◎ 电气参数监控(EPM,Electrical Parameter Monitoring)

测试可以筛选出不良产品,又可以反馈正在研发或量产中的产品缺陷,从而进行改善。相比而言,电气参数监控的主要目的是后者,即通过评价分析产品单位元件的电气特性,对晶圆的制作工序提供反馈。具体来说,就是在进入正式晶圆测试前,采用电学方法测量晶体管的特性和接触电阻,验证被测产品是否满足设计和元件部门提出的基本特性。从测试的角度来看,就是利用元件的电学性能提取直流参数(Parameter),并监控各单位元件的特性。

◎ 晶圆老化(Wafer Burn in)

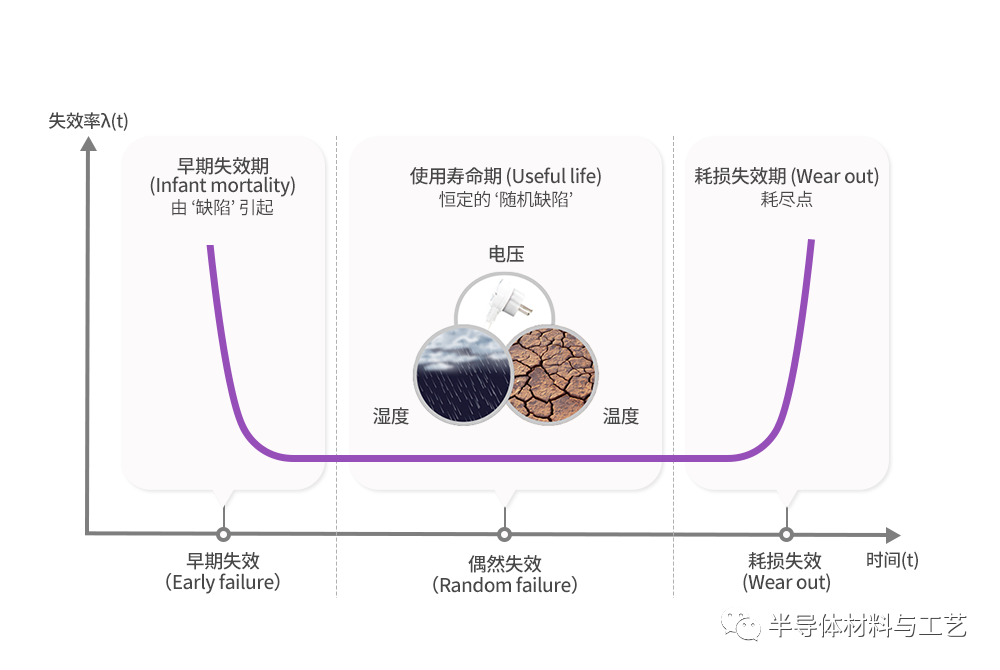

▲ 图3:产品使用时间与不良率(ⓒ HANOL出版社)

图3以时间函数揭示了产品生命周期中的不良率 [曲线呈现出如同浴缸的形状,故被称作浴盆曲线(Bath-Tub Curve)] :早期失效(Early failure)期,产品因制作过程中的缺陷所导致的失效率较高;制造上的缺陷消失后,产品进入偶然失效(Random failure)期,在此期间,产品的失效率降低;产品老化磨损后进入耗损(Wear out)失效期,失效率明显再次上升。可见,如果完成产品后立即提供给客户,早期失效会增加客户的不满,造成退货等产品问题的可能性也很大。

“老化(Burn in)”的目的就是为识别产品的潜在缺陷,提前发现产品的早期失效状况。晶圆老化是在晶圆产品上施加温度、电压等外界刺激,剔除可能发生早期失效的产品的过程。

◎ 晶圆测试

在晶圆老化(Wafer Burn in)测试剔除早期失效产品后使用探针卡进行晶圆测试。晶圆测试是在晶圆上测试芯片电学性能的工序。其主要目的包括:提前筛选出不良芯片、事先剔除封装/组装3过程中可能产生的不良产品并分析其原因、提供工序反馈信息,以及通过晶圆级验证(Wafer Level Verification)提供元件与设计上的反馈等。

在晶圆测试中筛选出的部分不良单元4,将会在我们下面要讲到的维修(Repair)过程中被备用单元(Redundancy cell)替换。为测试这些备用单元是否能正常工作,以及芯片能否成为符合规格的良品,在维修工序后,必须重新进行一次晶圆测试。

3 组装 : 与基板或系统实现电气或直接连接、组装的工序;

4单元(Cell): 为在记忆元件存储信息(Data)所需的最小单位的单元数组;DRAM存储单元(Cell)由一个晶体管(Transistor)和一个电容器(Capacitor)组成;

◎ 维修(Repair)

维修作为内存半导体测试中的一道工序,是通过维修算法(Repair Algorithm),以备用单元取代不良单元的过程。假设在晶圆测试中发现DRAM 256bit内存的其中1bit为不良,该产品就成了255bit的内存。但如果经维修工序,用备用单元替换不良单元,255bit的内存就又重新成了256bit的内存,可以向消费者正常销售。可见,维修工序可以提高产品的良率,因此,在设计半导体存储器时,会考虑备用单元的制作,并根据测试结果以备用单元取代不良单元。当然,制作备用单元就意味着要消耗更多的空间,这就需要加大芯片的面积。因此,我们不可能制作可以取代所有不良内存的充足的备用单元(比如可以取代所有256bit的备用256bit等)。要综合考虑工艺能力,选择可以最大程度地提升良率的数量。如果工艺能力强,不良率少,便可以少做备用单元,反之则需要多做。

维修可分为列(Column)单位和行(Row)单位:备用列取代不良单元所在的列;备用行取代不良单元所在的行。

DRAM的维修要先切断不良单元的列或行,再连接备用列或行。维修可分为激光维修和电子保险丝(e-Fuse)维修。激光维修,顾名思义,就是用激光烧断与不良单元的连接。这要求先脱去晶圆焊盘周围连线的保护层(Passivation layer),使连接线裸露出来。由于完成封装后的芯片表面会被各种封装材料所包裹,激光维修方法只能用于晶圆测试。电子保险丝维修则采用在连接线施加高电压或电流的方式断开不良单元。这种方法与激光维修不同,它通过内部威廉希尔官方网站 来完成维修,不需要脱去芯片的保护膜。因此,除晶圆测试外,该方法在封装测试中也可使用。

#4 封装测试

在晶圆测试中被判定为良品的芯片,经封装工序后需要再进行封装测试,因为这些芯片在封装工序中有可能发生问题。而且,晶圆测试同时测试多个芯片,测试设备性能上的限制可能导致其无法充分测试目标参数。与此相反,封装测试以封装为单位进行测试,对测试设备的负荷相对较小,可以充分测试目标参数,从而选出符合规格的良品。

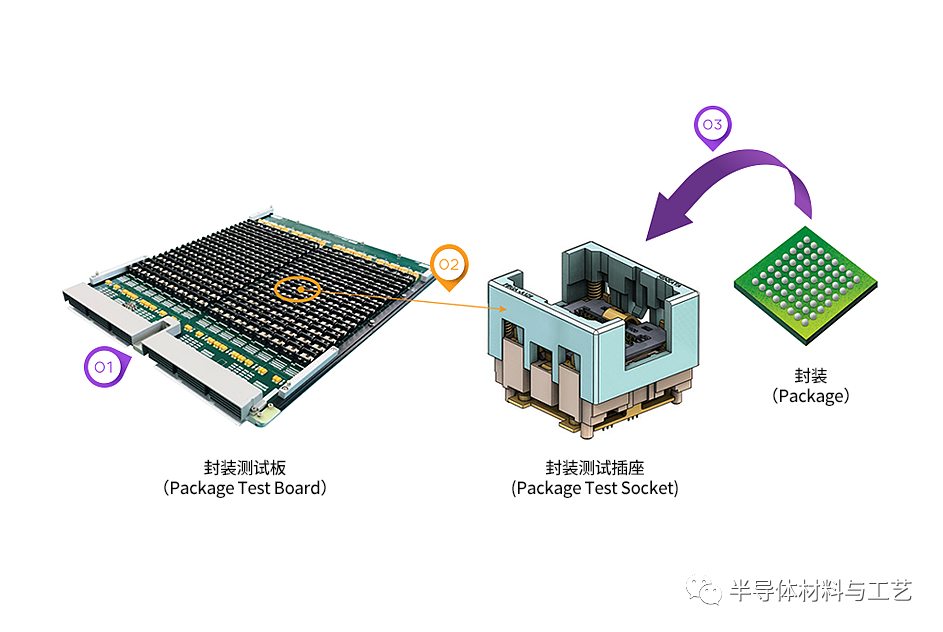

封装测试方法如图4所示:先把“03”的封装引脚(Pin,图中为锡球)朝下装入封装测试插座内,使引脚与插座内的引脚对齐,然后再将封装测试插座固定到封装测试板(Package Test Board)上进行测试。

▲ 图4:封装测试系统(ⓒHANOL出版社/ photograph.NST, SENSATA)

◎ 老化测试(Test During Burn In,TDBI)

前边也提到过,“老化(Burn in)”是为了提前发现产品的早期失效,向晶圆产品施加温度、电压等外界刺激的工序。这一工序既可在晶圆测试中进行,也可在封装测试阶段进行。封装后实施的“老化”被称为老化测试(TDBI)。大部分半导体产品在晶圆和封装测试均进行老化测试,以便更加全面地把握产品的特性,寻找缩减老化时间和工序数量的条件。可见,老化对于量产来说是一道最有效的工序。

◎ 测试

这是验证数据手册5中定义的运作模式在用户环境中能否正常工作的流程。通过温度测试,检验产品交流/直流参数的缺陷,以及单元&外围威廉希尔官方网站 (Cell & Peri)区域的运作是否满足客户要求的规格。此时,需要在比数据手册中规定的条件更为恶劣的条件下,甚至是最糟糕的条件下进行测试。

5 数据手册(Data Sheet):定义半导体产品基本配置与特性等具体信息的文件。

◎ 外观(Visual)检测

完成所有测试后,需通过激光打标(Laser Marking)把测试结果和速率特性(尤其是需要区分速率时)记录在产品封装的表面。经封装测试和激光打标后,将良品装入封装托盘(Tray),产品即可出厂了。当然,在出厂前,还要进行最后一道测试——外观测试,以剔除外观上的缺陷。外观检测主要查看是否有龟裂、打标错误、装入错误的托盘等问题;锡球方面主要检查球是否被压扁,或球是否脱落等问题。

编辑:黄飞

-

有关半导体工艺的问题2009-09-16 0

-

半导体工艺讲座2009-11-18 0

-

芯片制造-半导体工艺制程实用教程2009-11-18 0

-

[课件]半导体工艺2012-02-26 0

-

半导体器件与工艺2012-08-20 0

-

半导体工艺2012-08-20 0

-

《半导体制造工艺》学习笔记2012-08-20 0

-

浅析化合物半导体技术2019-06-13 0

-

半导体工艺技术的发展趋势2019-07-05 0

-

半导体工艺几种工艺制程介绍2020-12-10 0

-

半导体光刻蚀工艺2021-02-05 0

-

半导体后端工艺:了解半导体测试(上)2023-07-24 1848

-

【半导体后端工艺:】第一篇了解半导体测试2023-11-24 1274

-

半导体后端工艺:封装设计与分析2024-02-22 1158

全部0条评论

快来发表一下你的评论吧 !