串行FIR滤波器MATLAB与FPGA实现

描述

前言

本文介绍了设计滤波器的FPGA实现步骤,并结合杜勇老师的书籍中的串行FIR滤波器部分进行一步步实现硬件设计,对书中的架构做了简单的优化,并进行了仿真验证。

FIR滤波器的FPGA实现步骤

从工程角度分析FIR滤波器的FPGA实现步骤如下:

- 分析设计需求,根据设计需求确定FIR滤波器的仿真算法设计。

- 编写仿真代码或利用工具生成相关设计文件(包括但不局限与c++、MATLAB、python等语言或者相关滤波器设计工具)

- 量化滤波器系数,防止运算时数据溢出造成错误。

- 根据实际工程需求确定硬件实现架构并编写代码。

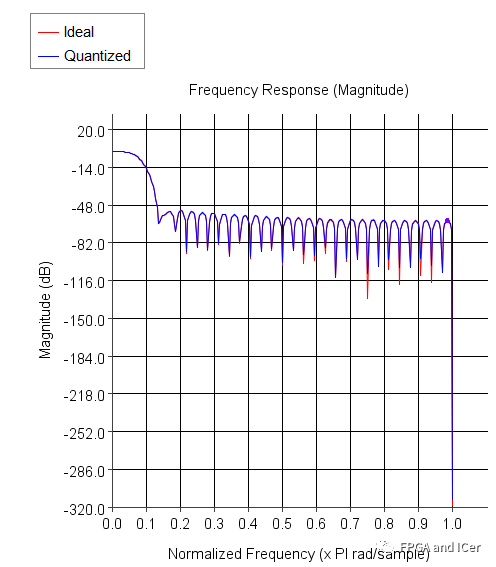

量化滤波器系数的影响

量化位数对滤波器的阻带纹波有较大的影响,且量化位数越高,则影响越小。下面给出两个之前设计的FIR IP工程中量化效果的截图,从图中可以很清楚看出,当量化位数不够,也就是量化精度不够时,对阻带影响较大,使用量化效果不好的滤波器可能造成滤波效果不能达到预期效果。

量化精度不够

正常量化

串行FIR滤波器FPGA实现

FIR滤波器的结构形式时,介绍了直接型、级联型、频率取样型和快速卷积型4种。在FPGA实现时,最常用的是最简单的直接型结构。FPGA实现直接型结构的FIR滤波器,可以采用串行结构、并行结构等不同中的结构设计,本节主要介绍在vivado环境下进行串行FIR滤波器设计的结构实现,同样仿造杜勇老师的《数字滤波器的MATLAB与FPGA实现》的书中的设计需求去一步步搭建工程并实现。

实现串行FIR滤波器滤波器需求

设计一个15阶(长度为16)的低通线性相位FIR滤波器,采用窗函数设计,截止频率为500 Hz,采样频率为2 000 Hz;采用FPGA实现全串行结构的滤波器,系数的量化位数为12比特,输入数据位宽为12比特,输出数据位宽为29比特,系统时钟为16 kHz。

滤波器系数确定与量化

确定滤波器的结构后,就根据滤波器进行设计代码仿真,这里引用书中的仿真设计,并将滤波器参数系数量化。 确定滤波器系数的方法有很多,可以使用MATLAB中丰富的函数实现,或者使用相关滤波器设计的软件工具,定制满足当前需求的窗函数的滤波器系数。

N=16; %滤波器长度

fs=2000; %采样频率

fc=500; %低通滤波器的截止频率

B=12; %量化位数

%生成各种窗函数

w_kais=blackman(N)';

%采用fir1函数设计FIR滤波器

b_kais=fir1(N-1,fc*2/fs,w_kais);

%量化滤波器系数

Q_kais=round(b_kais/max(abs(b_kais))*(2^(B-1)-1))

hn=Q_kais;

%转化成16进制数补码

Q_h=dec2hex(Q_kais+2^B*(Q_kais<0))

%求滤波器的幅频响应

m_kais=20*log(abs(fft(b_kais,1024)))/log(10); m_kais=m_kais-max(m_kais);

Q_kais=20*log(abs(fft(Q_kais,1024)))/log(10); Q_kais=Q_kais-max(Q_kais);

%设置幅频响应的横坐标单位为Hz

x_f=[0:(fs/length(m_kais)):fs/2];

%只显示正频率部分的幅频响应

m5=m_kais(1:length(x_f));

m6=Q_kais(1:length(x_f));

%绘制幅频响应曲线

plot(x_f,m5,'-',x_f,m6,'--');

xlabel('频率(Hz)');ylabel('幅度(dB)');

legend('未量化','12bit量化');

grid;

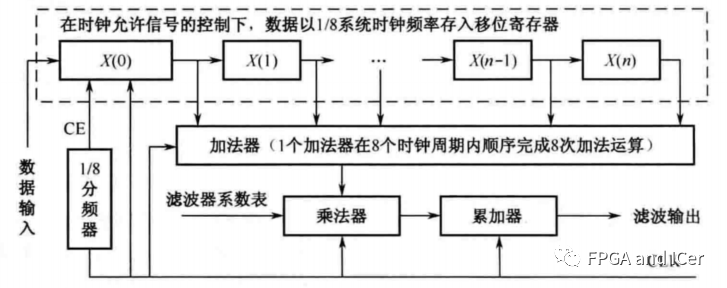

硬件架构

下图为杜勇老师的《数字滤波器的MATLAB与FPGA实现》实现的串行FIR滤波器的结构图。 因为FIR滤波器参数对称,所以同时计算相应的对称结构的值,所以针对长度为16的滤波器只需要计算8次即可出结果,图中的8个时钟周期可以替换成N/2;这样就得到了一个通用化的串行FIR滤波器结构图。

串行FIR滤波器结构

串行实现FIR滤波器,可以节约加法器资源,同时牺牲了整个滤波器实现的性能,缺点也就很明显了,当滤波器的系数长度N增大时,该数据吞吐的速率也将对应变成1/N。

根据架构描述威廉希尔官方网站

杜勇老师书中提供的代码相当繁琐,而且不具有通用化的使用价值(串行FIR使用价值确实不大,可能只用于学习),我根据上述的硬件设计的架构对代码进行了重写配置,使得代码更具有通用意义,可根据参数输入来适配不同滤波器长度的设计。

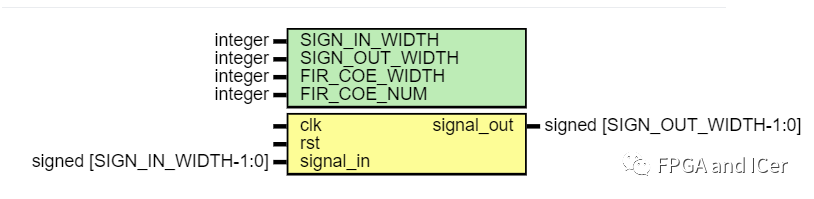

实现模块框图

接口描述如下:

接口描述

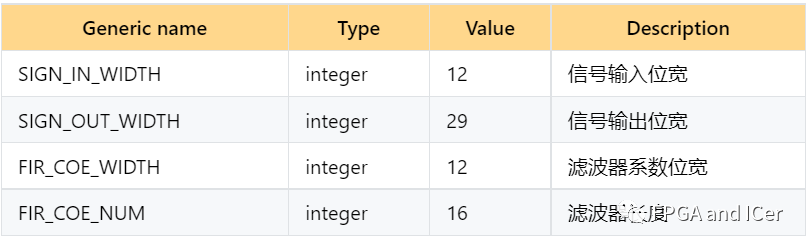

参数描述如下:

参数描述

代码如下:

`timescale 1ns / 1ps

module Fir_FullSerial(

input clk,//!系统时钟

input rst,//!复位信号

input signed [SIGN_IN_WIDTH-1:0] signal_in,//!信号输入

output signed [SIGN_OUT_WIDTH-1:0] signal_out//!信号输出,信号输出速度为CLK/FIR_COE_NUM

);

//

parameter integer SIGN_IN_WIDTH = 12 ;//!信号输入位宽

parameter integer SIGN_OUT_WIDTH = 29 ;//!信号输出位宽

parameter integer FIR_COE_WIDTH = 12 ;//!滤波器系数位宽

parameter integer FIR_COE_NUM = 16 ;//!滤波器长度

localparam integer FIR_WIDTH_DIV_2 = FIR_COE_NUM/2 ;

function [FIR_COE_WIDTH-1:0] coe_data;

input [FIR_WIDTH_DIV_2-1:0] index;

begin

case(index)

'd0:coe_data='h000;

'd1:coe_data='hffd;

'd2:coe_data='h00f;

'd3:coe_data='h02e;

'd4:coe_data='hf8b;

'd5:coe_data='hef9;

'd6:coe_data='h24e;

'd7:coe_data='h7ff;

endcase

end

endfunction

//!寄存输入信号

reg [SIGN_IN_WIDTH-1:0] Sign_in_Reg[FIR_COE_NUM-1:0];

//!计数器逻辑

reg [FIR_WIDTH_DIV_2-1:0] cnt;

always @(posedge clk ) begin

if (rst=='b1) begin

cnt<='d0;

end

else begin

if (cnt==FIR_WIDTH_DIV_2-'b1) begin

cnt <= 0;

end

else begin

cnt <= cnt + 1;

end

end

end

//将数据存入移位寄存器sign_in_Reg中

integer i;

always @(posedge clk)begin

if (rst=='b1)begin

//初始化寄存器值为0

for (i=0; i

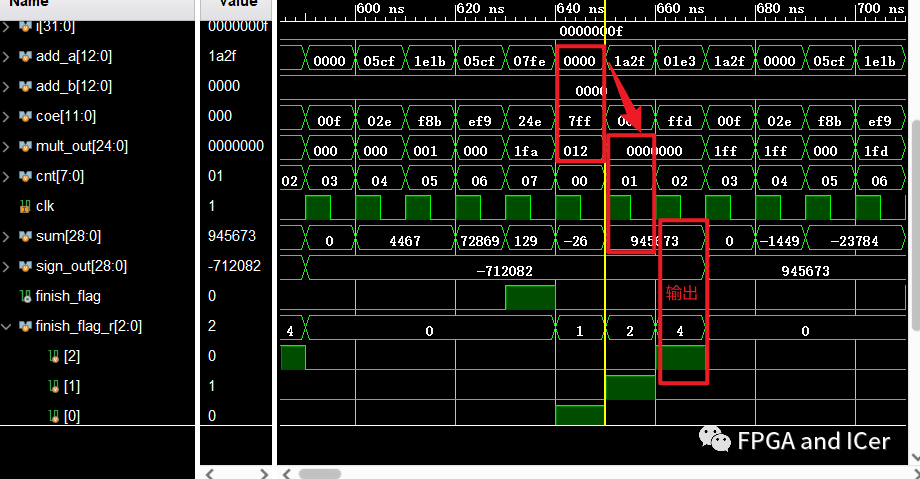

其中,代码增加了一个信号输出标志,该标志信号为传输8次数据后延时三拍的数据,为什么是三拍? 因为读取信号后首先做了一级位宽拓展,第二级做了乘加运算,第三级为累加输出。 所以输出信号相比传输数据完成的位置延迟三拍。

针对乘累加运算,这里没有使用IP,但是为了加速信号传输该信号的运算使用dsp48,所以在信号声明时前面加了(*use_dsp48="yes"*)。

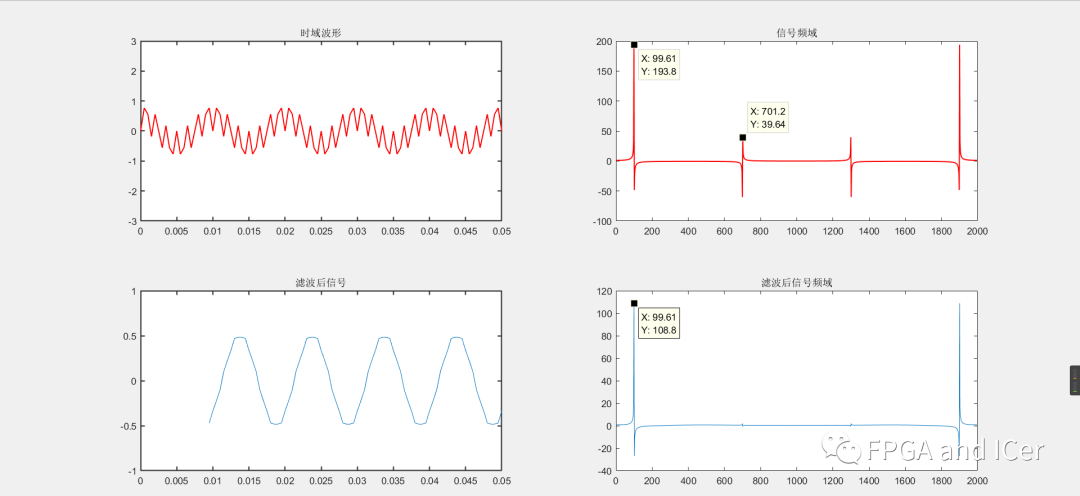

仿真数据设计

为了验证串行设计代码的正确性。 这里使用MATLAB脚本产生了一个混频信号,然后将混频信号进行量化处理并导出txt文件以供仿真文件读取。

clc;close all;clear all;

Fs = 2000; %采样频率

N = 2^10; %采样点数

f1=300; %正弦波1频率

f2=400; %正弦波1频率

t=[0:N-1]/Fs; %时间序列

s1 = sin(2*pi*f1*t) ;

s2 = sin(2*pi*f2*t) ;

s = s1 .* s2;

figure(1);

subplot(1,2,1);

plot(t,s,'r','LineWidth',1.2);

title('时域波形');

axis([0,100/Fs,-3,3]);

set(gca,'LineWidth',1.2);

%转化为位宽12bit数据

s_12bit=s./max(s).*(2.^11 - 1); % DA输入波形,量化到16bit

s_12bit(find(s_12bit<0) ) = s_12bit(find(s_12bit<0) ) + 2^12 - 1;

s_12bit = fix(s_12bit);

s_12bit = dec2hex(s_12bit);

% %生成文件

fid= fopen('sin_data.txt','w+');

%生成十六进制

for i=1:N

fprintf(fid,'%s',s_12bit(i,:));

fprintf(fid,'\\r\\n');

end

fclose(fid);

%% 设计验证

N=16; %滤波器长度

fs=2000; %采样频率

fc=500; %低通滤波器的截止频率

B=12; %量化位数

%生成各种窗函数

w_kais=blackman(N)';

%采用fir1函数设计FIR滤波器

b_kais=fir1(N-1,fc*2/fs,w_kais);

ss=conv(b_kais,s);

subplot(1,2,2);

plot(t(20:1000),ss(20:1000));

title('滤波后信号');

axis([0,100/Fs,-1,1]);

set(gca,'LineWidth',1.2);

运行仿真后,根据设计的滤波器系数进行仿真,发现可以正常滤波除去高频分量。

滤波仿真效果

仿真激励文件编写

`timescale 1ns / 1ps

module Fir_FullSerial_tb;

// Parameters

localparam integer SIGN_IN_WIDTH = 12;

localparam integer SIGN_OUT_WIDTH = 29;

localparam integer FIR_COE_WIDTH = 12;

localparam integer FIR_COE_NUM = 16;

// Ports

reg clk = 1;

reg rst = 1;

reg [SIGN_IN_WIDTH-1:0] signal_in;

wire [SIGN_OUT_WIDTH-1:0] signal_out;

Fir_FullSerial #(

.SIGN_IN_WIDTH(SIGN_IN_WIDTH ),

.SIGN_OUT_WIDTH(SIGN_OUT_WIDTH ),

.FIR_COE_WIDTH(FIR_COE_WIDTH ),

.FIR_COE_NUM (FIR_COE_NUM )

)Fir_FullSerial_dut (

.clk (clk ),

.rst (rst ),

.signal_in (signal_in ),

.signal_out ( signal_out)

);

reg [11:0] mem [0:99];

reg [9:0] addr ;

reg [11:0]data_out ;

always #(10*8)

begin

if(rst==0)

addr = addr + 10'd1;

signal_in = mem[addr][11:0];

end

always

#5 clk = ! clk ;

initial

begin

signal_in =0;

$readmemh("sin_data.txt",mem);

addr = 10'd0;

#10;

rst = 0;

end

endmodule

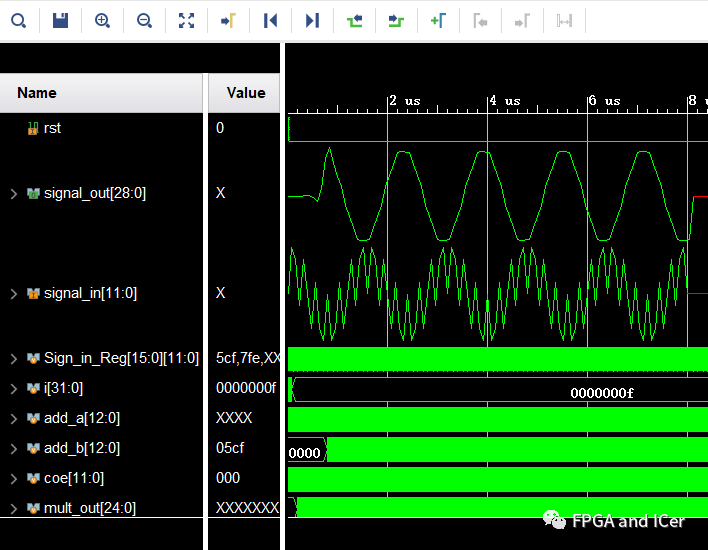

运行仿真,查看波形可见,滤波效果和仿真结果一致。

仿真波形

关于之前提到的延迟三拍的问题可以在波形输出这里查看,7ff为滤波器系数上次运算的最后一个数据,此数据运算结果在下一拍,乘加运算的结果为0,下一拍进行累加输出给sign_out输出。

延迟分析

-

基于FPGA的FIR滤波器设计与实现2012-08-11 0

-

并行FIR滤波器Verilog设计2020-09-25 0

-

高效FIR滤波器的设计与仿真-基于FPGA2008-01-16 1659

-

用MATLAB设计FIR滤波器的方法2008-01-16 15426

-

如何用用FPGA实现FIR滤波器2009-03-30 4672

-

FIR带通滤波器的FPGA实现2009-11-13 7060

-

基于MATLAB及FPGA的FIR低通滤波器的设计2011-08-05 1047

-

基于Matlab的FIR带通滤波器设计与实现2012-07-26 29352

-

基于MATLAB与FPGA的FIR滤波器设计与仿真2012-09-25 1136

-

基于Matlab/Simulink的FIR数字滤波器的设计与实现2016-01-15 984

-

基于matlab和fpga的FIR滤波器设计2016-04-27 952

-

基于MATLAB的FIR滤波器设计与滤波2016-12-14 1289

-

FIR滤波器的FPGA设计与实现2017-12-21 1047

-

FIR滤波器的MATLAB与FPGA设计2022-04-24 3365

全部0条评论

快来发表一下你的评论吧 !