FPGA跨时钟域处理的注意事项

可编程逻辑

1366人已加入

描述

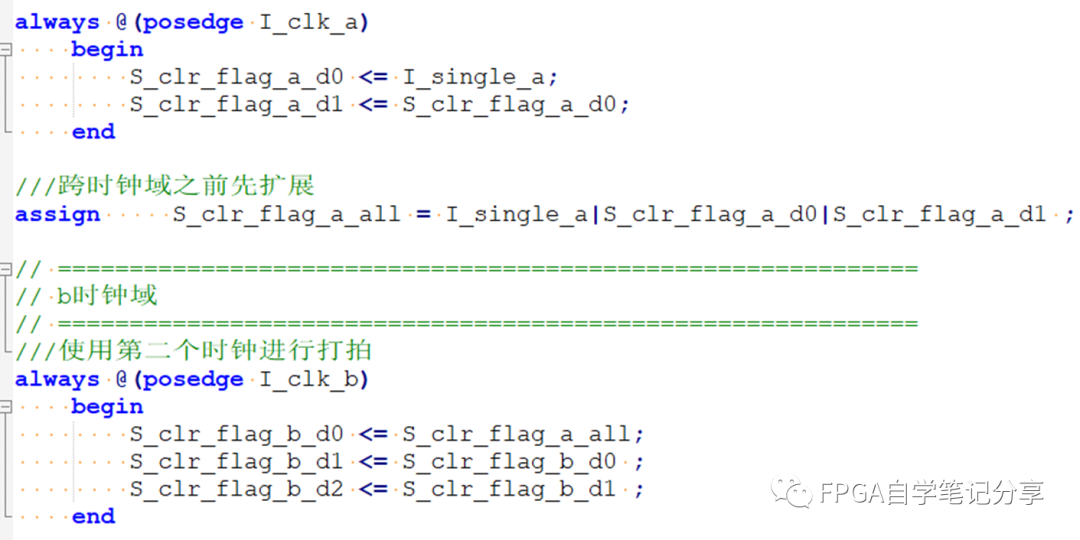

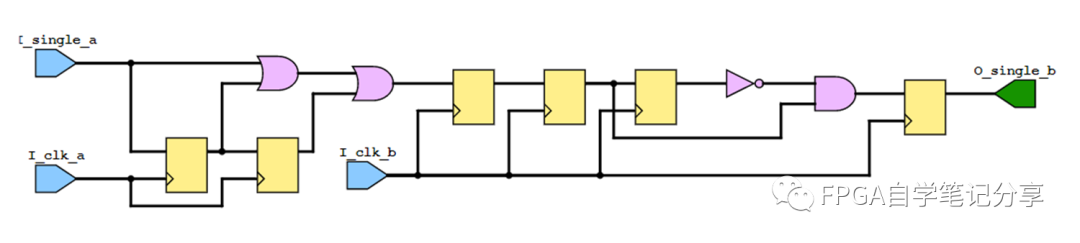

1、跨时钟域之间不能存在组合逻辑。 跨时钟域本身就容易产生亚稳态,如果在跨时钟域之间存在组合逻辑会大大增加竞争冒险出现的概率。 这一点在实际设计中通常会因为粗心而导致设计异常,如下边代码中的S_clr_flag_a_all信号,就是在扩展时不小心使用了组合逻辑,这种情况下由于竞争冒险,会导致跨时钟域后的b信号出现一个clk的异常电平。

此时的跨时钟域威廉希尔官方网站 为:

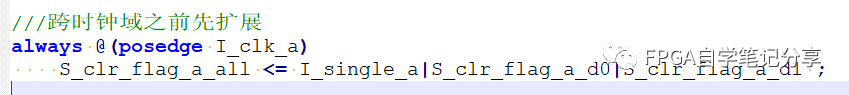

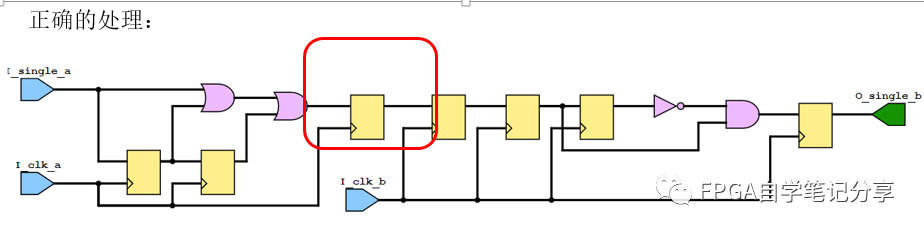

正确的处理方法是使用时序逻辑进行扩展:

正确的威廉希尔官方网站 为:

2、跨时钟域信号要集中在一个位置跨时钟域,然后再使用,不能分别跨时钟域处理。

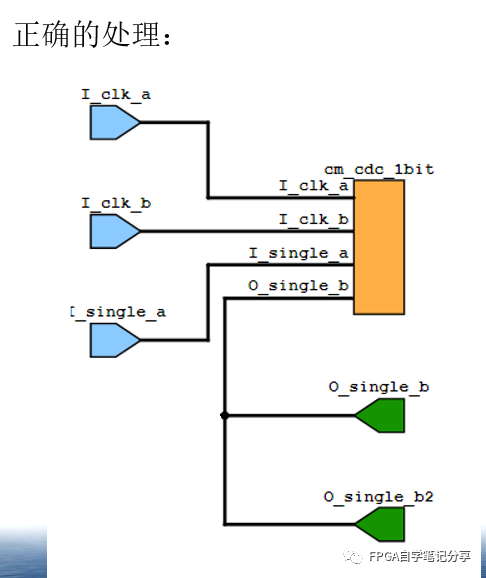

如下图,a时钟域的a信号要在b信号内的b和b2两个位置使用,正确的处理如下:

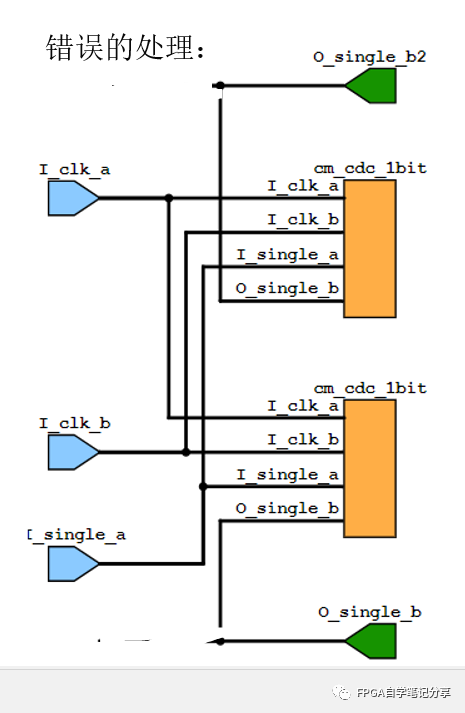

错误的处理方式如下,这种处理方式下,由于b和b2分别做的跨时钟域,由于时钟抖动、走线路径的原因,会导致b和b2不同步,如果该信号是一个关键的控制信号,会导致系统异常,要注意避免这种情况的发生。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

基于FPGA的跨时钟域信号处理——MCU2021-11-01 494

-

如何处理好FPGA设计中跨时钟域问题?2020-09-22 0

-

FPGA初学者的必修课:FPGA跨时钟域处理3大方法2021-03-04 0

-

如何处理好FPGA设计中跨时钟域间的数据2021-07-29 0

-

FPGA跨时钟域处理简介2022-02-23 0

-

FPGA界最常用也最实用的3种跨时钟域处理的方法2017-11-15 13749

-

如何利用FPGA设计一个跨时钟域的同步策略?2018-09-01 5554

-

关于FPGA中跨时钟域的问题分析2019-08-19 3351

-

FPGA设计中解决跨时钟域的三大方案2020-11-21 3876

-

揭秘FPGA跨时钟域处理的三大方法2022-12-05 1649

-

介绍3种方法跨时钟域处理方法2021-09-18 22295

-

(10)FPGA跨时钟域处理2021-12-29 429

-

三种跨时钟域处理的方法2022-10-18 7781

-

FPGA跨时钟域处理方法(一)2023-05-25 1989

-

FPGA跨时钟域处理方法(二)2023-05-25 1030

全部0条评论

快来发表一下你的评论吧 !