优化设计以实现高性能,同时满足严格的设计计划

描述

本博客的第 1 部分探讨了从事片上系统 (SoC) 目标高能效设计的设计人员面临的问题,以及 Synopsys 的 PrimeShield 设计鲁棒性解决方案如何帮助优化低功耗设计,同时实现积极的上市时间目标。

最后一部分将深入探讨PrimeShield设计鲁棒性解决方案如何帮助SoC设计人员优化其设计以实现高性能,同时满足紧迫的设计计划,并提供一些实际示例。

设计稳健性,实现高性能设计

在时序的情况下,经过验证的方法使用静态时序分析 (STA) 来分析每个时序路径,并根据频率指标单独检查它们。由于高级节点的显著可变性,特别是在低电压下,非常需要分析由高可变性引起的潜在性能瓶颈。通过对所有关键路径进行统计关联来识别这些瓶颈的统计分析可以避免过度补偿,同时提高设计性能、功耗和面积 (PPA) 指标。在时序性能方面也出现了新的PPA机会。

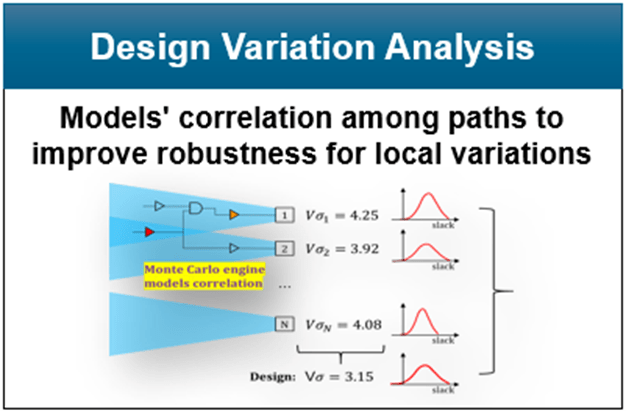

PrimeShield设计变异分析(DVA)通过显式跟踪通过公共单元的路径之间的相关性来计算准确的每个端点西格玛。它使用 STA 蒙特卡罗分析以及来自现有 LVF 库的精确时序数据实现可预测的时序,并针对运行时进行了高度优化。DVA的路径相关性感知方法显着降低了悲观情绪,而不是假设路径是独立的传统方法。变化鲁棒性功能还可以识别芯片上的瓶颈单元,通常是变化较大且引脚松弛不足的单元;修复这些电池可以显著提高设计鲁棒性,而功耗可以忽略不计。

在基于时序裕量的传统方法中,旨在确保稳健性的增加裕量会对性能产生负面影响。降低时序裕量的关键是通过控制晶体管之间对时钟路径工艺变化的跟踪来减少时钟和信号偏斜冗余。为了减少时序悲观情绪,PrimeShield设计鲁棒性解决方案执行全局偏斜分析。全局偏斜分析计算与全局和互连 VT 偏斜相关的路径鲁棒性。

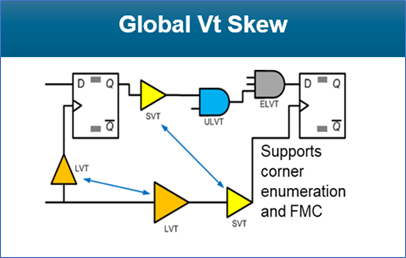

全局 V T 变化在单个 V T 类中具有很强的相关性,但在不同的 VT 类之间仅部分相关。与传统分析一样,同时应用最小/最大时序降额过于悲观;然而,对N VT类的2种N组合的分析是极其成本和资源密集型的。因此,设计人员被迫在时钟网络中仅使用一种VT类型,并背负着额外的时序悲观的惩罚。

PrimeShield全局V T偏斜分析允许用户在发射和捕获路径中对相同VT类的所有单元应用相同的降额。因此,它抵消了同一VT级变化的发射/捕获影响,显着降低了悲观情绪,同时仍确保签核安全。该分析还允许在时钟网络中使用多个V T类,同时提高签核安全性,即使在时钟网络中使用一种VT类型也是如此。

此外,PrimeShield 设计鲁棒性解决方案通过显著减少全局 V T 变化所需的 STA 角库数量以及 N V T 类确定最差混合 V T 时序松弛所需的 2N V T 组合运行,提高了设计人员的工作效率。

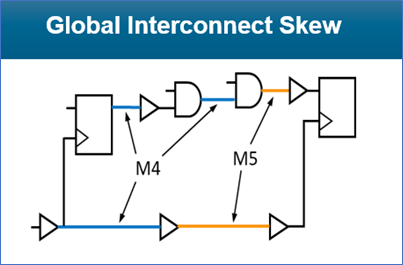

同样,金属/互连变化在每层内也高度相关,但在不同的金属层之间仅部分相关。与传统分析一样,同时应用最小/最大寄生边界过于悲观;然而,对N种金属层的2种N组合进行分析是极其成本和资源密集型的。

PrimeShield 全局互连偏斜分析明确模拟了发射和捕获路径中相同金属层内变化的延迟影响的抵消。它减少了时序悲观情绪,同时仍然提供签核安全性;可以采用基于蒙特卡罗的快速分析来实现最高精度。全面的设计变化和全局偏斜分析可最大限度地减少时序悲观保护带和过裕量,从而改善设计性能并提升 FMAX。

证据就在布丁里

通过早期的合作伙伴关系和广泛的合作,灯塔客户已转向PrimeShield设计鲁棒性解决方案,以利用相互技术和专有技术来提高先进节点设计的鲁棒性,并实现新的功耗和性能水平。

PrimeShield设计稳健性解决方案已经在多个客户部署中证明了其有效性:

移动/5G、HPC 和汽车领域的全球半导体领导者在多个模块的总功耗降低 4% 后,在 3/6 纳米超低功耗设计流片上部署了 PrimeShield。

一家大型北美半导体领导者在 5/4 nm 设计上部署了 PrimeShield 设计鲁棒性解决方案,通过设计变化分析、7:13 VT 库角落和运行时间缩短以及 1× 蒙特卡罗仿真性能改进,FMAX 提升了 120%。

亚洲一家大型手机芯片供应商能够在保持相同功率和面积的同时,将下一代 8 纳米高性能 CPU 的 FMAX 提高近 5%。

一家供应商通过使用PrimeShield电压松弛分析,同时保持时序,在为美国领先的超大规模企业设计的11 nm SoC上,将动态功耗降低了5%。

总结

如今,由于统计鲁棒性分析的成本和复杂性,它通常在设计周期的后期进行,甚至作为事后分析。但对于领先的客户来说,鲁棒性已成为除功耗、性能和面积之外必不可少的设计质量指标。PrimeShield设计鲁棒性解决方案的快速、高容量鲁棒性分析引擎意味着设计人员最终可以在整个设计流程中优化最佳设计性能、功耗、面积和鲁棒性(PPA-R)。

PrimeShield 设计鲁棒性解决方案在 Synopsys 融合设计平台中提供,可提供具有最小统计鲁棒性损失和最佳设计 PPA-R 的设计。它为客户设计团队提供全面的全局鲁棒性、偏斜和电压松弛分析和优化,以解决由变化引起的设计漏洞,同时最大限度地提高下一代设计的能效和性能。

审核编辑:郭婷

-

NVIDIA火热招聘GPU高性能计算架构师2017-09-01 0

-

时钟设备如何满足复杂系统的高性能时序需求?2018-08-27 0

-

高性能DAQ系统的ADC电压基准两级缓冲器优化设计2018-12-07 0

-

满足各种不同应用需求的RF功率测量优化方法讨论2019-07-22 0

-

时钟IC怎么满足高性能时序需求?2019-08-12 0

-

如何在电源转换应用中实现高性能、成本优化型实时控制设计?2021-03-16 0

-

如何优化封装以满足SerDes应用键合线封装规范?2021-04-25 0

-

可满足高性能数字接收机动态性能要求的ADC和射频器件有哪些?2021-05-28 0

-

AutoKernel高性能算子自动优化工具2021-12-14 0

-

卓越性能电源计划的目的2021-12-27 0

-

怎么把电源计划设置为高性能呢2021-12-31 0

-

高性能、多通道、同时采样ADC在数据采集系统(DAS)中的设计2023-06-16 1634

-

Hitek Systems开发基于PCIe的高性能加速器以满足行业需求2024-03-22 623

-

优化TPS546xx的布局以实现热性能2024-10-12 81

-

如何优化MEMS设计以提高性能2024-11-20 308

全部0条评论

快来发表一下你的评论吧 !