DDR5/4/3/2:每一代 DDR 如何提高内存密度和速度

描述

驱动未来存储器的关键特性是存储器密度、速度、更低的工作电压和更快的访问速度。DDR5 支持从 8Gb 到 64Gb 的内存密度,以及从 3200 MT/s 到 6400 MT/s 的宽范围数据速率。DDR5的工作电压从DDR1的2.4V进一步降低到1.1V。

DDR5现在提供的速度比有史以来第一个SDRAM快16倍。这是通过速度和密度的显着飞跃来实现的,每一代 DDR 都有所增加。在这篇博客中,我们将讨论不同DRAM存储器的演变,从SDRAM到最新的DDR5。

从1970年代初到1990年代中期生产的DRAM使用异步接口,其中输入控制信号对内部功能有直接影响。SDRAM于1993年推出,提供了一个同步接口,在其时钟输入的上升沿之后,可以识别控制输入的变化。它支持512Mb的内存密度。继SDRAM之后,一系列DDR进入市场,每个DDR都有一些新功能并增加了内存密度。现在,下一代 DDR5 将确保以更低的功耗和更高的速度实现更高的内存密度和许多新功能。

SDRAM(同步动态随机存取存储器):

SDRAM是动态随机存取存储器,与CPU的时钟速度同步。SDRAM也代表SDR SDRAM(单数据速率SDRAM)。单数据速率意味着SDR SDRAM在一个时钟周期内只能读/写一拍数据。在传输下一个读/写操作之前,需要等待命令完成。SDR 速度从 66 MHz 到 133 MHz 不等。

DDR(双倍数据速率 SDRAM):

DDR SDRAM是一种双倍数据速率同步动态随机存取存储器。它通过在时钟信号的上升沿和下降沿传输数据,在不增加时钟频率的情况下实现双倍数据带宽。预取缓冲区大小为 2n(每次内存访问两个数据字),是 SDR SDRAM 预取缓冲区大小的两倍。DDR 存储器在每个时钟周期将 n 位数据从存储器阵列传输到存储器内部 I/O 缓冲区。这称为 n 位预取。

DDR2(双倍数据速率第二代 SDRAM):

与 DDR1 类似,DDR2 也以两倍的时钟速度传输数据(在时钟信号的上升沿和下降沿传输数据)。此外,内部时钟以数据总线速度的一半运行,从而获得更高的总线速度和更低的功耗。上述所有因素都有助于DDR2-SDRAM实现每个内部时钟周期的四次数据传输。DDR2 的预取缓冲区为 4 位(DDR SDRAM 的双倍)。DDR2的数据速率为400MT/s至800MT/s。

DDR3(双倍数据速率第三代 SDRAM):

DDR3 以两倍于 DDR2 SDRAM 的速率传输数据,从而实现更高的带宽和峰值数据速率。还增加了两个新功能,自动自刷新和自刷新温度范围,使内存根据温度变化控制刷新率。它的预取缓冲区宽度为 8 位。

DDR4(双倍数据速率第四代 SDRAM):

DDR4 能够实现更高的速度和效率,但保留预取缓冲区大小为 8n,与 DDR3 相同。更高的带宽是通过每秒发送更多的读/写命令来实现的。DDR4 标准将 DRAM 银行划分为两个或四个可选的银行组,其中可以更快地转移到不同的银行组。与DDR4相比,DDR3的工作电压也更低。还添加了一些新功能,例如DBI(数据总线反转),CRC(循环冗余校验)和CA奇偶校验。这些新功能增强了DDR4内存的信号完整性,提高了数据传输/访问的稳定性。

DDR5(双倍数据速率第五代硬盘存储器):

DDR5 SDRAM 通过使用 16n 预取缓冲区实现更高的速度。DDR5 将 DRAM 插槽分为两个、四个或八个可选组,而 DDR4 最多使用 4 个存储组。还添加了一些新功能:

写入模式命令 – 它通过不通过总线发送数据来节省功耗。

增强型 PDA:通过将唯一的 PDA 枚举 ID 分配给每个 DRAM 来使用 CA 接口作为每个 DRAM 寻址能力的唯一方法。因此,后续命令不需要使用 DQ 信号来决定为命令选择哪个 DRAM。

写入均衡两种类型的训练 – 用于周期对齐的外部 WL 培训(如 DDR4),用于相位对齐的内部 WL 培训。

支持各种培训,如CA培训,CS培训等。

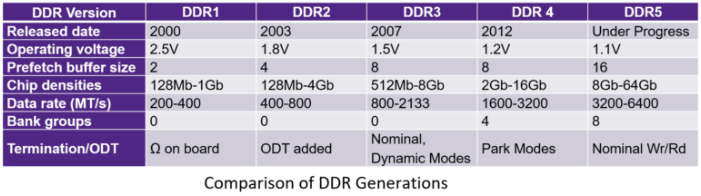

下表列出了各代 DDR 之间的基本差异:

随着每一代新一代 DDR 的出现,内存密度和速度都在显著提高。

审核编辑:郭婷

-

DDR5内存将在明年实现量产2020-12-09 2487

-

DDR5内存将面向数据中心市场2020-12-12 2799

-

什么是DDR?DDR内存的演进之路2022-10-26 0

-

Rambus推出6400MT/s DDR5寄存时钟驱动器,进一步提升服务器内存性能2023-02-22 0

-

新技术内存接口DDR5有望2019年量产2017-09-26 3282

-

三种主流内存技术(DDR、GDDR、LPDDR)的速度对比与应用和DDR5芯片的设计2017-11-15 44635

-

内存条ddr4和显卡ddr52020-07-30 2852

-

嘉合劲威将在2021年率先实现DDR5内存量产2020-12-02 1998

-

DDR3内存突然涨价50% DDR5内存将要上市2021-02-02 3576

-

新一代DDR5内存模组密集发布,支持DDR5 CPU随后就到!2021-04-27 13948

-

新一代内存DDR5带来了哪些改变?2021-05-19 4627

-

ddr5的主板可以用ddr4内存吗 几代CPU才能上DDR52023-08-09 24650

-

DDR5内存的工作原理详解 DDR5和DDR4的主要区别2024-11-22 1014

-

DDR5内存与DDR4内存性能差异2024-11-29 385

-

DDR3、DDR4、DDR5的性能对比2024-11-29 1490

全部0条评论

快来发表一下你的评论吧 !