基于移位寄存器TDM的实现方式

可编程逻辑

1366人已加入

描述

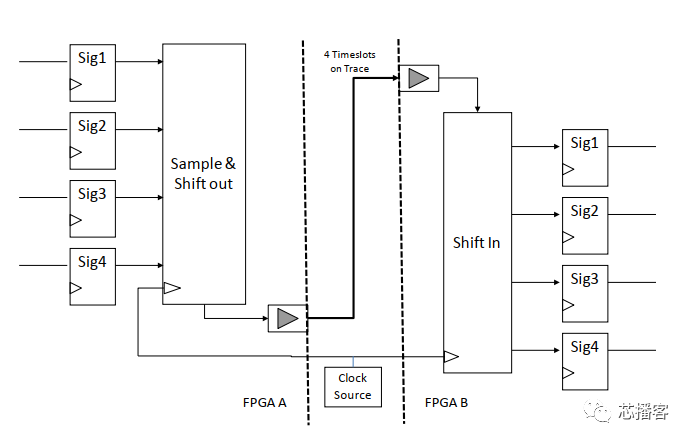

设计中两片FPGA分割边界的数据Sig1、Sig2、Sig3、Sig4……等一大波的信号被并行地加载到传输时钟的上升沿上的移位寄存器中,并用相同的时钟移出。在接收端的FPGA_B中,移位寄存器对传输时钟上的输入数据进行采样,并与设计并行地提供数据。

第一个采样(在这种情况下为sig4)在移位寄存器输出端从采样时钟边缘可用,但是在该方案的一些版本中可能需要传输时钟的额外边缘,以便在数据被完全移位到目标寄存器之后锁存数据。再次,发送和接收移位器需要启动,然后保持同步。

这种类型的方案非常适合在FPGA间trace迹线上具有比平均传输时间更长的板,因为路径中没有额外的组合延迟,我们可以最大限度地利用传输时钟周期。特别是,如果先前的采样尚未被时钟记录到接收逻辑中,则不可将新数据采样到记录道上。

在某些实验室情况下,我们可能会很幸运,但在其他情况下,传输线的轨迹特性或连接中的轻微不连续性可能会使传输不可靠。因此,我们有传输时钟速度的物理上限,如果我们达到了这个上限,那么进一步提高复用率的唯一方法就是降低整个系统的速度。这样做之后,即使使用10:1或更高的多路复用器比率,我们也只需要以更低的时钟速率原型。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

移位寄存器的特点_移位寄存器工作原理2017-12-22 49512

-

线性移位寄存器2010-01-12 1975

-

移位寄存器,移位寄存器是什么意思2010-03-08 17512

-

移位寄存器的工作原理是什么?2010-03-08 44919

-

寄存器与移位寄存器2016-05-20 1141

-

移位寄存器实验报告_移位寄存器原理2017-12-22 28582

-

移位寄存器具有什么特点及作用?2017-12-22 84975

-

移位寄存器怎么用_如何使用移位寄存器_移位寄存器的用途2017-12-22 20312

-

一文解析Matlab如何实现移位寄存器2018-04-26 16808

-

移位寄存器的原理2019-07-15 74820

-

移位寄存器的种类与作用2019-07-15 16703

-

移位寄存器的设计与实现2022-09-06 4612

-

基于移位寄存器的TDM的实现方式2023-05-23 355

-

移位寄存器的工作原理 移位寄存器左移和右移怎么算2024-01-18 8561

-

移位寄存器右移是怎么移位的2024-07-12 1447

全部0条评论

快来发表一下你的评论吧 !