深度剖析UVM中的Analysis port

描述

Analysis port

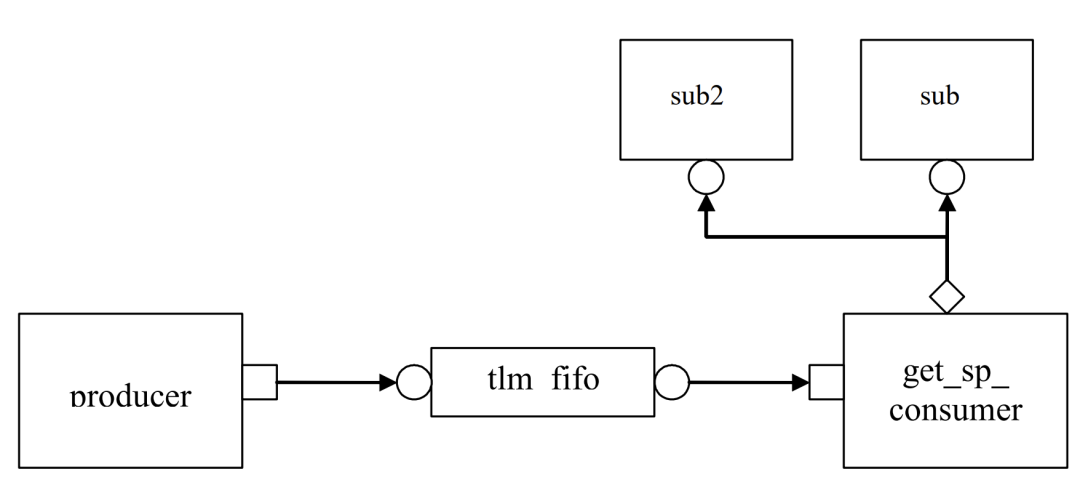

每个组件通过其TLM接口与系统中的其他组件进行通信,用于给DUT发送激励或者对DUT的行为进行响应。

然而,在任何绝大多数复杂的验证环境中,特别是随机验证环境中,需要将收集到的transaction发送给环境的其他部分,以便进行端到端检查(scoreboard)或收集接口覆盖率。

这两种类型的TLM通信的区别在于,put/get ports通常需要一个相应的export来提供实现。对于analysis port来说,一个monitor能够产生一个transaction而不用关心连接了哪些组件。各个不同的analysis components连接到monitor analysis_port,以不同的方式处理transaction。

类比于,互联网上看到同一个新闻,不同的人会产生不同的反应,有的人兴高采烈,有的人捶胸顿足。 这就是订阅者模式。

uvm_analysis_port

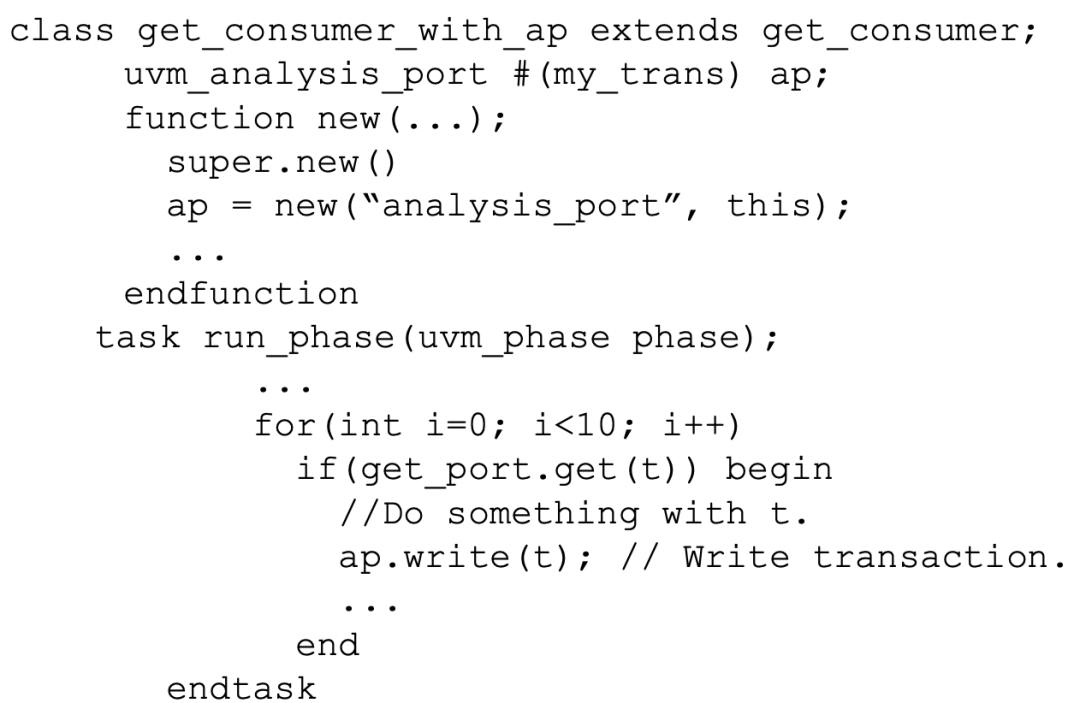

uvm_analysis_port是一个特别的TLM port,其接口包含一个函数 write()。

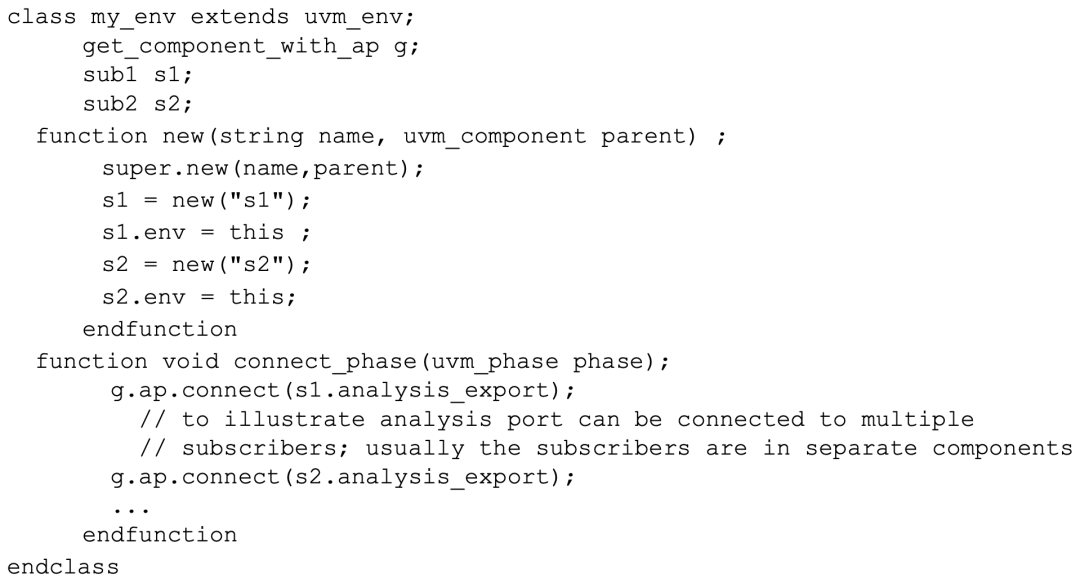

uvm_analysis_port包含一个连接到它的analysis_exports列表。当组件调用analysis_port.write()时,analysis_port会遍历该列表并调用每个analysis_export的write()方法。如果没有任何连接,write()的调用就直接返回。因此,一个uvm_analysis_port可以连接到0个、1个或者多个analysis_exports,但analysis_port.write()操作并不取决于连接的analysis_exports数量。

因为write()是一个void function,所以write()将总是在同一个delta cycle内完成,无论连接了多少个组件。

在上一层环境中,analysis port被连接到相应组件的analysis export,如coverage collectors和scoreboards等等。

Analysis Exports

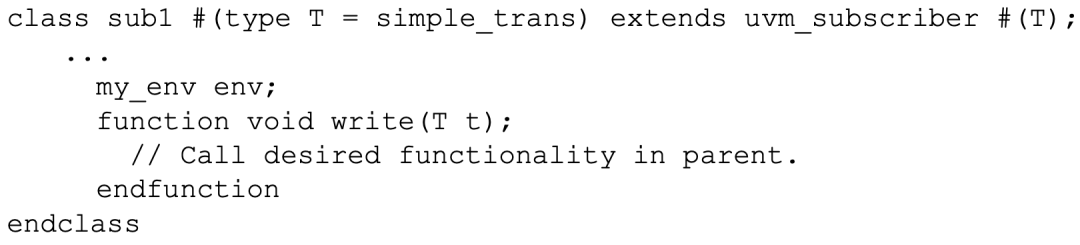

与其他TLM连接一样,连接到analysis port的每个组件都要通过analysis_export提供write()的实现。

uvm_subscriber基础验证组件可以用来简化这个操作 ,所以一个典型的 analysis component会扩展自uvm_subscriber:

与上面描述的put()和get()一样,analysis port和analysis_export之间的TLM连接,需要允许analysis_export提供write()的实现。如果多个analysis_export被连接到一个analysis port,该端口将依次调用每个analysis_export的write()方法。

所有write()的实现都必须是function,analysis port的write() function会立即完成,不管连接到多少个analysis_export。

当多个uvm_subscriber连接到一个analysis port时,每个uvm_subscriber都被传递同一个transaction对象的指针,即write()调用的参数。每个write()的实现都必须copy这个transaction对象,然后对copy的对象进行操作,以避免破坏传递相同指针的其他transaction对象内容。

UVM还包括一个Analysis_fifo,它是一个包括analysis_export 的uvm_tlm_fifo,以允许blocking components访问analysis port传递的transaction对象。

analysis_fifo是unbounded的,所以monitor的write()可以保证立即完成,然后,analysis组件可以随意从analysis_fifo中获取transaction。

全部0条评论

快来发表一下你的评论吧 !