一款射频芯片的layout设计指导案例

RF/无线

描述

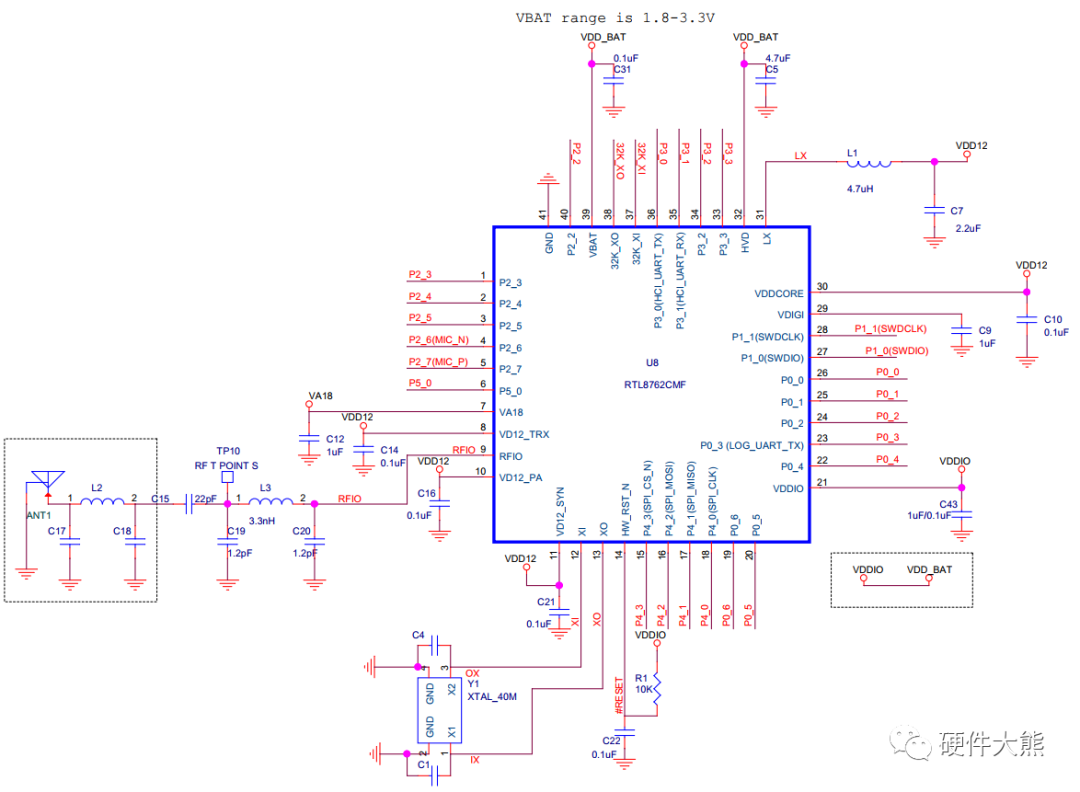

RTL8762C是瑞昱一款超低功耗蓝牙芯片,瑞昱的硬件设计指导书中,关于该芯片的layout设计指导很有普适性的参考指导意义,如下为笔者做过一定简化的芯片最小系统原理图——

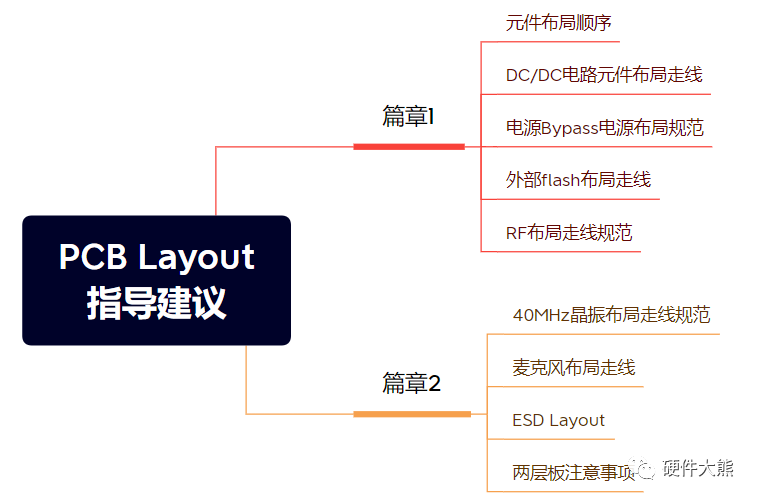

PCB Layout建议分如下几个点——

元件布局顺序

按如下顺序布置元件,顺序靠前的元件意味着布局时需要尽量靠近 IC

DC/DC 威廉希尔官方网站 元件

VBAT bypass 电容

RF 威廉希尔官方网站 元件

40MHz 晶振

RF VDD bypass 电容

其他 bypass 电容

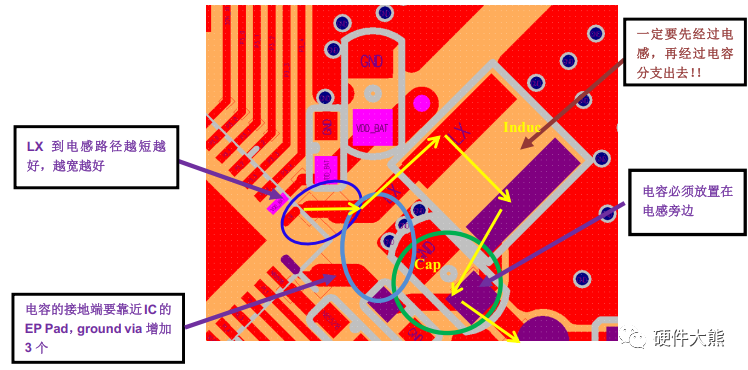

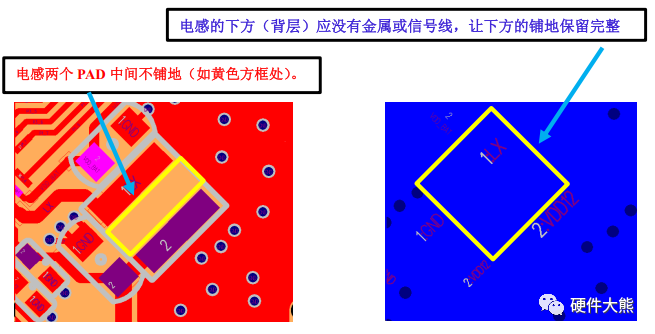

DC/DC威廉希尔官方网站

元件布局走线

1. HVD/VBAT 的电源输入线尽量粗,建议 20 或者 25mil。

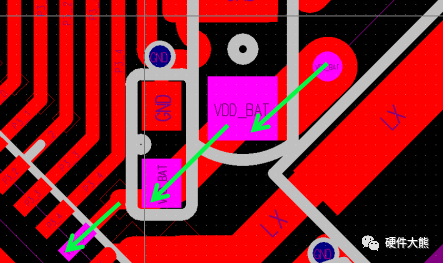

2. DC/DC 的电感及电容放置必须靠近 CHIP 的输入端。

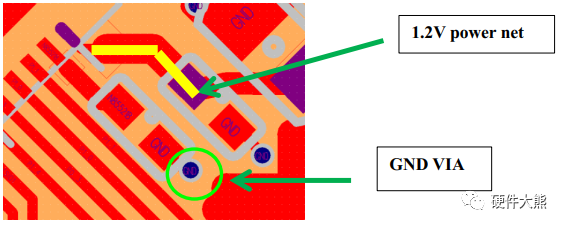

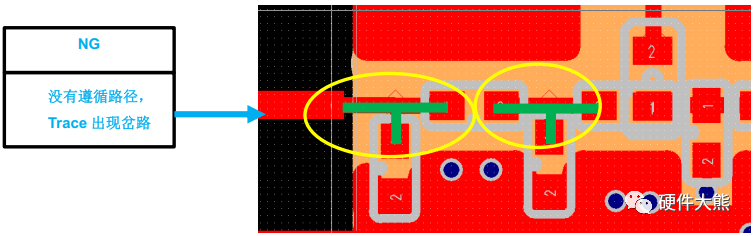

3. DC/DC LX Pin 经过电感和电容形成一个稳定、低噪声的电压源,先经电感再经电容,严格禁止未经过电容就分支出去(如图黄线标示)。考虑 EMI 问题, LX 信号线必须短而粗, Trace 宽度建议 15mil 以上。

4. 电容的接地端尽可能靠近 IC 的 E-PAD,如果空间足够,电容的 GND VIA 可以放三个,让 GNG 的回流比较好。

电源Bypass电源布局规范

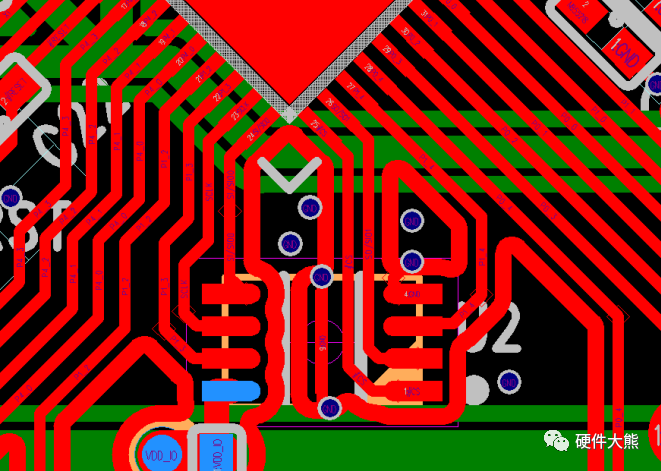

1. Bypass 电容放置必须靠近 Power pin 的输入端,回流无阻隔,正常回流到芯片 GND。

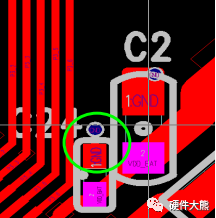

2. Bypass 电容独立过孔接地,且过孔尽量靠近电容 PAD,减小回流路径,如下图标注。

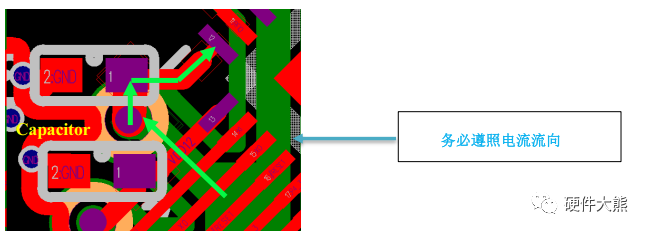

3. 电源线走线路径必须先经电容再进 Power pin 的输入端, 线宽建议 15mils 以上

4. 电源的 Bypass 电容摆放必须靠近 IC,走线必须先经过电容,再进入 IC 或输出给其他分支电源

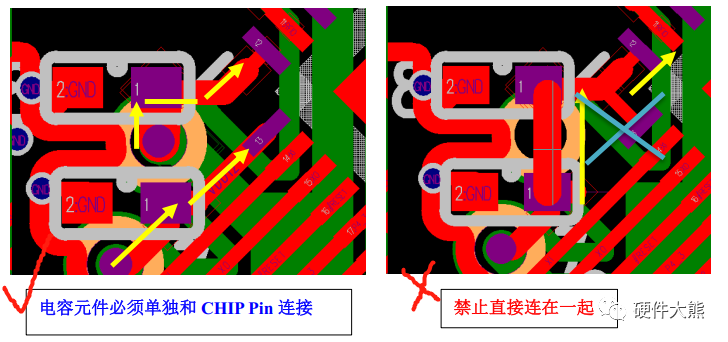

5. 如果同电源 net 有 2 个相邻的 Bypass 电容元件,必须单独和 IC Power Pin 连接,不可以直接连接在一起。

6. VDIGI 和 VDDIO 的 Bypass 电容尽可能远离 1.2V 电源 Net

外部flash布局走线

外部 Flash 需要尽量靠近 IC 放置, 所有信号线尽量走等长线。

RF布局走线规范

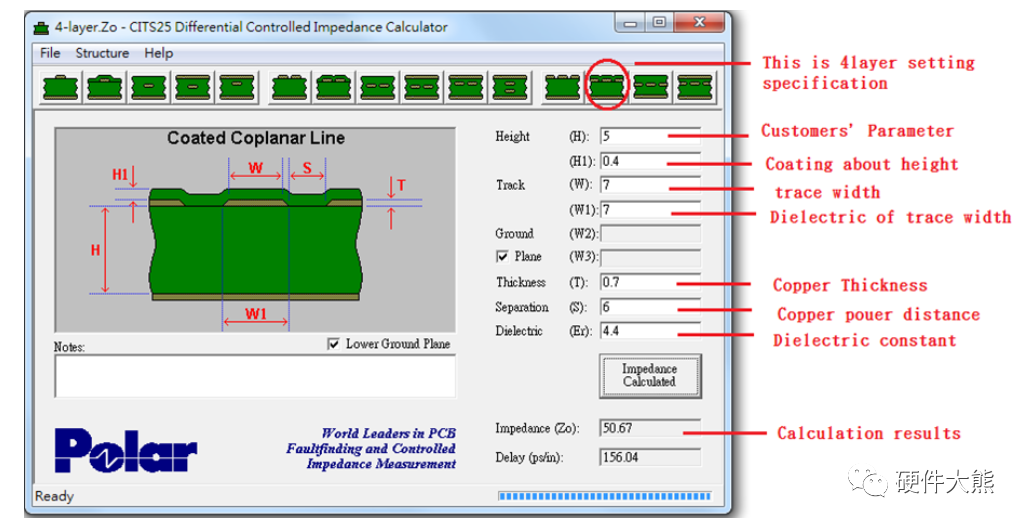

1.RF 阻抗计算:RF 线是指 IC RFIO Pin 脚到天线间的连线,这段连线必须小心控制阻抗在 50Ω +/-10%内,可以使用 RF 阻抗计算工具得出符合 50 欧姆阻抗线宽、线距来进行走线。参数包括 RF 信号线到参考层的距离(H)、绿漆厚度(H1)、线宽(W)、线宽误差(W1)、铺铜厚度(T)、铺铜间距(S)、介电常数(Er)

2. 为了避免 RF 阻抗的较大变化,建议 RF 线不得小于 8mil

3. RF 测试点 TP10 放置避免出现岔路,如果测试点放置在 BOTTOM 层,可在路径上加 VIA 连接。

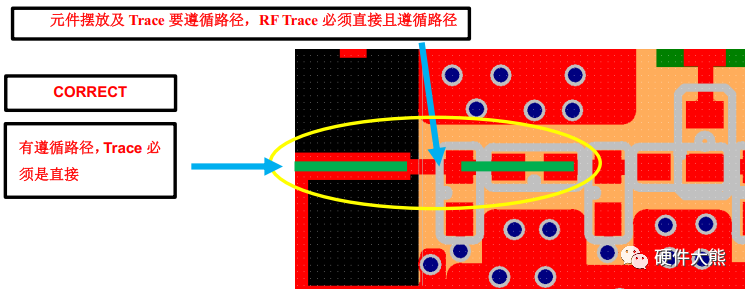

4. RF 匹配元件尽可能靠近 IC RFIO Pin 脚。

5. 2层板或者 4 层板设计, BT CHIP(TOP 层)的下层必须是接地层(GND 层)。

6. RF 匹配元件及走线的参考层,禁止有任何信号线穿越(2 层板 PCB 尤其要注意)。

7. 天线区域需要禁空,不应该有铜,天线下方不应该有信号线。

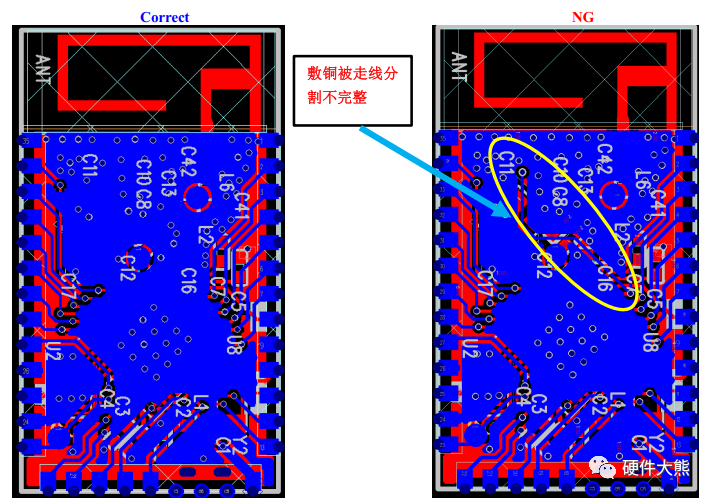

8. 天线参考地尽快回流到芯片地,天线回流路径需要:距离最短、没有阻隔、连接良好。下面两图中右图覆铜被走线分割不完整,左图比较好。

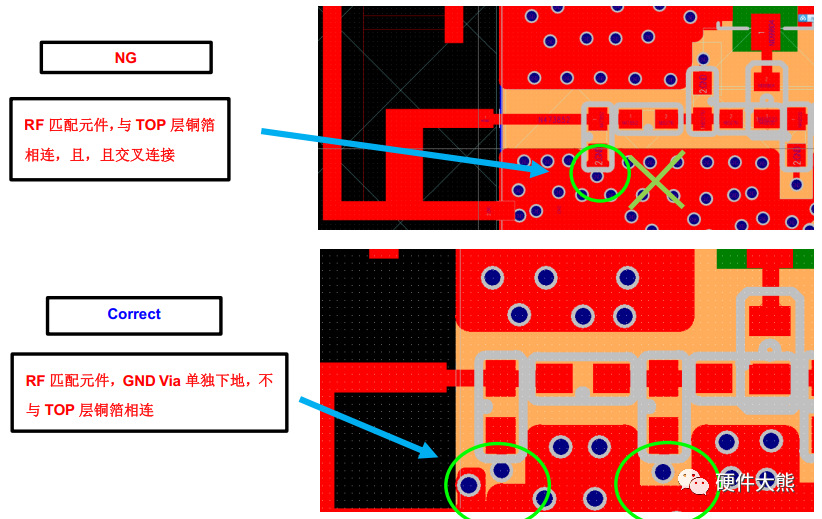

9. RF 元件 GND VIA 要尽可能靠近 PAD,一个 GND VIA,且单独下地,不与 TOP 层铜箔相连,铺铜要用覆盖连接

审核编辑:刘清

-

求推荐一款CPLD芯片2012-11-23 0

-

请推荐一款芯片2013-01-17 0

-

我想选一款能实现TMS320F2812的ARM芯片,求大神指导~2015-06-18 0

-

求一款带有模拟输出的射频芯片2015-10-12 0

-

求推荐一款ADC芯片2016-09-26 0

-

请问有没有一款参考频率本身在10MHz的射频卡2018-08-31 0

-

请大家给推荐一款集成整个接收通道的芯片2018-12-20 0

-

求推荐一款相位解调芯片2019-03-27 0

-

如何去设计一款高性能的PHS射频收发器芯片?2021-06-01 0

-

开发一款射频SOC蓝牙芯片2021-11-10 0

-

DDR2Layout指导手册2017-10-17 747

-

介绍一款低功耗的单片ASK/OOK射频接收芯片XL7002022-10-13 3367

-

一款射频芯片的layout设计指导案例2023-06-06 1069

-

芯岭技术推出一款单片ASK/OOK射频接收芯片—XL5202024-05-30 1007

-

AT2401C是一款2.4GHz Zigbee 射频前端芯片 功率放大器(PA) 智能家居工业自动化2024-05-31 535

全部0条评论

快来发表一下你的评论吧 !