应用HyperLynx解决高速采集板中阻抗匹配的问题

设计测试

描述

本次设计中高速数据采集板的技术指标如下:a)垂直分辨率12bit;b)双通道同时工作交替采样,单通道采样率为500MSPS;c)有效分辨率位数大于等于10bits;d)信噪比SNR>62dB。该采集板系统的主要器件有ADC芯片,时钟芯片和通道上的模拟放大器和滤波器。

通过对性能指标的综合分析,我们选择ADS5463为我们的ADC芯片,AD9517-3为时钟芯片。数据采集板中遇到的阻抗匹配问题主要集中在这两个芯片上。

ADS5463的采样率为500MSPS,垂直分辨率为12bits,有效分辨位数为10.5bits。ADS5463的时钟信号输入幅值范围很宽,输入的时钟信号峰峰值最大可达到3伏。ADS5463的信噪比和时钟信号的幅度、共模电压的大小、温度以及供电电压的纹波等因素有关。其中时钟信号的幅度对信噪比影响较大,时钟信号的峰峰值越高信噪比越高。数据输出的格式为LVDS电平。

AD9517为可编程的12通道的时钟产生器。AD9517内置有2GHz的VCO,可产生最高800MHz的LVDS时钟信号以及1.6GHz的LVPECL时钟信号。通过对寄存器的设置可以产生不同电平标准以及不同频率的时钟输出信号。

为了尽量增大ADS5463的信噪比,AD9517的输出时钟采用LVPECL电平。LVPECL的信号摆幅为800mV,输出阻抗很低,因此它有很强的驱动能力。ADS5463的输出为LVDS电平、AD9517的输出为LVPECL电平,二者均为差分信号。为了控制差分线的阻抗并且找到一个良好的端接方案,下面引出差分阻抗的定义。

差分线的阻抗

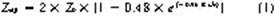

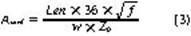

对于FR4材料的边缘耦合微带线,差分阻抗近似为:

式中,Zdiff表示差分阻抗,单位为Ω;Z0表示未耦合时的单端特性阻抗;s表示信号线边沿的间距,单位是mil;h表示信号线与返回路径平面间的介质厚度;FR4介质的介电常数决定了式中的两个系数0.48、0.96。

对于FR4材料的边缘耦合带状线,差分阻抗近似为:

式中,FR4介质的介电常数决定了式中的两个系数0.37、2.9,b表示平面间总的介质厚度,其余同公式(1)。

传输线中,导线引起的总衰减为:

式中,Len表示传输线的长度,单位为in;Z0表示传输线的特征阻抗,单位为Ω;w表示线宽,单位为mil;f表示正弦波频率分量,单位为GHz;Acond表示导线引起的总的衰减,单位是dB;36这个参数和FR4介质的介质耗散因子tan(δ)有关,FR4的介质耗散因子tan(δ)为0.02。

传输线的阻抗匹配和端接

为了使AD采集系统满足设计指标,借助HyperLynx仿真软件的辅助,完成对ADS5463采集系统的板级仿真,减小甚至消除因为阻抗不匹配或者端接错误而带来的振铃,使AD采集系统可以正常工作在指定的频率(500MHz)。并应用上文的公式(1)(2)(3)对实验结果进行计算和分析。

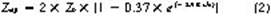

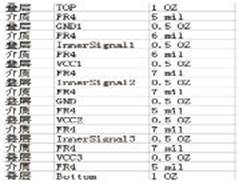

高速数字采集板的信号完整性验证板的叠层结构如图1所示。

图1 验证板的叠层结构

为了使多层印制板在正常工作时能够满足电磁兼容和敏感度标准,在进行多层印制板的分层及堆叠设计时应该从信号的返回路径及电源和地层的阻抗这两个方面考虑。

对于多层板中的传输线,驱动器受到的阻抗主要由信号路径和与之最近的平面构成的阻抗决定的,而与实际连接在驱动器返回端的平面无关。对于高速数字板而言,信号线的良好端接变的很重要。我们希望驱动器受到的阻抗是可以控制的,这样易于在设计时对信号线进行良好的端接。为了满足阻抗可控的要求,在设计高速数字板时要求布线层应安排与映像平面层相邻,重要的信号线应该紧邻地层。这里的映像平面层指的是电源层和地层,即信号的返回路径应该是电源层或者地层。板上的信号层InnerSignal1遵循上述设计原则。InnerSignal1与GND1和VCC1两个映像平面层相邻,形成了带状线结构,在设计时方便通过控制介质的厚度和走线宽度来控制传输线的特征阻抗。

除了信号的返回路径,电源和地阻抗也是在分层时要考虑的一个因素。为了减小地弹和轨道塌陷,在设计时应该尽量的减少电源和地之间的感性阻抗。为了尽可能的减少电源和地之间的感性阻抗,要求电源平面和地平面相邻并且尽可能的靠近。FPGA的核电压布在VCC2电源层。板上的电源层VCC2和GND层相邻并且介质厚度仅为5mil,这将使VCC2和GND之间的感抗较小。

验证板上的器件为:AD9517时钟芯片一片用于给ADS5463提供时钟,ADS5463一片用于数据采集,两片FPGA为Altera公司的StratixII系列的EP2S60用于接收和处理AD采集后的数据,LT1764五片用于提供板上的电源。

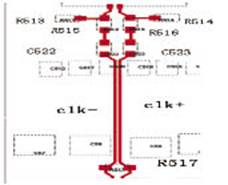

首先对ADS5463的时钟线进行分析。为了使ADS5463有一个较高的信噪比,AD9517的输出时钟设为LVPECL电平。验证板上由AD9517到ADS5463的时钟线布局如图2所示。

图2 时钟线的PCB布局图

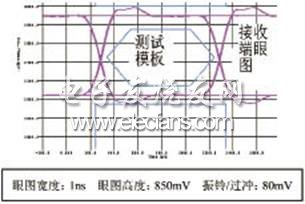

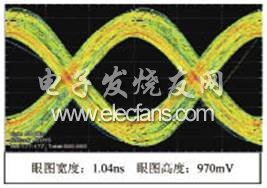

对时钟信号采用交流耦合并联端接的方式。图2中的R517为并联端接电阻,阻值为100Ω。C523和C522为交流耦合隔直电容,容值为0.1nF,C523和C522的存在将使ADS5463的时钟信号以ADS5463自带的2.5V参考电平作为共模电压。R515和R516为零,在本设计中不起作用。由于LVPECL输出为射随输出结构,故需要两个电阻拉到一个直流偏置电压。电阻R513和R514用来提供偏置电压,电阻值为200Ω。时钟线clk-、clk+布局在顶层,为一对边缘耦合微带线。微带线clk-、clk+的结构为:s=4mil,h=5mil、Z0=62.72Ω,介质为FR4。由式(1)可计算得Zdiff=99.03Ω。显然,传输线的特征阻抗和端接电阻R517的阻值相差很小,时钟信号存在极轻微的反射。利用HyperLynx仿真软件对时钟线clk-、clk+进行仿真。ADS5463的时钟输入端接收到的时钟信号的眼图如图3所示。

图3中六边形的部分和矩形的边框为眼图的测试模板,其他部分为接收端的眼图。对于LVPECL电平而言,噪声容限为200mV。输出电压典型值为800mV,最大阈值电压为300mV。ADS5463的上升时间和下降时间的典型值为500ps(注:这里的上升时间和下降时间指的是上升沿和下降的20%到80%这一段长度所占用的时间)。根据这些参数我们设定用于眼图测试的模板。用于眼图测试的模板是图3中的六边形。

图3 时钟信号的眼图

仿真的结果显示:眼图的宽度为1ns,眼图张开的高度约为850mV,过冲的高度约为80mV,接收端的眼图并未碰到模板。从上述分析来看,由ADS5463接受到的差分时钟信号符合LVPECL电平的标准,可以在AD采集系统中使用。仿真的眼图并不完美,眼图中产生的小幅度的振铃及过冲与端接电阻、隔直电容以及提供偏置电压的电阻处的短桩线所引发的阻抗突变有关。减小这些短桩线的长度会进一步提高眼图的质量。

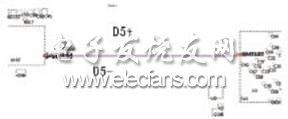

除了时钟线以外,板上另一组需要仿真的重要信号线是ADS5463的数据线。ADS5463将AD转换后的数据通过12位数据总线送往StratixII进行处理。完成对AD时钟线的仿真后,下一步对AD的数据线进行仿真。板上的数据线布局如图4所示。

图4 数据线的PCB布局图

验证板上第二组传输线为数据线D5+/D5-。该差分线为ADS5463到StratixII之间的数据线。ADS5463为发送器、StratixII为接收器,StratixII提供100Ω的片上端接。数据的传输速率为500MHz,LVDS电平。第二组传输线的长度为2.83in,传输线绝大部分在Signal1信号层,只有极短的部分在顶层。对于D5+这根传输线位于顶层的微带线的长度为105.86mil(0.10586in),对于D5-这根传输线位于顶层的微带线的长度为95.07mil(0.09507in)。即发生阻抗突变的传输线的长度足够短,虽然依旧发生了反射但这些反射却被信号的上升或者下降沿遮盖住了,这些反射对传输线的信号完整性产生的影响可以被忽略。传输线D5+/D5-的特征阻抗由在Signal1信号层的部分决定。

对于D5+/D5-在信号层Signal1部分的带状线而言;Z0=52.43Ω、b=12mil、s=9mil、介质为FR4。由式(2)的Zdiff=99.13Ω。即带状线的差分阻抗为Zdiff=99.13Ω。

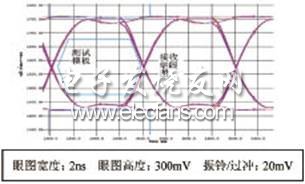

利用HyperLynx仿真软件对ADS5463的数据线D5-、D5+进行仿真。接收端的StratixII得到的数据信号的眼图如图5所示。

图5 数据信号的眼图

图5中六边形的部分和矩形的边框为眼图的测试模板,其他部分为接收端的眼图。对于LVDS电平而言:TIA/EIA-644A标准规定,如噪声容限为147mV,则最小输出差动电压为247mV,最大阈值电压为100mV。StratixII系列器件的LVDS接口的下降时间最大为180ps,上升时间最大为160ps(注:这里的上升时间和下降时间指的是上升沿和下降的20%到80%这一段长度所占用的时间)。根据这些参数我们设定用于对眼图测试的模板,用于眼图测试的模板为图5中的六边形。

仿真的结果显示:接收端眼图的宽度为2ns,接收端眼图的高度约为300mV,大于LVDS接收端要求的最小眼图高度200mV,接收端振铃小于20mV。接收端的眼图并未碰到模板。传输线D5+/D5-完全可以完成500MHz数据传输的任务。

图5显示的眼图并不完美,有轻微的塌陷和很小的振铃。除去传输线D5+/D5-在不同层的部分阻抗不完全相同存在轻微的反射以外,造成D5+/D5-眼图有一定振铃的原因在于过孔影响。介质损耗和趋肤效应则导致了眼图的轻微塌陷。

在高密度的威廉希尔官方网站 板中信号线的穿层不可避免的带来了过孔。信号线的过孔的阻抗一般是在25Ω到35Ω。过孔的阻抗不连续来自于传输线和过孔处的电磁场的不连续以及除了电源和地平面外过孔处回流路径的缺失。

对于因为过孔导致的阻抗突变而带来的反射,在设计中通常采用在过孔附近增加地过孔的方法来改良信号的质量。增加的地过孔起到了传输线上过孔处回流路径的作用。

导线上单位长度的损耗有两部分组成:一部分是由导线损耗引起的衰减,一部分是由介质损耗引起的衰减。趋肤效应是引起导线损耗的主要原因。介质的耗散因子tan(δ)则是引起介质损耗的主要原因。根据公式(3),在D5+/D5-这段传输线上产生的衰减为:Acond =0.3453dB。输入FPGA的电压幅值为ADC输出电压幅值的96%。

通过更换介质材料可以减少导线带来的损耗,进而改善信号的质量。FR4的损耗因子tan(δ)为0.02,是常用的板材中较高的。更换板材,如图5中六边形的部分和矩形的边框为眼图的测试模板,其他部分为接收端的眼图。对于LVDS电平而言:TIA/EIA-644A标准规定,如噪声容限为147mV,则最小输出差动电压为247mV,最大阈值电压为100mV。StratixII系列器件的LVDS接口的下降时间最大为180ps,上升时间最大为160ps(注:这里的上升时间和下降时间指的是上升沿和下降的20%到80%这一段长度所占用的时间)。根据这些参数我们设定用于对眼图测试的模板,用于眼图测试的模板为图5中的六边形。

仿真的结果显示:接收端眼图的宽度为2ns,接收端眼图的高度约为300mV,大于LVDS接收端要求的最小眼图高度200mV,接收端振铃小于20mV。接收端的眼图并未碰到模板。传输线D5+/D5-完全可以完成500MHz数据传输的任务。

图5显示的眼图并不完美,有轻微的塌陷和很小的振铃。除去传输线D5+/D5-在不同层的部分阻抗不完全相同存在轻微的反射以外,造成D5+/D5-眼图有一定振铃的原因在于过孔影响。介质损耗和趋肤效应则导致了眼图的轻微塌陷。

在高密度的威廉希尔官方网站 板中信号线的穿层不可避免的带来了过孔。信号线的过孔的阻抗一般是在25Ω到35Ω。过孔的阻抗不连续来自于传输线和过孔处的电磁场的不连续以及除了电源和地平面外过孔处回流路径的缺失。

对于因为过孔导致的阻抗突变而带来的反射,在设计中通常采用在过孔附近增加地过孔的方法来改良信号的质量。增加的地过孔起到了传输线上过孔处回流路径的作用。

导线上单位长度的损耗有两部分组成:一部分是由导线损耗引起的衰减,一部分是由介质损耗引起的衰减。趋肤效应是引起导线损耗的主要原因。介质的耗散因子tan(δ)则是引起介质损耗的主要原因。根据公式(3),在D5+/D5-这段传输线上产生的衰减为:Acond =0.3453dB。输入FPGA的电压幅值为ADC输出电压幅值的96%。

通过更换介质材料可以减少导线带来的损耗,进而改善信号的质量。FR4的损耗因子tan(δ)为0.02,是常用的板材中较高的。更换板材,如RogersRF35(损耗因子为0.0018),我们可以在接收端得到质量更好的眼图。

实测结果

通过上文的理论计算和仿真,在HyperLynx的辅助下解决了500MSPS采样率的AD系统的核心问题即:时钟和数据的信号的完整性。上述仿真结果应用于实际工程中取得了较为理想的效果,实现了AD采样系统的技术指标。图6为用Tektronix示波器看到的ADS5463时钟信号的眼图。

图6 ADS5463时钟信号的眼图

结论

应用HyperLynx的仿真,使得对高速采集板上的阻抗控制变得简单。通过前仿真和后仿真我们能在投版制板之前找到并解决板子中隐藏的信号完整性问题,使得板子一次成功的概率大大提高。相比于价格高昂并且繁琐的EMI测试,HyperLynx提供了一个更为经济有效的设计方法,并且在很大程度上节省了开发周期,使产品更有竞争力。

-

寒烟翠

2015-04-30

0 回复 举报总不至于是用仿真来确定吧? 收起回复

寒烟翠

2015-04-30

0 回复 举报总不至于是用仿真来确定吧? 收起回复

-

寒烟翠

2015-04-30

0 回复 举报最近在学习阻抗匹配这一块儿,请教一下各层的特征阻抗怎么去确定,特征阻抗值的确定是从哪些方面考虑的,是因为器件模型,还是通用规则? 收起回复

寒烟翠

2015-04-30

0 回复 举报最近在学习阻抗匹配这一块儿,请教一下各层的特征阻抗怎么去确定,特征阻抗值的确定是从哪些方面考虑的,是因为器件模型,还是通用规则? 收起回复

-

阻抗匹配中的Hyperlynx应用2008-07-17 0

-

高速PCB设计中的阻抗匹配2019-05-31 0

-

怎么利用HyperLynx解决高速数据采集板中遇到的阻抗匹配的问题?2021-04-06 0

-

Hyperlynx仿真应用:阻抗匹配2008-07-17 1597

-

什么是阻抗匹配2006-09-25 4521

-

关于高速设计中的阻抗匹配的问题2010-03-15 1346

-

高速PCB中的阻抗匹配2017-08-28 1467

-

怎样理解阻抗匹配_pcb阻抗匹配如何计算2018-05-02 42782

-

阻抗匹配是什么意思_阻抗匹配原理详解2018-05-03 50795

-

PCB设计中的阻抗匹配的介绍特征阻抗及常见阻抗匹配的方式详细概述2018-07-12 1998

-

高速数字系统中阻抗匹配与端接方案2019-08-14 8140

-

【硬见小百科】高速PCB设计中的阻抗匹配2019-12-13 2941

-

阻抗匹配的原理及应用2022-08-22 3562

-

为什么高频小信号谐振放大器中要考虑阻抗匹配?如何实现阻抗匹配?2023-10-11 2361

-

什么是阻抗匹配?高速PCB设计为什么要控制阻抗匹配?2023-10-30 2511

全部0条评论

快来发表一下你的评论吧 !