可编程逻辑器件测试

可编程逻辑

描述

可编程逻辑器件 (Programmable Loeie Device,PLD)是一种用户编程实现某种逻辑功能的逻辑器件,主要由可编程的与阵列、或阵列、门阵列等组成,可通过编程来实现一定的逻辑功能。

PLD 按集成度高低可分为简单 PLD 和复杂PLD,简单 PLD包括可编程只读存储器 ( Proerammable Read Onlv Memory,PROM)、可编程逻辑阵列 (Prograrmable Logie Array, PIA)器件、可编程阵列逻辑(Prograrmable Array Logie, PAL)器件、通用阵列逻辑 ( Generic ArrayLogic, CAL)器件;复杂 PLD 包括可擦可编程逻辑 (Erasable PLD, EPLD) 器件、复杂的可编程逻辑 (Complex Programmable Logie Device, CPLD)器件、场可编程门阵列 ( Field Programmable Gate Array, FPGA)器件等。

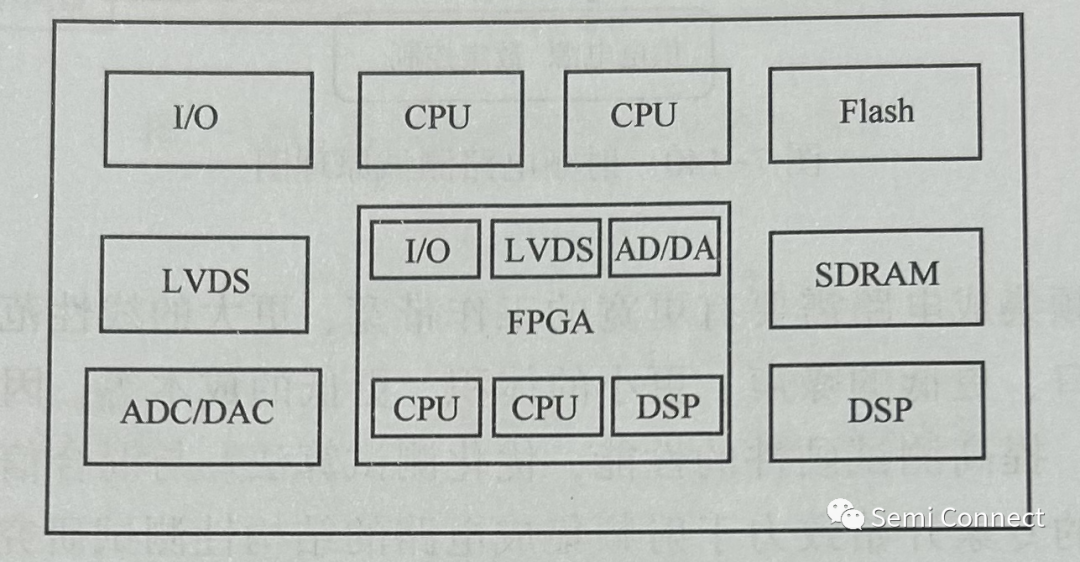

随着可编程器件的发展,可以将 CPU、DSP、ADC/DAC、存储器等集成到一个可编程器件上,从而构成可编程系统芯片 (System On Programmable Chip, SoPC),如图所示。

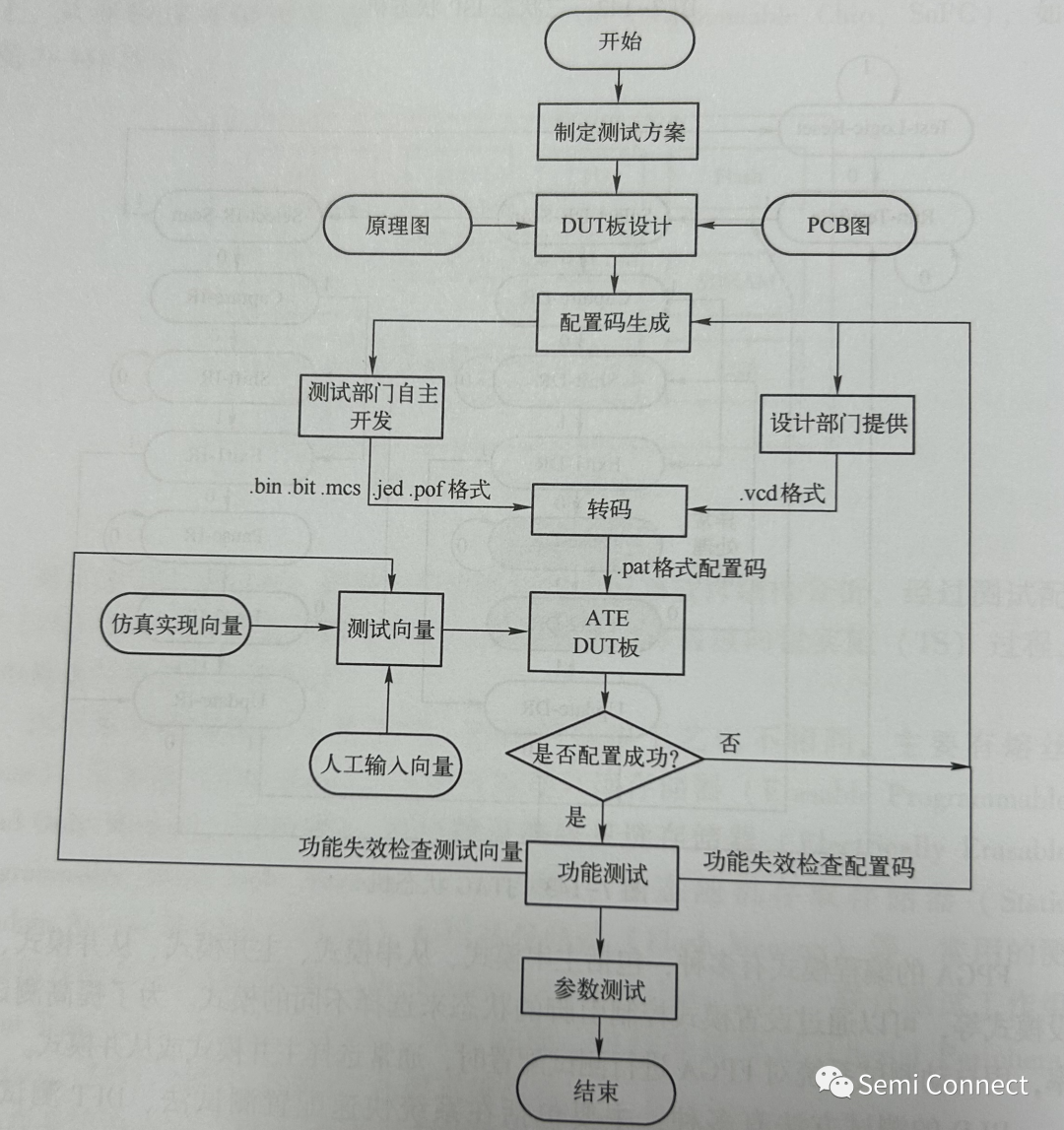

对PLD进行测试时,需要对其内部包含的资源进行结构分析,经过测试配置(TC)将其编程配置为具有特定功能的威廉希尔官方网站 ,再通过向量实施(TS) 过程对威廉希尔官方网站 进行功能及参数测试。

因可编程逻辑单元工艺不同,PLD 的编程工艺也不相同,主要有熔丝(Fuse)、反熔丝(Ani-fuse)、可擦可编程只读存储器 (Erasable ProgrammableRead Only Memory,EPROM)、电可擦可编程只读存储器 (Electrically ErasableProgrammable Read Only Memory, E²PROM)、静态随机存取存储器 (StaticRandom Aecess Memory, SRAM)和闪速存储器(Flash Memory)等。

常用的测试编程方法有在系统可编程 (In-System Programmable, ISP)、联合测试工作组(Joint Test Action Group, JTAG)协议编程、串行外设接口 ( Serial PeripheralInterface. SPI)编程、主模式/从模式编程等在系统可编程 (ISP)技术是莱迪思公司在 20 世纪 80 年代提出的一种先进的编程技术,广泛用于 PROM、CPLD 和 FPGA 等的在系统编程。

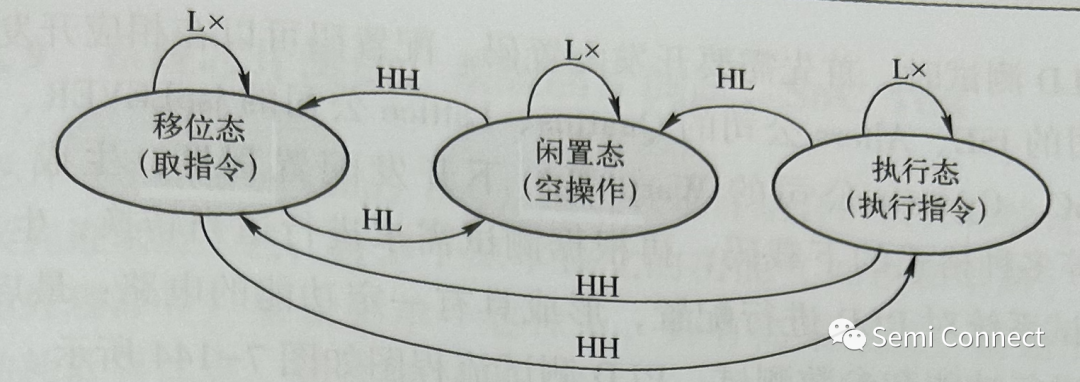

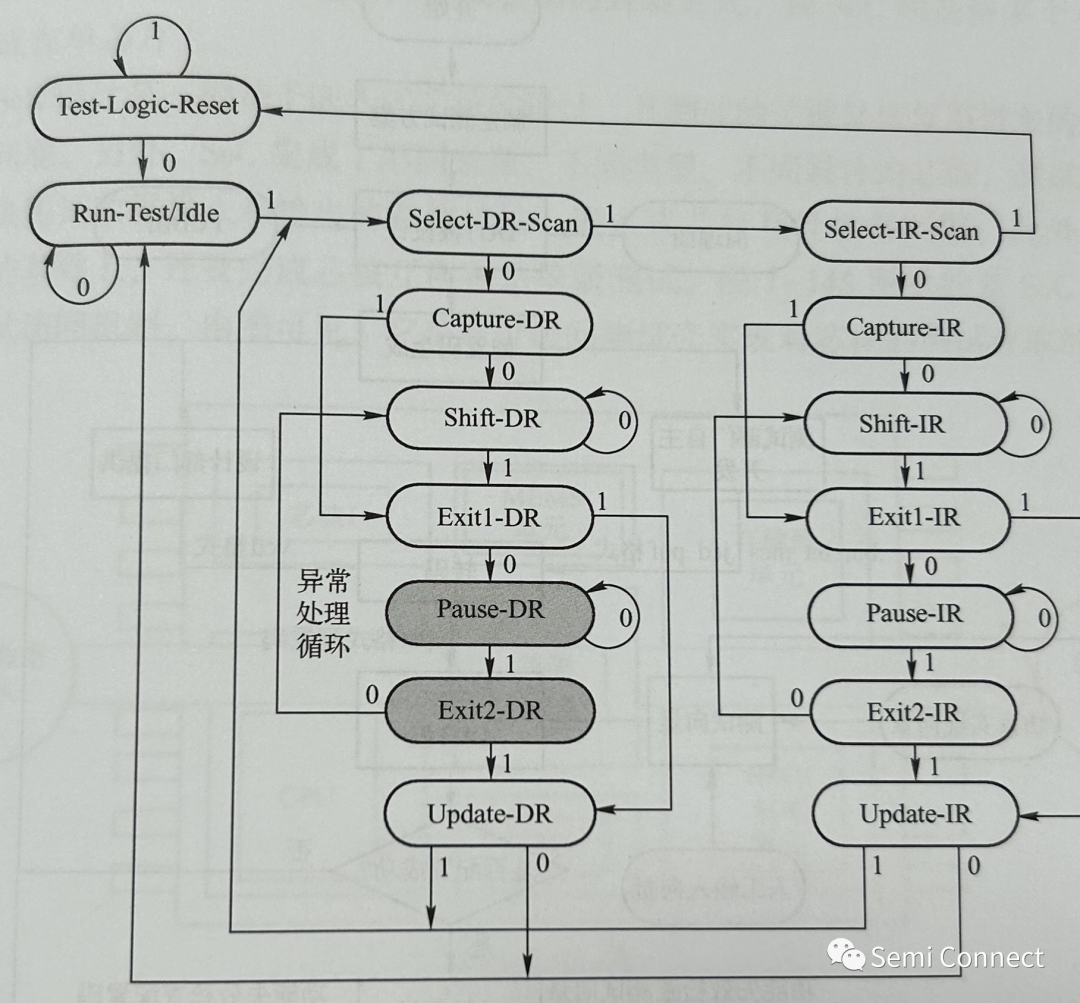

ISP 状态机有两种,即三状态 ISP 状态机和 IEEE1149.1 标准的 JTAG 状态机(见图)。

FPCA 的编程模式有多种,包括主串模式、从串模式、主并模式、从并模式、外设模式等,可以通过设置模式控制 脚的状态水选择不同的模式。为了提高测试效率,用自动测试系统对 FPGA 进行测试配置时,通常选择主并模式或从并模式。

PLD 的测试方法有多种,主要包括在系统快速配置测试法、DFT测试法、内建自测试法(BIST)、扫描测试法(SCAN)、功能级联测试法、基于黑盒的测试法,动态可重构测试法、定制软件测试法、白适应测试法和基于板級应用的测试法等。随着测试技术的发歷,一些新的测试方法不断涌现,要达到较高的湖试覆盖率,需果用多和方法相结合的方式进行测试,进行 PLD 测试时,首先需要开发配置码。

配置码可以在相应开发环境(如XILINX公司的ISE、Altera 公司的 Quartus、Lattice 公司的 ispLEVER、Actel 公司的 Libero SoC、Cypress 公司的 Warp 等)下开发配置程序,生成.bit、.rbt、.bin、.svt 等多种格式的 下载码;再根据测试需求进行适当转换,生成配置码;然后利用测试系统对 PLD 进行配置,形成具有一定功能的威廉希尔官方网站

;最后加载测试码,对威廉希尔官方网站

进行功能和参数测试。PLD 测试流程图如图所示。

审核编辑:刘清

-

可编程逻辑器件2014-04-15 0

-

可编程逻辑器件是如何发展的?2021-04-29 0

-

PLD可编程逻辑器件2021-07-22 0

-

可编程逻辑器件设计2006-03-25 1021

-

可编程逻辑器件基础及应用实验指导书2010-03-24 629

-

什么是PLD(可编程逻辑器件)2009-06-20 26208

-

EDA技术与应用(可编程逻辑器件)2012-05-23 915

-

可编程逻辑器件FPGA/CPLD结构与应用2016-12-11 765

-

可编程逻辑器件(书皮)2022-07-10 455

-

可编程逻辑器件原理、开发与应用2017-09-19 782

-

可编程逻辑器件PLD课件下载2021-08-13 1087

-

电可编程逻辑器件EPLD是如何设计的2022-08-22 1429

-

可编程逻辑器件的结构2023-03-24 1181

-

可编程逻辑器件测试方法2023-06-06 1501

-

什么叫可编程逻辑器件 可编程逻辑器件有哪些特征和优势?2023-09-14 2832

全部0条评论

快来发表一下你的评论吧 !