XILINX FPGA IP之Clocking Wizard详解

可编程逻辑

描述

锁相环基本上是每一个fpga工程必不可少的模块,之前文档xilinx 7 系列FPGA时钟资源对xilinx fpga的底层时钟资源做过说明,但是对于fpga的应用来说,使用Clocking Wizard IP时十分方便的。

Clocking Wizard IP:简化时钟设计代码的开发,用户不用了解FPGA的底层结构,时钟源源语,ip使用图形化界面,根据用户设置选择合适的源语及参数。

它的主要特性包括:

1、支持MMCM及PLL;

2、安全时钟启动功能在输出端提供稳定有效的时钟,顺序启动功能提供了序列输出时钟;也就是说ip能够根据设置,保证时钟稳定后才会输出,同时多个时钟间的输出顺序也可以设置;

3、最大能力支持2个输入,7个输出;

4、提供了一个AXI4-Lite接口,用于动态地重新配置乘、除、相移/偏移或占空比,锁相环输出的时钟可以动态配置;

5、自动计算vco频率,乘法、除法因子;用户只用在IP中确定输入时钟及想要的输出时钟,ip会自动配置响应的vco频率及输出分频比。

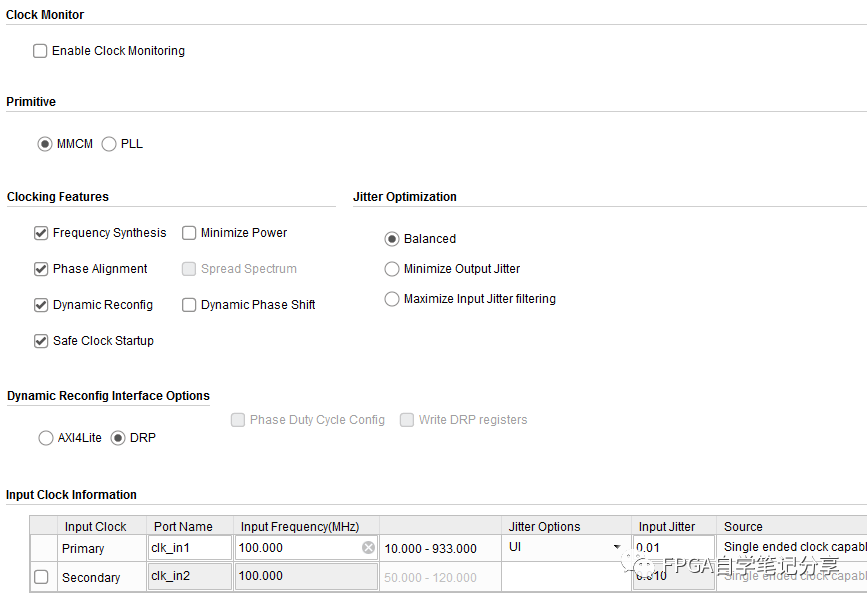

ip设置的第一个界面如下,其中的主要参数为:

Clock Monitor:时钟监控

Frequency Synthesis :频率综合

Minimize Power:最小功耗,牺牲性能

Phase Alignment:输出时钟相位锁定到输入参考上

Spread Spectrum:频谱扩展,降低干扰

Dynamic Reconfiguration:动态重配频率、占空比

Dynamic Phase Shift:动态调整输出时钟关系

Safe Clock Startup and Sequencing:用于稳定输出时钟及时钟序列

Balanced:IP自用优化带宽抖动

Minimize Output Jitter:可能会带来功耗增加及相位异常

Maximize Input Jitter filtering:会引起输出时钟抖动

然后就是两个输入时钟的设置。

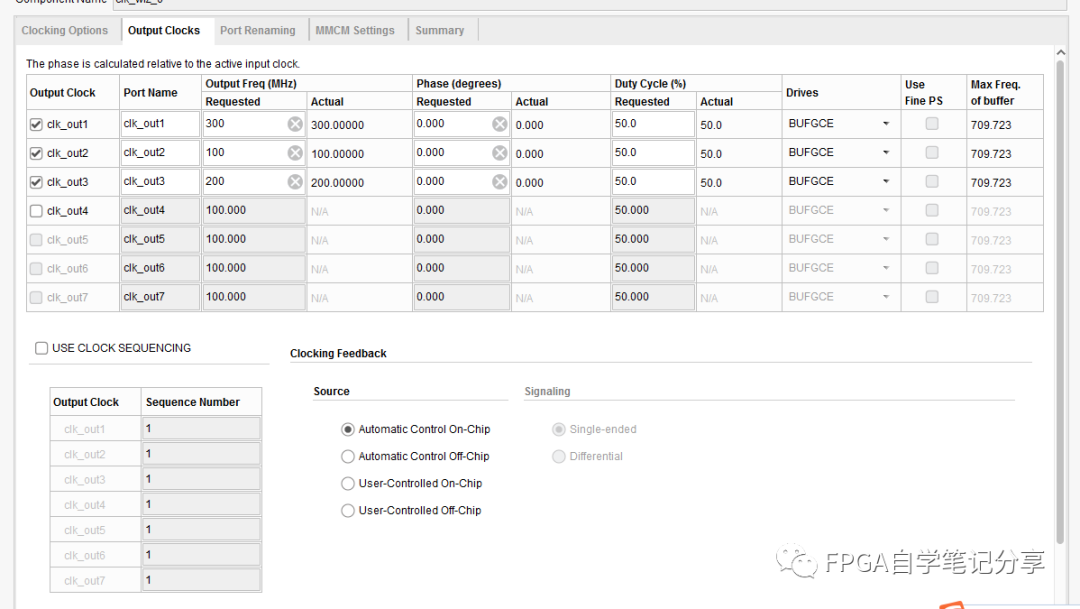

第二个界面如下,对输出时钟进行配置:

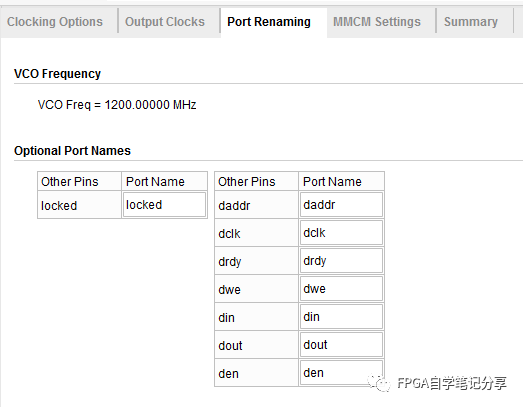

第三个界面如下,显示根据用户配置生成的vco频率及端口。

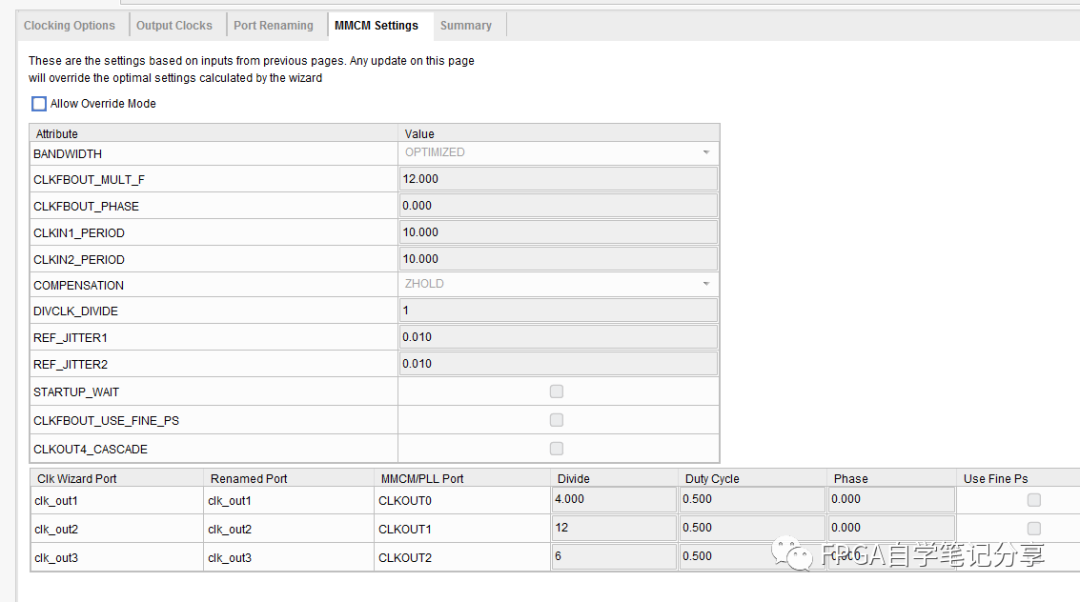

第四个界面如下,这个界面是根据配置生成的乘法倍数及各个时钟的分频数据,这里是允许用户自己修改的。

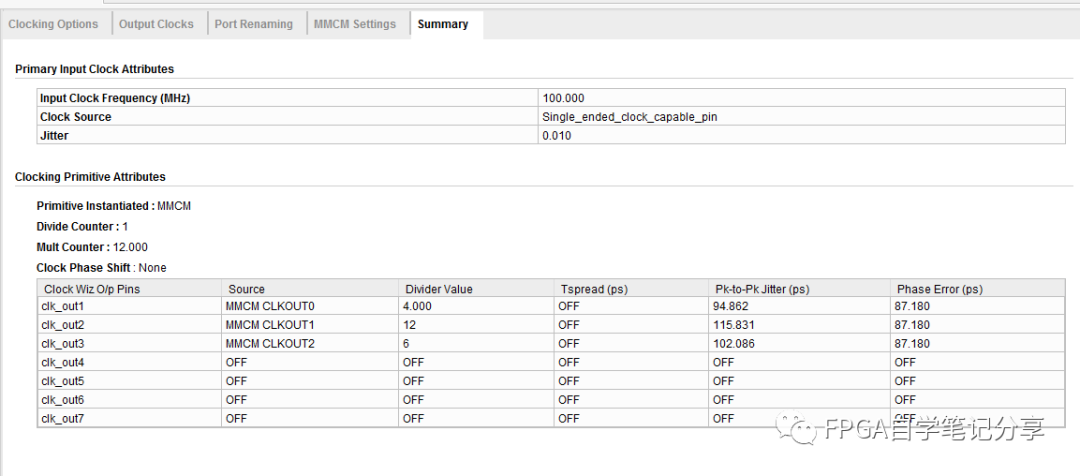

最后就是总结界面了,如下图,是对用户最终设计的总结。

然后就生成了锁相环了,用户可以对其进行例化使用了:

//----------------------------------------------------------------------------

// Output Output Phase Duty Cycle Pk-to-Pk Phase

// Clock Freq (MHz) (degrees) (%) Jitter (ps) Error (ps)

//----------------------------------------------------------------------------

// clk_out1__300.00000______0.000______50.0_______94.862_____87.180

// clk_out2__100.00000______0.000______50.0______115.831_____87.180

// clk_out3__200.00000______0.000______50.0______102.086_____87.180

//

//----------------------------------------------------------------------------

// Input Clock Freq (MHz) Input Jitter (UI)

//----------------------------------------------------------------------------

// __primary_________100.000_____________0.01

// The following must be inserted into your Verilog file for this

// core to be instantiated. Change the instance name and port connections

// (in parentheses) to your own signal names.

//----------- Begin Cut here for INSTANTIATION Template ---// INST_TAG

clk_wiz_0 instance_name

(

// Clock out ports

.clk_out1(clk_out1), // output clk_out1

.clk_out2(clk_out2), // output clk_out2

.clk_out3(clk_out3), // output clk_out3

// Dynamic reconfiguration ports

.daddr(daddr), // input [6:0] daddr

.dclk(dclk), // input dclk

.den(den), // input den

.din(din), // input [15:0] din

.dout(dout), // output [15:0] dout

.drdy(drdy), // output drdy

.dwe(dwe), // output dwe

// Status and control signals

.reset(reset), // input reset

.locked(locked), // output locked

// Clock in ports

.clk_in1(clk_in1) // input clk_in1

);

最后说几点:

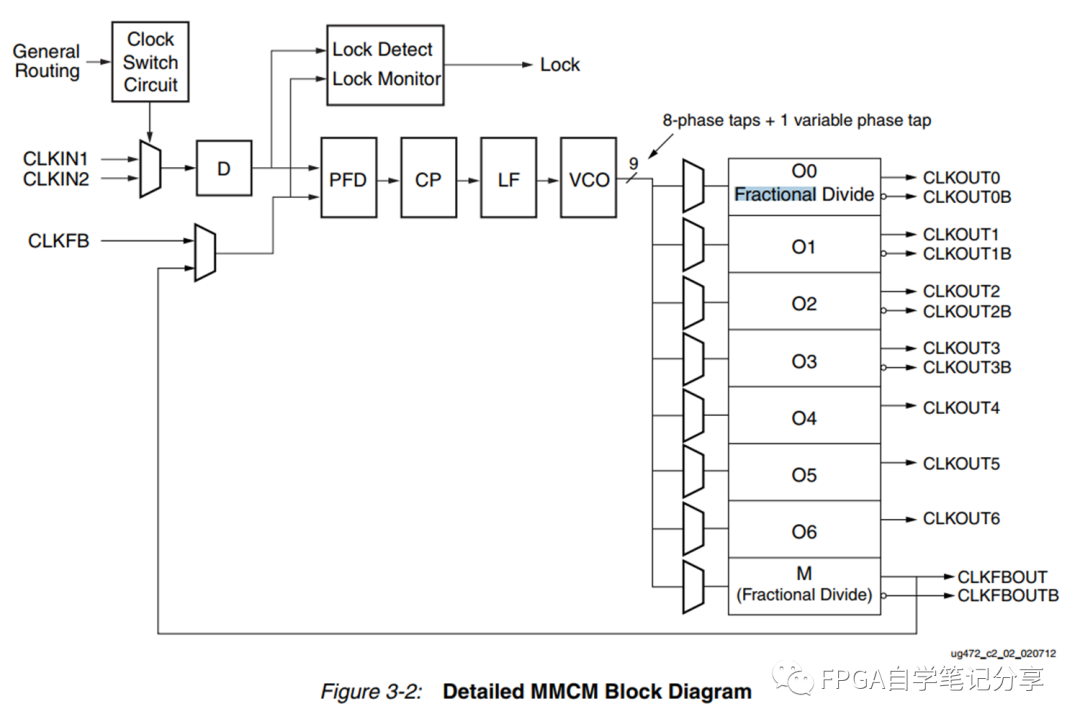

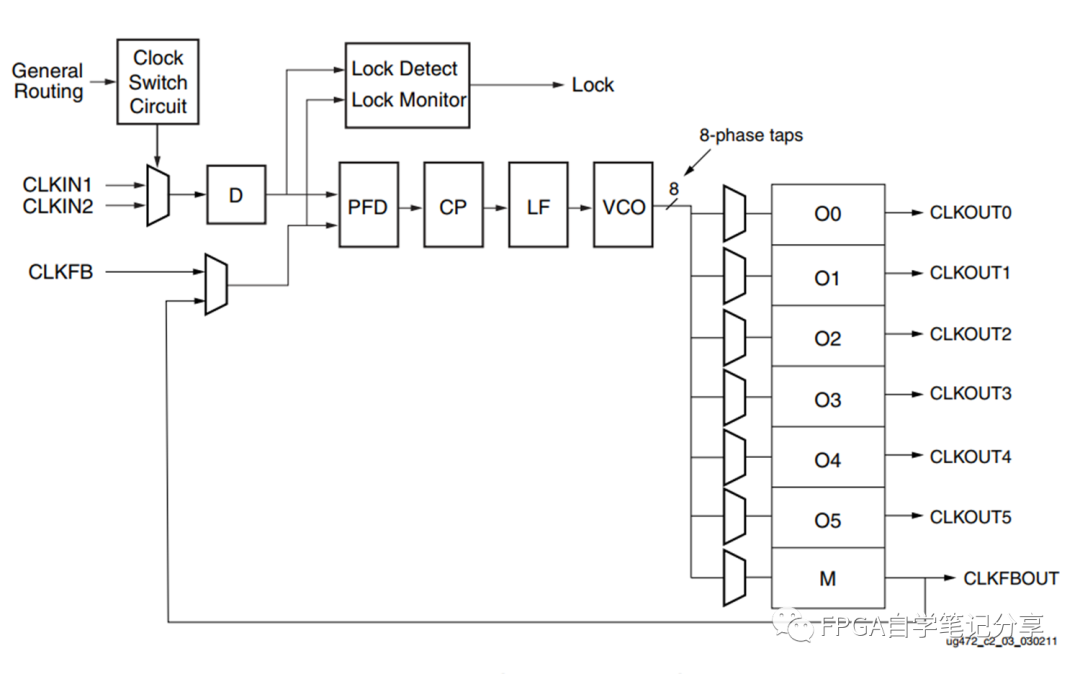

首先是MMCM及PLL的选择,每个CMT包含一个MMCM和一个PLL,他们的结构如下:

MMCM:

PLL:

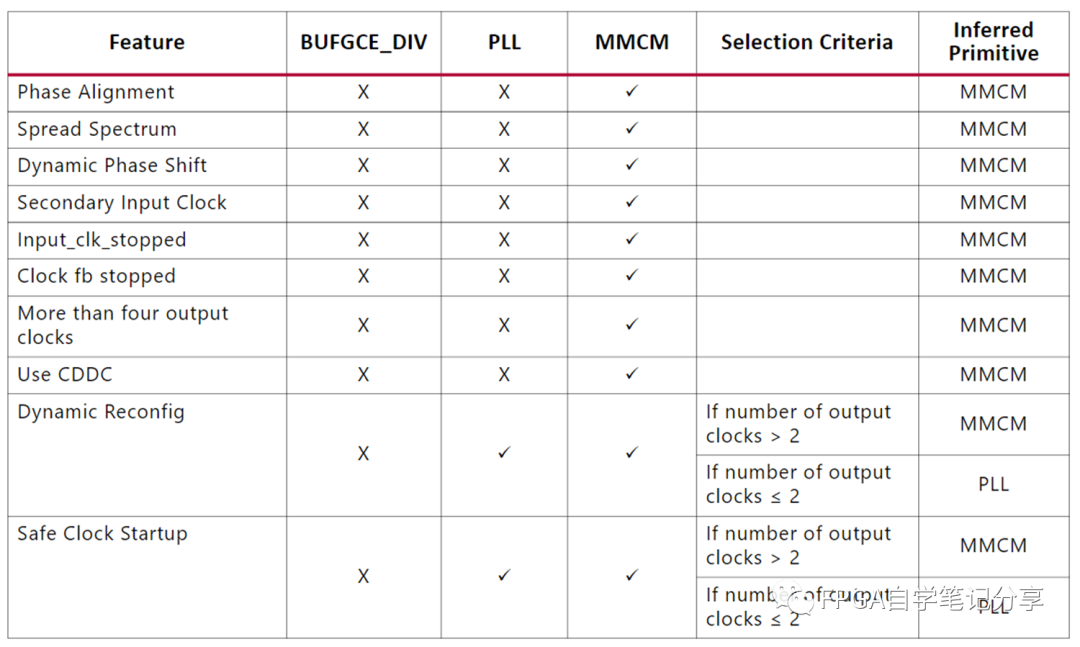

MMCM和一个PLL的详细差别如下表,ip生成时可以根据需要进行选择。

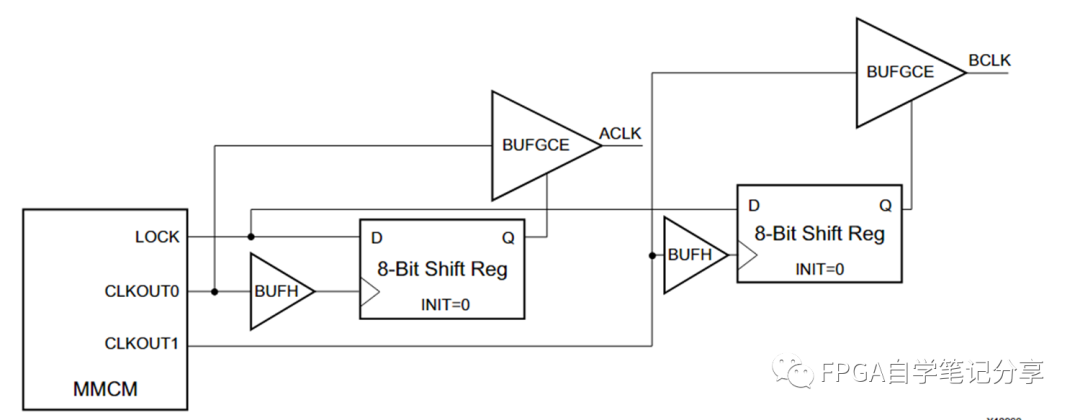

二是关于安全启动模式,如下图,这种模式下只有时钟锁定后才会有是时钟输出,而且时钟输出会经过8bit的移位寄存器,移位寄存器设置不同的delay值,就控制了每个时钟的输出顺序。

-

那位大神有IP核详解资料 万分感谢2015-06-03 0

-

Xilinx FPGA入门连载24:PLL实例之基本配置2015-11-16 0

-

Xilinx FPGA入门连载44:FPGA片内ROM实例之ROM配置2016-01-08 0

-

Xilinx FPGA入门连载48:FPGA片内RAM实例之RAM配置2016-01-22 0

-

Xilinx FPGA入门连载52:FPGA片内FIFO实例之FIFO配置2016-02-29 0

-

Xilinx系列FPGA芯片IP核详解2017-06-06 0

-

Xilinx FPGA片内ROM实例之ROM配置2019-01-09 0

-

Xilinx FPGA入门之PLL实例的基本配置2019-01-21 0

-

Xilinx FPGA怎么动态配置clocking输出时钟相位2019-08-05 0

-

Xilinx CORE生成器IP列表名称及说明详解2017-11-18 4829

-

Xilinx FPGA底层资源架构与设计规范2018-03-21 5014

-

FPGA应用之vivado三种常用IP核的调用2023-02-02 3531

-

XILINX FPGA IP之MMCM PLL DRP时钟动态重配详解2023-06-12 11199

-

XILINX FPGA IP之FIFO Generator例化仿真2023-09-07 1914

全部0条评论

快来发表一下你的评论吧 !