下一代硅光子技术会是什么样子

描述

摘要

在光通信发展的推动下,硅光子技术已发展成为主流技术。目前的技术已经使得集成光子器件从数千个激增到数百万个,它们主要以数据中心通信收发器的形式出现,此外传感和运算等许多令人兴奋的应用领域的产品也指日可待。需要什么才能将硅光子器件的出货量从数百万增加到数十亿?下一代硅光子技术会是什么样子?硅光子应用面临的集成和制造瓶颈有哪些共同点?哪些新兴技术可以解决这些问题?

这篇观点文章试图回答这些问题。我们绘制了硅光子学技术的发展趋势图,从CMOS技术的世代定义中进行了比较。我们确定了在CMOS制造兼容器件、威廉希尔官方网站 、集成和封装方面取得巨大进步所必须解决的关键挑战。我们确定了对下一代系统和应用至关重要的挑战——通信、信号处理和传感领域。通过发现和总结这些挑战和机遇,我们旨在促进对硅光子生态系统的器件、威廉希尔官方网站 和系统的进一步研究。

1.技术路线图

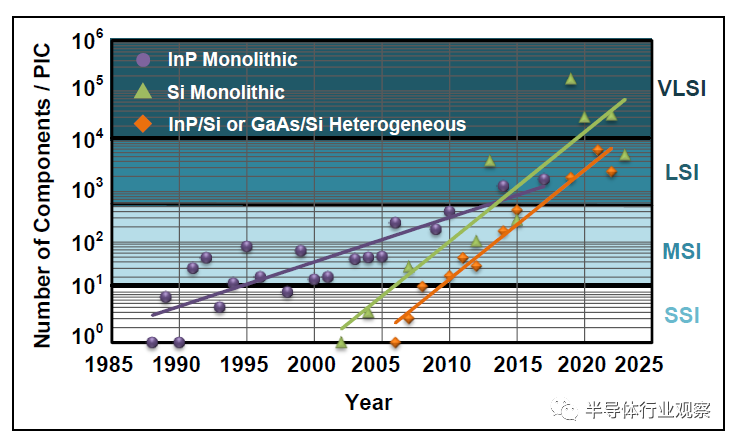

图1 小规模、中等规模、大规模和超大规模集成(分别为SSI、MSI、LSI、VLSI)的硅光子集成威廉希尔官方网站 (PIC)上组件数量的时间线。元件是指与其他单元组合以构建威廉希尔官方网站 的单元,如波导、定向耦合器、加热器、光栅耦合器等。异质硅光子学比混合型延迟约两年。为了进行比较,我们还展示了基于InP的集成光子学的数据。通常,高速调制器的数量越高,缩放就越具有挑战性。

图1展示了硅光子技术的演变。硅基光子集成威廉希尔官方网站 (PIC)于1985年推问世,1991年至1992年在厚绝缘体上硅(SOI)工艺中实现了低损耗波导。接下来出现了各种光学器件。很快,硅光子就进入了小规模集成(SSI)时代——在PIC上有1到10个组件,其中包括高速pn结调制器和光电探测器(PD),以及III-V激光器与硅PIC的异质集成。下一个时代迎来了硅光子的商业成熟。在中等规模集成(MSI)时代,Mach-Zehnder调制器(MZM)成功用在数据中心内的IMDD收发器中——PIC上有10到500个组件,包括单波长和多波长。基于微环调制器(MRM)的IMDD收发器(见图2a)体现了PIC技术的多路复用和能效优势。硅光子/电子平台中的相干收发器证明,该技术可以在性能上与LiNbO3光子和III-V族电子媲美。除了通信,硅光子还有更多新的应用,如倏逝场生物传感器。硅光子现在开始了大规模集成(LSI)的下一个时代——在同一芯片上实现500到10000个组件。LSI的应用包括激光雷达(见图2b)、图像投影、光子开关、光子计算、可编程威廉希尔官方网站 和多路复用生物传感器。甚至超大规模集成威廉希尔官方网站 (>10000个元件)的原型现在也已出现。在通信领域,一直是硅光子的重要市场驱动力,硅光子已经从SSI时代的挑战者技术转变为MSI时代数据中心内和数据中心间互连的主导技术,并有望成为LSI时代的主流技术。硅光子是使共封装光学技术(CPO)取得成功、实现高性能计算的规模化、实现分解计算的关键。

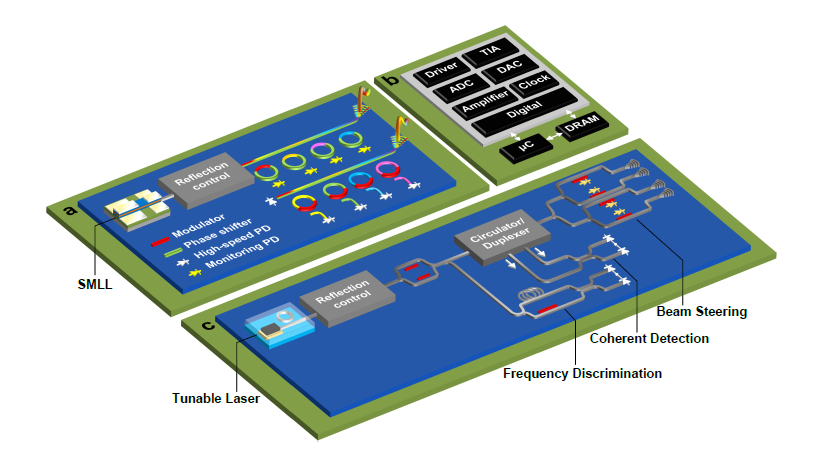

图2 当前和未来技术的LSI硅光子系统的示意图:a.WDM收发器:SMLL向紧凑的、具有WDM功能的调制器和滤波器阵列提供多波长CW光。反射控制威廉希尔官方网站 限制反向反射进入激光器。高速PD执行O/E转换。b.然后电流由TIA和限幅放大器放大。ADC用于将信号数字化以用于进一步的DSP。监测PD用于控制和稳定波长、相移和温度。DAC和驱动器用于数字信号的E/O调制。DRAM提供大的内存访问。微控制器也可以用于进行一些数字处理。c.激光雷达:可调谐激光器为移相器、循环器/双工器和相干前端网络提供频率啁啾光,用于零差/外差FMCW测距和检测。使用OPA/FPA进行光束探测。延迟线干涉仪通过直接控制可调谐激光器或调制器以及通过DSP进行各种形式的误差校正,有助于校准接收到的拍频,并支持线性调频。

2.硅光子技术的技术视角

经过几代CMOS工艺的发展,许多材料被添加到硅中,以降低功率、提高性能和缩小面积——这些通常被称为PPA指标。添加物包括用于金属迹线的Al和Cu,用于诱导应变和实现异质结BJT的Ge,以及用于钝化和扩散势垒的氮化硅(SiN)。CMOS的研发预算和商业市场比硅光子技术大几个数量级。因此,我们在硅光子工艺的发展中也看到了类似的趋势。除了用于高速调制的p/n掺杂剂之外,现在由几个晶圆厂原生支持的两种材料是(1)Ge高速光电探测器和(2)SiN,以扩展波长范围,实现更高的光功率,并在干涉测量器件中支持具有更低损耗和更好相位控制的波导。

缩小面积将是LSI和VLSI时代下一个十年硅光子工艺开发的重点。事实上,最大的密度限制很少来自器件尺寸;消除串扰的波导之间的间距比实际波导的尺寸大得多。对于射频(RF)器件,有源元件之间的间距(临界尺寸为微米)通常为数百微米,以消除射频串扰。缩小这些“空白”需要非常详细的系统级模拟和充分的多物理建模,这将是制造更小、更便宜、更高密度芯片的核心。无源器件本身的尺寸减小通常受到折射率对比度和1-2μm的工作波长的限制。使用反向威廉希尔官方网站 来收缩无源构建块仍有一些余量,但波导本身不能真正收缩到今天硅平台的400-500 nm宽度以下。然而,在光学I/O耦合器和高速调制器中仍然可以实现显著的缩放。为了耦合到光纤,带有边缘耦合器的V形槽以相当大的芯片面积为代价,提供了低损耗、易于顶包连接。没有V形槽的边缘耦合器更小,但需要更精确的主动对准,从而增加了成本。多芯光纤是一种很有吸引力的解决方案。主要的替代耦合方法是通过光栅耦合器,它紧凑的特性提供了在芯片表面上定位的灵活性,能够进行晶圆级测试,并且也可以以低插入损耗(IL)来实现,但存在偏振和温度敏感性以及较低的光带宽。无源对准封装技术,如光子引线键合(PWB),提供了一种有吸引力的潜在替代方案,对其组件进行更多的可靠性研究将有助于其广泛应用。

2.1

E/O 调制

下一个十年的探索旨在缩小光子芯片从而提高密度,即在硅光子中找到难以捉摸的“理想”调制器——长度(L)小、需要小的驱动电压来产生π相移(Vπ)、提供低的传播损耗(α)和IL,对于一些应用,具有高线性和大-3dB E/O带宽(BW)。此外,该调制器优选的是移相器,因为这能够实现更高阶相干调制格式。

2.1.1 高速调制器

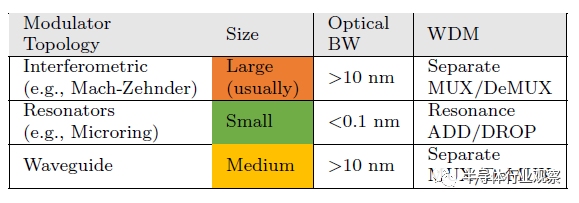

基于波导的调制器(表1)的常用效率品质因数(FoMeefficiency)为αVπL。对于非常紧凑的MRM,由于α引起的损耗变得不那么关键,并且更好的FoMeefficiency包含IL和Vpp(特定光学调制幅度或OMA的峰间电压摆动)。所有调制器都要在FoMeefficiency和E/O BW之间进行权衡。最后,驱动器中消耗的功率取决于驱动器所看到的调制器阻抗。电阻阻抗(端接行波调制器)消耗静态(DC)和动态(AC)功率,而高阻抗(电容性)主要消耗动态功率。由于需要增加激光功率来补偿损耗,因此高IL也是较高功耗的代表。

表1 不同调制器拓扑结构的比较

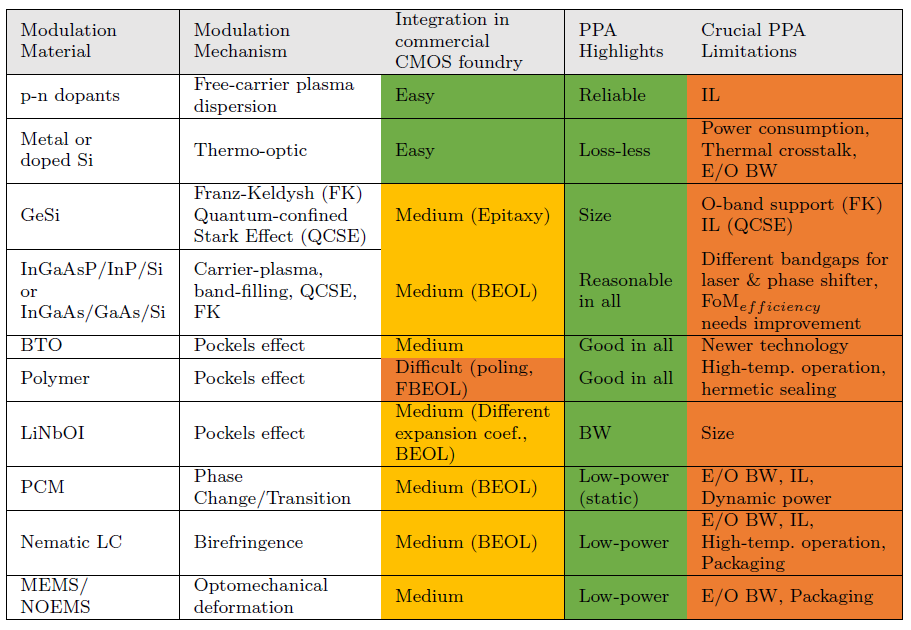

除了拓扑结构之外,调制器的PPA度量还取决于用于调制的材料和机制。表2显示了在各种硅光子工艺中用于调制器的不同材料。利用自由载流子等离子体色散的p-n掺杂剂目前在所有商业硅光子晶圆厂都可以买到,支持60 GHz甚至更高的E/O BW。目前,商业市场主要由行波MZM调制器形式的此类器件主导。等离子体在硅中的分散导致了中等的FoM效率,对于平均OMA具有高的IL。载波积累允许较短的MZM,但有BW限制。当实现为MRM时,器件要小得多,但IL和OMA对于支持LSI/VLSI IC来说仍然是次优的。

表2 比较不同的调制材料和机制在商业CMOS晶圆厂的集成情况以及功率、性能(截至2023年)和面积(PPA)指标方面的情况

由于Ge PD已经得到了大多数商业硅光子晶圆厂的支持,各个团队都试图使用GeSi,一种相关但不完全相同的技术,来实现更好的调制器。基于Franz-Kelydysh效应的GeSi电吸收调制器(EAM)可以在高E/O BW的C/L波段工作。然而,它们通常不是光学宽带,因为它们使用带边调制进行吸收。对于O波段操作,利用量子受限斯塔克效应(QCSE)的调制器仍然存在较大的IL。虽然在这一领域已经进行了多次学术和商业探索,但尚不清楚这些调制器是否会进入未来几代的商业器件。

InP到CMOS的异质集成已经引起了电子和光子学研究者的兴趣。对于光子学,它为IMDD收发器的大批量制造(HVM)中的激光集成铺平了道路,并正在用于SOA集成。鉴于这些集成努力,InP/Si调制器仍然非常有前途。用于C/L/O带的InP/Si EAM已经被证明,并且在至少一个硅光子晶圆厂中可用。

最“纯”的电光调制依赖于Pockels效应,它提供了本质上非常高的E/O BW,甚至超过100 GHz,但这些材料在CMOS集成方面面临诸多挑战,并且很少或根本没有与CMOS集成用于电子器件的历史(与已经在CMOS电子器件中引入的Ge和SiN相比)。绝缘体上LiNbO3(LNOI)调制器提供低IL,并已与源极和PD集成。然而,其αVπL产物需要进一步解决。锂是CMOS制造厂的污染物,其使用可以使用BEOL集成或封装技术来解决。聚合物-硅-有机杂化物(SOH)和等离子体-有机杂化体(POH)需要极化和气密密封,这给制造稳定的器件带来了重大挑战。尽管最近的结果很有希望,但它们的高温可靠性和回流兼容性仍有待进一步证明。POH调制器,尽管它们在PPA指标中看起来很有吸引力,但与CMOS SOI制造的兼容性更差。良好的等离子体金属(Cu、Ag、Au)也是严重的污染物,并且需要光学损耗很大的扩散阻挡层(例如TaN)。铁电薄膜材料(如BaTiO3)的多晶层显示出比LNOI大得多的Pockels系数(以pm/V表示),并且与聚合物相当,最近大的E/O BW的证明使它们很有前景。注意,器件中的大波克尔系数是非常重要的,这需要电调制场和传播光学模式的良好重叠。一般来说,对Ge PD处理和回流的兼容性将是商业晶圆厂采用新调制器技术的要求。

改善所有PPA指标和HVM适用性对于商业晶圆厂和LSI应用至关重要。然而,由于大量的光子应用,将始终需要极高的E/O BW调制器,一些专注于原型和研发晶圆厂将继续解决相关的制造挑战。最后,尽管>100 GHz E/O BW调制器对电信和数据中心应用都很有吸引力,但它们需要能够以这样的速度驱动它们的电子器件。除非Vπ(或Vpp)显著降低,否则无论CMOS/BiCMOS/III-V实现如何,这种电子器件都将消耗大量功率。

2.1.2 用于调谐和切换的移相器

许多光子应用需要消耗很少或不消耗功率的移相器,并且具有用于配置、调谐和切换的低αVπL。对于某些应用,这些移相器也应该具有很高的速率,但不需要10GHz E/O BW。虽然在许多威廉希尔官方网站 中,光只通过一个高速调制器,但它必须穿过许多低速移相器进行调谐和切换。利用热光效应的金属加热器(或掺杂波导),如今可用于所有制造平台。它们具有1-10μs的响应时间,并且消耗相当大的功率,产生热串扰,从而限制LSI/VLSI的缩放。改善热绝缘降低了它们的功耗,但代价是更高的响应时间。

图3b中列出的最后一组材料和技术是加热器的有吸引力的替代品。它们包括液晶(LC)、MEMS/NOEMS和相变材料(PCM)。用于显示应用的硅上LC(LCOS)调谐已经被大规模地证明,并且LC也是自由空间波长选择开关的选择技术。作为移相器,它们使用极低的功率,但目前受到IL的影响,尽管最近在可见光波段已经证明了极低的IL。芯片上的液体集成带来了一系列温度和封装方面的挑战,基于PCM的非易失性存储器已经在电子工业中实现了HVM,并且正在被探索用于神经网络应用。PCM在硅光子中的使用承诺了紧凑的调谐能力,但存在高IL和显著的动态功耗。基于MEMS/NOEMS的移相器本质上是低功率的,并且已经在多家晶圆厂进行了验证。诸如用光学和电气馈通进行气密密封等挑战是可以解决的。最后,BaTiO3等材料有望实现高速调制和高效相移,但代价是面临非常严峻的技术和经济整合挑战。

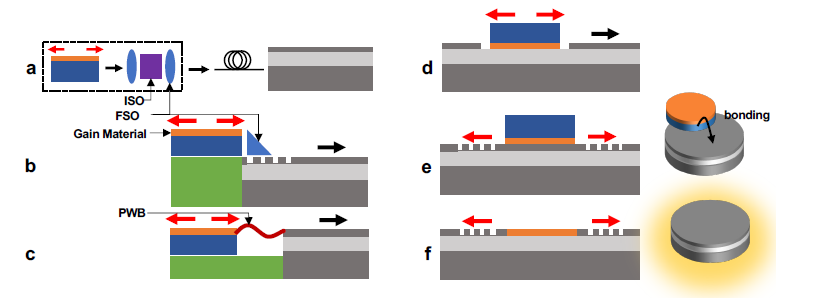

图3 将激光器连接到硅PIC的技术。a.具有自由空间光学(FSO)的常规激光隔离器光纤PIC b.具有FSO的混合2.5D。c.带PWB的混合动力2.5D。d.混合3D(倒装芯片或转移打印)。e.异质(直接键合或转移印刷)f.单片(异质外延)。

2.2

激光集成

硅的间接带隙阻碍了PIC上的激光器(CW载波)所需的有效光学增益。这种缺陷需要替代材料或方法在硅片上引入光源,过去几十年的发展中涌现了不同的解决方案(图3)。传统技术是用激光器和隔离器将PIC光纤连接起来(图第3a段)。更具可扩展性的方法将III-V族增益材料与不含光纤的PIC集成在一起。但是,如果激光器不能容忍反射,仍然需要一个隔离器。芯片外隔离器性能良好,但体积庞大,增加了封装复杂性和成本。务实地说,通常可以设计芯片和封装,避免背反成为限制因素;传输路径中的高损耗在外部世界和任何光源之间提供了屏障。当设计成封装时,可以管理紧凑型隔离器的成本。芯片上反射控制方法(图2)可以消除对大体积隔离器的需求,包括仔细设计光子组件以将反射降低到激光器的容差阈值以下、通过使用具有低线宽增强因子的量子点增益区域来降低激光器的反射灵敏度、磁光材料的单片集成(例如,Ce:YIG)、时空调制器或有源反射消除威廉希尔官方网站 。一种对近端(相干)和远端(非相干)调制多波长反射具有鲁棒性的通用、低成本、可扩展、片上、低损耗、低功耗和紧凑的解决方案仍然是一个研究问题。

激光集成的一个实用解决方案是混合集成,将来自不同材料技术的多个芯片共同封装在一起。例如,为数据通信应用制造并经过预测试的低成本高产量的(亚)毫米DFB激光器可以与硅光子芯片共同封装。一种商业上成功的2.5D集成技术将已知良好的激光器同环氧树脂、球透镜和隔离器共同封装(图第3b段)。其他2.5D技术包括使用对接耦合或光子引线键合来实现松弛的对准公差(图3c)。这些2.5D技术足以用于当今的几种定制硅光子应用。混合3D集成技术(倒装芯片或微转印)有望以使用PIC区域为代价进一步缩小组件尺寸(图3D),但需要高精度的放置和粘合。

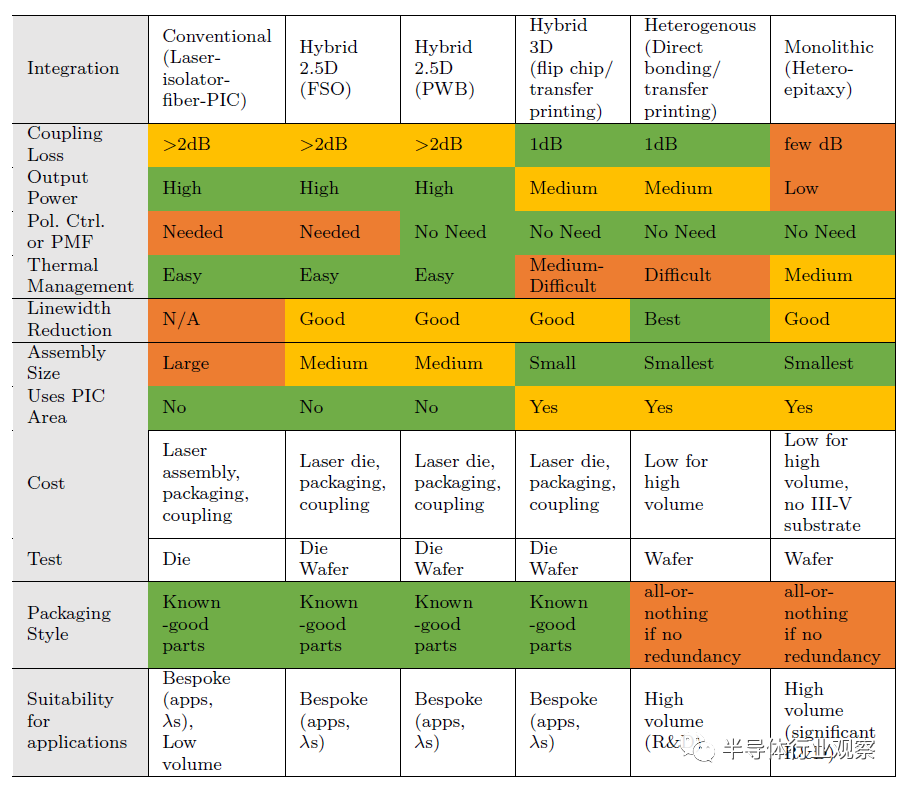

表3总结了各种集成方案的PPA和其他指标。大多数C/L/O波段激光器的壁塞效率(WPE)仅约为10%,这一指标需要更集中的研究来改进。对于类似的WPE,激光器与PIC之间的耦合损耗可以作为功耗的代表。在2.5D混合集成中,单独的激光器提供了选择具有所需光功率的激光器的灵活性,并且热管理也很容易。为了实现更高的功率处理,可以在PIC上使用SiN。有一些方法可以从DFB的典型线宽提高激光器的线宽,也可以消除反射以提高隔离。具有高Q Si或SiN外腔的3D技术支持将线宽降低至1 Hz及更低,足以用于相干通信和汽车激光雷达等应用。混合集成还允许多个波长。尽管如此,相对于需要多个激光器、增益元件等的>8λWDM LSI PIC的扩展,混合集成的好处仍有待彻底证明。

表3 从PPA指标(截至2023年)、成本、测试、封装方式和应用适用性方面比较将激光器连接到硅PIC的不同技术

HVM中另一项商业上成功的技术是异质集成,即在晶圆级将多种材料或外延堆叠一起加工成一个硅片。此外,还采取了各种战略,它们包括通过粗对准将III-V族芯片结合到Si上,然后对Si晶片进行后处理以制造量子阱(QW)激光器(图3e)。为了实现高温操作、效率和可靠性,必须仔细解决掩埋氧化物(BOX)对增益介质的热隔离和不匹配的热膨胀系数问题。放置冗余激光器有助于提高故障及时率。异质方法的好处包括亚dB耦合损耗,这是一种利用硅中的低损耗外腔使用自注入锁定显著降低激光线宽的机制。

量子点(QD)激光器所需的另一种长期方法是在硅晶片上直接生长外延增益材料。由于其较低的线宽增强因子αH,QD激光器能够实现较低的带宽和降低的反射灵敏度。它们还具有较低的阈值电流密度。使用异质外延生长的单片集成(图3f),其中甚至不需要III-V衬底,仍然是最终目标。

多家硅光子晶圆厂正在开发混合或异质激光解决方案。出于可扩展性的目的,它们可能会倾向于支持多波长的技术,这对一些LSI应用至关重要。很可能首先通过结合多个单波长激光器来支持横向扩展。梳状激光器,如无源半导体锁模激光器(SMLL),正被各种研究小组积极研究。DFB阵列确保在每个波长中都有大的输出光功率,而在SMLL中,功率在波长之间分配,降低了SNR。可饱和吸收体的存在进一步降低了SMLL的总输出功率(并因此降低了每波长)。然而,SMLL明显小于DFB阵列。无源SMLL的线宽通常低于DFB阵列。预计SMLL将在未来十年进行更多的研发,以展示更高的功率、可靠性和寿命。这种对DWDM应用的要求甚至更严格,任何温度漂移都会产生通道间串扰。

2.3

雪崩光电探测器

大多数硅光子应用受到激光器输出功率和WPE有限以及威廉希尔官方网站 中高IL的限制。一种替代方案是在检测阶段提高SNR(图2)。低电压APD具有大的-3dB O/E BW、高的整体响应度和同时低的噪声,将有利于提高接收机的信噪比。需要注意的是,整体响应度(以A/W为单位)和低噪声至关重要。具有差的固有响应性的APD的大的倍增增益不会延伸出优越的性能。尽管在硅APD中相对更容易实现,但同时优化增益-BW噪声对于低电压Si/Ge APD来说仍然具有挑战性。与Ge PD相比,APD通常具有较差的BW、线性度和功率,这限制了它们在各种应用中的使用。APD还需要针对温度和电压漂移进行最佳偏置和稳定,但这也比已经证明的微环威廉希尔官方网站 具有更小挑战性。

3.硅光子技术:系统视角

3.1

光子&电子相辅相成

硅PIC几乎总是与电子IC(EIC)一起存在。当我们审视基于光子芯片的系统时,今天的格局几乎100%由数据通信主导,我们预计这种情况将在不久的将来继续持续下去。在这种情况下,EIC有几个用途(图2):(1)启用端到端数据的E/O和O/E转换。(2) 对温度和制造变化进行偏置、控制和补偿。因此,光子学通过提供数据链路为电子器件服务,而电子器件通过提供控制和读出以及数字信号处理(DSP)为光子学服务。光子学和电子学之间的一个主要区别是,光子不相互作用,因此非常适合信息传输,而电子相互作用并相互排斥,因此是很好的开关和计算元件。因此,每个硅光子开关都需要相应的电子开关。总的来说,必须伴随LSI PIC的EIC中的晶体管数量比PIC中的组件数量大几个数量级。这是一种自然的相互作用,因为晶体管在(1)开关、(2)提供增益(线性和限制性)和(3)提供高精度时消耗的功率要低得多,同时比光子组件小几个数量级。另一方面,与铜相比,光子组件(1)在较长距离上移动数据时能够实现较低的频率相关损耗,(2)可以通过异步和无中继器的数据移动提供较低的延迟,以及(3)使非常高速的数据在光波导上的并行性(通过WDM)变得容易。当数据已经在光域中时,光子信号切换或处理可能会变得有吸引力。前者是一种广泛部署的技术,而后者尚未实现从研究到产品的飞跃,以取代DSP的功能。因此,认识到PIC和EIC技术各自的优点是很好的。例如,必须仔细分析光子域中处理电子数据的E/O和O/E开销。相反,硅光子技术为缩小大型光学系统提供了机会,并将新的应用(如传感和成像)带到了现实中,而电子技术本身无法实现这些应用。最后,硅光子技术在数百太赫兹的载波上工作,而硅电子器件仅限于亚太赫兹。这种不同的属性开启了有吸引力的共同设计机会,例如设计具有超低相位噪声的电子时钟。

3.2

光子&电子生态系统

摩尔定律表明,每一代CMOS技术都会降低晶体管的关键尺寸,从而降低每个组件的成本。随着时间的推移,半导体行业的经济规模呈指数级增长,这使得该行业能够为越来越昂贵的晶圆厂和工艺开发买单。晶圆厂使许多用户能够访问这些高级流程,而无需每个用户自己付费开发流程。在最极端的情况下,晶圆厂托管的MPW(多项目晶圆)运行允许多个用户分担单个晶圆运行的成本,以经济高效地开发产品。

随着工艺的成熟,产量上升并且成本下降。晶圆厂和第三方知识产权(IP)供应商能够提供工艺设计工具包(PDK)和设计IP库,使客户能够构建极其复杂的电子威廉希尔官方网站 ,并在第一时间将其做好。通过依靠久经考验的器件和久经考验的威廉希尔官方网站 级IP,设计师可以专注于片上系统(SoC)集成,而在某些情况下永远不会触及晶体管级别。

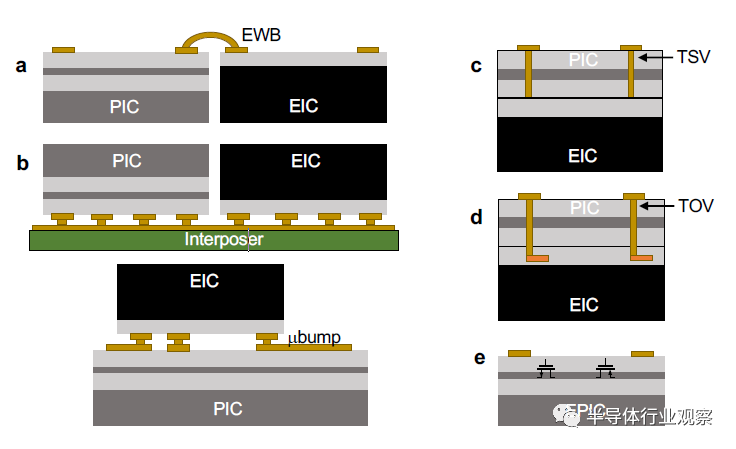

一旦芯片被制造出来,就会有一个由测试公司、封装服务提供商等组成的丰富生态系统。引线接合(图4a)和倒装接合(具有C4凸块和微凸块,图4b)是可靠且流行的封装方式,后者提供更多的凸块而不仅仅是外围连接。更先进的封装技术(见图4),如通硅过孔(TSV)、无TSV内插器和异质集成,用于通过将复杂的大型SoC分解成更小的小芯片来提高信号完整性、功率和热分布以及管芯成品率。由于FPGA、GPU和CPU都是在HVM中生产的,尽管封装技术复杂,但总体成本仍在下降。然而,明智的封装决策是为了避免不必要的复杂性;一般来说,最简单的封装是最好的,并且只有在没有其他替代方案可行的情况下,才会引入先进的封装技术(晶片上芯片、芯片堆叠等)。

图4 比较将PIC连接到电子IC(EIC)的不同技术:a.并排电引线接合(EWB)b.2.5D 倒装芯片并排或堆叠c.混合3D TSV(穿透硅通孔)d.具有TOV的异质3D(穿透氧化物通孔)e.单片EPIC。

光子学行业有几个相似之处,但也有许多明显的差异。就像在电子行业一样,增加光子组件的数量并不总是为了降低成本,而是为了提供新的功能、提高性能或减少每个组件的面积。尽管成熟的PDK和抽象语言仍处于非常早期的阶段,但现在许多晶圆厂都可以运行MPW。到目前为止,第三方知识产权支持基本上不存在。公司采用最先进的PIC工艺来保护其投资和知识产权。这让人想起CMOS行业的前几十年,作为虚拟集成器件制造商(IDM),在工艺和PDK层面保持差异化。同时,学术研究主要集中在器件的改进上。

光子晶圆厂面临着一个重大的困境:他们的客户经常要求他们定制工艺,这涉及到大量的研发费用,并危及最终晶圆的可靠性和产量。推动客户进入标准流程是解决这一问题的解决方案,但为了做到这一点,客户需要看到稳定性以及稳定的PDK和IP生态系统中的重大价值;只有少数设计师是这样看待问题的,因为今天设计界的许多成员都是作为器件设计师而不是SoC设计师接受培训的。在这样的设计者看来,改变工艺参数通常是产生性能差异的最简单方法,但从可靠性和工艺维护的角度来看,这种改变的下游成本可能非常高。随着越来越多习惯于固定PDK想法的设计师毕业并进入该领域,破坏性的流程变化将慢慢变得越来越不常见;晶圆厂也可能会越来越抗拒来自客户的流程变化,而这些变化并没有得到大量采购承诺的证明。

3.3

光子&电子共同集成

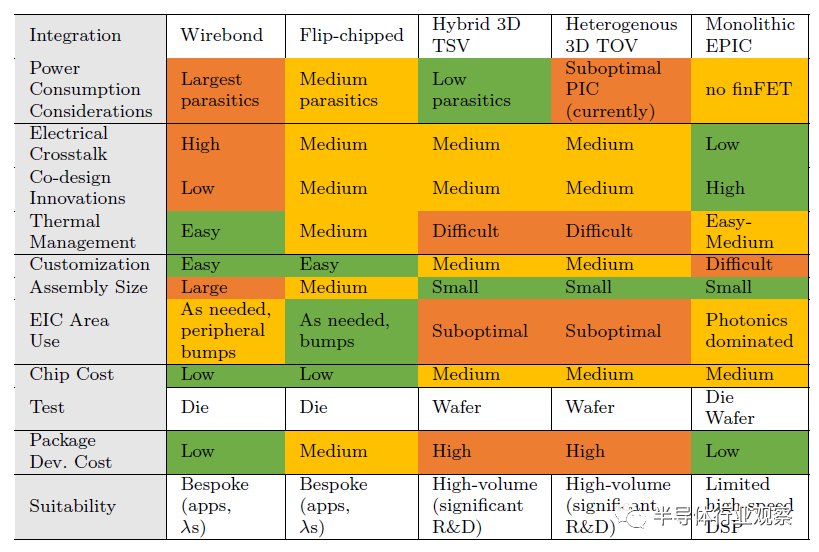

自从第一个商业上成功的硅光子产品问世以来,PIC与EIC集成的选择就一直存在。开发单片EPIC工艺(图4e),从CMOS(或BiCMOS)SOI工艺开始,并针对光子应用对其进行优化,已多次获得成功。从商业化和上市时间的角度来看,单片EPIC通常“似乎”是首选的优越技术(表4)。驱动器和TIA等高速威廉希尔官方网站 可以与调制器和PD并排放置,从而减少寄生效应和功耗。控制器(热、波长)可以被设计并放置在光子组件旁边,而不需要专用焊盘。对于LSI应用,单片EPIC可以显著简化封装复杂性。然而,当管芯区域由光子(光子元件比电子元件大几个数量级)主导时,在没有充分利用CMOS器件的情况下,整体管芯成本可能会显著增加。这种分析必须针对个别产品逐一进行。

表4 在PPA指标(截至2023年)、成本、测试可能性、封装风格和应用适用性方面比较将PIC连接到电子IC的不同技术

原则上,在开发出具有卓越FoMeefficiency的下一代调制器之前,基于微环的威廉希尔官方网站 似乎对单片EPIC工艺非常有吸引力(第2.1.1节)。但要得出它们在给定的特定应用中是否有意义的结论,需要进行完整的系统分析;微环具有相当大的控制开销和性能权衡,尤其是在非常高的速度下。如果应用需要高速ADC/DAC,尤其是DSP(图2),还必须添加另一个finFET EIC以节省功耗,因为目前在45 nm CMOS SOI中最快的单片EPIC工艺仍然比finFET工艺慢几代(扇出延迟)。在未来几年内,将光子组件直接集成到45nm节点以下的CMOS晶片上的可能性不大;在PICs和规模微电子之间的片上键合相对简单的世界里,这样做在经济或技术上都没有意义。

EPIC的其他可能性也被广泛探讨。将光子添加到上一代CMOS工艺中会导致高功率、较慢的驱动和TIA,从而导致更糟糕的收发器设计,并使其对硅光子的最大客户——数据通信和电信——没有吸引力。尽管如此,这样的过程对大学研究人员很有吸引力,因为它为以低成本和封装努力共同设计和创新新的EPIC威廉希尔官方网站 开辟了机会。另一方面,正在进行多项努力,将双极晶体管集成到与硅光子器件相同的晶片上。然而,到目前为止,这样做依然涉及对双极电子器件的性能的不可接受的妥协。

目前HVM中的大多数硅光子收发器都基于2.5D集成方法,其中PIC和EIC在其各自的最佳工艺中进行设计、尺寸确定、优化、测试,然后倒装到中介层基板上(图4b,表4)。EIC工艺可以从众多CMOS/SiGe晶圆厂中选择。多个EIC芯片也可以是倒装芯片,例如(1)具有相当大的击穿电压的SiGe芯片或缩放CMOS芯片,以允许高摆动驱动器和合理的开关速度来支持RF速度要求,以及(2)用于DSP/ADC/DAC的高级FinFET芯片。具有更快晶体管的EIC工艺甚至可以补偿由于额外的焊盘、ESD和布线(与单片EPIC解决方案相比)而产生的寄生电容。对于大多数PIC组件需要相对较低速度的电子器件(如激光雷达)的LSI应用,倒装芯片解决方案似乎是合理的。然而,对于需要许多高速驱动/读出线的LSI应用,倒装芯片解决方案意味着内插器上有许多RF迹线,这导致了复杂性和串扰问题。在任何一种情况下,由于需要许多I/O凸块,PIC的尺寸都会增加,尽管使用微凸块和铜柱技术,但这些增加在商业上通常可以忽略不计。在某些情况下,可以考虑混合3D集成,其中EIC在(较大的)PIC芯片上倒装,并使用先进的技术,如硅通孔(TSV)(图4c,表4)。RF线路仍然需要从小型EIC布线到PIC上的几个地方,这仍然具有挑战性。异构3D集成也在研究中,在这种集成技术中,光子组件的性能有望得到进一步改进(图4d,表4),其中一种可能性是使用集成在PIC上的多个EIC 3D。

总的来说,应用、性能规格和发货量(影响成本)将决定更昂贵的单片EPIC(具有更简单的封装)、多芯片2.5D集成(具有更复杂的封装)还是3D集成(具有更加复杂的处理/封装)哪种是正确的选择(表4)。我们预计所有这些场景都将共存,就像在电子生态系统中一样。

4.硅光子技术:应用前景

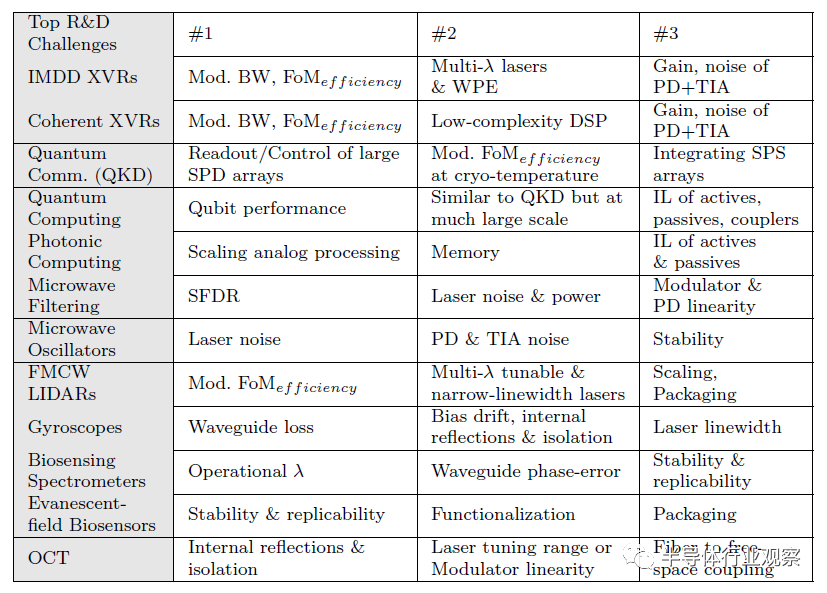

在本节中,我们描述了各种硅光子应用成功的主要技术障碍(表5),将它们与前几节中讨论的一些挑战和机遇联系起来。我们仅限制PIC/EIC技术的障碍,不包括经济、监管、市场和其他因素,如化学、生物标志物、量子优势等。我们也没有深入研究硅光子对这些应用的好处,因为之前的大多数工作都对其进行了详细描述。

表5 硅光子在通信、计算、信号处理和传感领域的各种应用面临的最大技术挑战(截至2023年)

为了使IMDD收发器进一步提高其能量效率(pJ/b)并扩展到更高的数据速率,调制器FoMeefficiency需要进一步降低,−3dB E/O BW需要提高到100 GHz。改进激光器的WPE对于大多数应用来说是必不可少的,但对于通信和计算应用来说尤其重要。还需要在每个波长中具有足够大功率的高效多波长光源。O/L/C频带中的低噪声、大增益带宽APD可以在没有显著功耗损失的情况下提供SNR改进,但从历史上看,它们的带宽、线性、噪声和功率处理特性阻碍了它们在最高带宽下的使用。最后,使用高增益、低噪声TIA放大PD信号仍然是一个关键的挑战。最近已经证明了几种基于均衡的技术可以使用低BW TIA来限制噪声,但大多数技术都只是在接收机时钟可用的假设下操作的。

为了使相干收发器在数据中心内部具有竞争力,必须解决额外的挑战(相对于IMDD)。TIA和驱动器的线性要求更加严格,需要尽可能减少对耗电DSP的依赖。研究人员正在探索的一种策略是利用集成光子和模拟电子威廉希尔官方网站 将一些信号处理任务转移到光学领域。后者需要大量的电子-光子协同设计工作,为CMOS设计者利用混合信号和RF IC的专业知识提供了机会。

实际的量子通信和计算应用需要具有先进CMOS控制器的LSI-VLSI光子组件。对于芯片级离散可变量子密钥分布(QKD),最重要的要求是超导纳米线单光子探测器(SPD)阵列的低温兼容光子/电子读出和控制;开发低损耗、低功率低温调制器和低温兼容WDM复用器/解复用器;以及在低噪声、低串扰的芯片级光子电子解决方案中集成发射器处的单光子源(SPS)阵列。超导纳米线SPD在电信波长下工作,有助于将现有光纤用作量子通道。除了大规模并行化之外,减少接收机中的损耗和提高SPD性能将有助于提高传输速率。对于量子计算应用,挑战是相似的,但需要更大的量子位控制/读出可扩展性,包括光子学和低延迟控制电子器件。当然,量子位的质量是至关重要的。控制/读取的可扩展性随着IL而降低——每损失一个光子都会以指数方式降低量子系统的能力。因此,需要超低损耗耦合器来连接到PIC。

光子计算涉及光子域中信息的模拟计算和处理。这需要处理多级信令并提高权重控制的精度,以保持足够高的SNR,从而与现有的CMOS EIC计算引擎相比保持精度。访问高速内存以防止非重量固定的激活和任务出现内存墙是另一个挑战。光子计算采用高并行性,因此需要减少无源和有源器件(调制器、移相器)的IL,并提高多波长激光器的输出功率,以增加网络规模。

对于汽车驾驶,硅光子激光雷达将自己定位为利用机械或基于MEMS的扫描的飞行时间(ToF)激光雷达的固态挑战者。激光雷达由两个子系统组成——测距和波束控制,这两个子系统都可以使用硅光子技术。ToF和调频连续波(FMCW)是测距技术。FMCW提供了以下优点:(1)相干检测低至几个光子的信号,(2)对来自环境源的干扰的鲁棒性,以及(3)同时进行距离和速度测量。相干检测的所有必要组件都可以集成在单个芯片上。对于波束控制,存在两种集成的可能性:(1)基于连续可调谐移相器和光栅的光学相位阵列。体光学解决方案,如旋转镜和振荡镜,具有廉价、成熟和简单的优点;用片上OPA取代这样的解决方案将是一个重大挑战。为了使OPA发射单个波束,光栅天线的间距需要小于半个波长(在自由空间中)——这对于硅芯片上的2D波束控制来说是一个具有挑战性的命题。因此,硅光子OPA通常具有布置用于1D中的光束转向的光栅,并且激光的波长被扫过以将光束转向另一个方向。(2) 基于片上开关网络和光栅耦合器的焦平面阵列。其中包括需要MEMS开关的2D FPA,或具有波长控制的1D FPA。无论解决方案如何,低功率(10s的nW)和改进的FoMeefficiency移相器对于波束控制来说都是重要的和必要的。改进激光是下一个挑战。对于1D运算放大器或FPA,多波长激光器可以放松波长调谐。对于FMCW解调,窄线宽(<100kHz)连续可调谐激光器(优选无模式跳变)至关重要。缩放和封装是第三个挑战。缩放许多发射器和移相器的光子学和电子器件,并为激光器和复杂的DSP集成相当大的延迟(图2,见补充),这两者都是必要的。

微波光子的应用(如滤波器和低相位噪声振荡器)与迄今为止讨论的大多数其他应用相比,具有不同的挑战。用于微波滤波的无杂散动态范围(SFDR)规范在当前一代硅光子中实现起来相当具有挑战性。调制器和PD需要严格的线性,同时,必须将几种噪声源(激光、PD、TIA)降至最低。获得RF净增益的目标使设计更加复杂。通过具有优于仅CMOS对应物的相位噪声的硅光子实现激光辅助微波振荡器还需要最小化激光噪声、PD和TIA噪声。还需要良好的短期和长期稳定性。

硅光子还可以用于低成本和紧凑设计的陀螺仪。但是,为了在性能上与基于光纤的同行竞争,利用Sagnac效应的硅光子中的陀螺仪必须证明波导中的超低损耗(模仿光纤)、在振动和温度变化的极端条件下由于反射而导致的偏置漂移的减少(以不掩盖Sagnac相移)以及高灵敏度的低噪声。SiN波导的工程化已经将损耗降低到0.5dB/m,还需要进一步改进。必须消除片上和片外的背反射,为此必须可靠地实现片上隔离器、反射消除威廉希尔官方网站 或自注入锁定。由于陀螺仪既不需要LSI实现,也不需要高速调制器,因此如果解决了上述挑战,它将会是一种很有前途的定制应用。它对振动的鲁棒性也要求异构实现,HVM必须解决其挑战。

用于生物传感应用的硅光子光谱仪通常需要与C/L/O波段不兼容的工作波长。这成为最重要的瓶颈,因为必须设计、测试和表征新的波导(相对于标准的220nm)和其他光子组件。激光器也是很具有挑战性的,并且在这些非标准波长下对宽波长调谐或多波长激光器的需求造成了严重的困难。最后,测量的稳定性和可复制性对于生物传感应用至关重要,尽管存在环境漂移,但必须保持PIC和激光器的性能。

倏逝场生物传感器的稳定性和可复制性要求甚至更严格,因为对血液或其他体液的侵入性测量增加了用户对信任的期望。检测的系统极限不仅取决于谐振器对温度、激光噪声、PD和TIA噪声的响应,还取决于流体流动、机械振动和生物噪声引起的噪声。在氧化物开放步骤之后,谐振器表面的功能化在很大程度上取决于波导设计和亲和力。生物传感器的封装和集成带来了下一组挑战。台式机使用昂贵的可调谐激光器和纳米定位器,但使用简单的无源PIC进行生物传感。另一方面,护理点设备必须紧凑、廉价,并且需要使用低成本可调谐激光器或与PIC、EIC和流体学的其余部分集成的固定波长激光器进行操作。

目前用于视网膜成像的以硅光子为扫描源的光学相干断层扫描(OCT)原型的灵敏度较差。首先,它们在O或C波段工作,而眼科OCT优选在1050 nm处,以更深地穿透组织。移动到1050nm将需要基于SiN的PIC和该波长的可调谐激光源。最大限度地减少内部反射并改善隔离将提高灵敏度。下一个障碍是激光源的调谐范围和扫描速率有限,降低了图像采集速率。最后,由于激光安全性的限制,激光功率不能太高。这反过来又需要PIC和成像光学器件之间几乎无损的连接。

5.总结与结论

我们在硅光子方面取得了巨大的飞跃——从几十年前才制造出第一个高限制波导和第一个调制器——到战略性地利用CMOS行业的材料、集成和封装技术成为收发器领域的主导技术。与此同时,硅光子在很大程度上仍然是一项正在开发中的技术,而一系列的可能性(本文仅描述了其中的一些)预示着未来的前景。未来十年将出现一些明显的赢家,整合也将发生。尽管如此,应用程序的多样性将确保该技术有足够的机会扩大规模并广泛传播。

我们相信,在下一个十年,我们将看到以下可能实现的里程碑:

混合、异构和单片集成将为大规模集成威廉希尔官方网站 甚至超大规模集成威廉希尔官方网站 实现提供具有必要密度、可配置性和可编程性的激光器、移相器、调制器和电子器件。这些集成技术中的每一种都有其优点,并且在可预见的未来都可能共存。

集成激光器和硅光子SOA将迅速发展。大多数晶圆厂将提供集成激光器,WPE超过20%。将支持多波长激光器和可调谐激光器。

硅光子最终将从可插拔收发器转向其他成功的商业产品,广泛应用于CPO和xPU应用。使用插入器和小芯片架构构建的复杂系统将采用光子技术进行互连。相干光子将进一步发展——例如用于内部通信(甚至数据中心内部)、传感(FMCW激光雷达、生物传感)和计算。

基于等离子体色散的调制器将继续充分用于许多WDM通信应用,但与此同时,Pockels调制器和移相器将在SOI CMOS工艺中商业化。LNOI将被引入硅光子工艺中,用于需要非常高速调制和低Vπ的应用,尽管它们的尺寸较长。

同样,高效热光加热器不会在一夜之间推出。但是,对理想的低功耗移相器的追求将带来一个真正能够实现LSI/VLSI应用的解决方案。许多技术正在竞争,明显的赢家尚未出现。

商用晶圆厂通常支持多层SiN和Si,并将针对这些SiN层优化高性能无源元件(滤波器、延迟线)。

我们预计逆向设计的趋势将开始产生更紧凑、更高性能和更坚固的波导块,这些波导块将成为PDK不可或缺的一部分。同样的技术也将提高超材料和超表面的性能。

光纤到PIC耦合的IL、带宽和片上面积将不断改善,典型的IL将会降至<0.5 dB。

我们还期待硅光子能够拥有更完整的生态。将光子威廉希尔官方网站 设计流程与EDA环境集成(或集成到EDA环境中)已经开始,随着威廉希尔官方网站 变得更加复杂,光子和电子的协同设计将变得更加关键。光子威廉希尔官方网站 的规模化和与电子学的融合也将带来光子威廉希尔官方网站 更大的可配置性和可编程性,降低构建利用光物理用于新应用的新系统的门槛。

太空时代催生了CMOS产业,互联网时代催生了光子产业,而数据时代将为这两者提供燃料。

责任编辑:彭菁

-

下一代定位与导航系统2012-08-18 0

-

2016CES:Atmel下一代触摸传感技术亮相2016-01-13 0

-

易飞扬:新世界没有硅光子不可能成功2016-11-24 0

-

新世界没有硅光子不可能成功2016-12-21 0

-

硅光子技术2017-11-02 0

-

下一代SONET SDH设备2019-09-05 0

-

请问电容滤波威廉希尔官方网站 经过电容滤波之后会是什么样子?2019-09-17 0

-

单片光学实现下一代设计2019-09-20 0

-

请问Ultrascale FPGA中单片和下一代堆叠硅互连技术是什么意思?2020-04-27 0

-

下一代超快I-V测试系统关键的技术挑战有哪些?2021-04-15 0

-

下一代网联汽车将会是什么样的呢?2019-04-17 3617

-

下一代显示技术将会是什么2020-07-06 3475

-

下一代人工智能基础设施的产品和服务是什么样的2022-09-23 845

-

发光的乐器在黑暗中会是什么样子2022-11-14 360

-

下一代硅光子技术会是什么样子?2023-07-05 656

全部0条评论

快来发表一下你的评论吧 !