概述安森美M 1 1200 V SiC MOSFET的关键特性及驱动条件

模拟技术

描述

SiC MOSFET 在功率半导体市场中正迅速普及,因为它最初的一些可靠性问题已得到解决,并且价位已达到非常有吸引力的水平。随着市场上的器件越来越多,必须了解 SiC MOSFET 与 IGBT 之间的共性和差异,以便用户充分利用每种器件。本系列文章将概述安森美 M 1 1200 V SiC MOSFET 的关键特性及驱动条件对它的影响,作为安森美提供的全方位宽禁带生态系统的一部分,还将提供 NCP51705(用于 SiC MOSFET 的隔离栅极驱动器)的使用指南。本文为第二部分,将重点介绍安森美M 1 1200 V SiC MOSFET的 动态特性 。

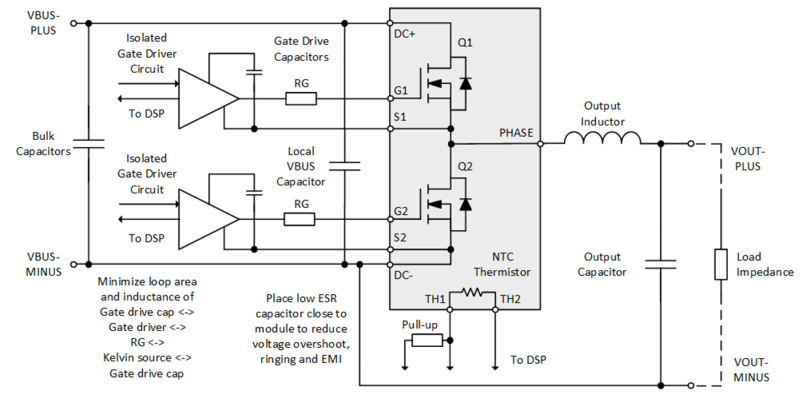

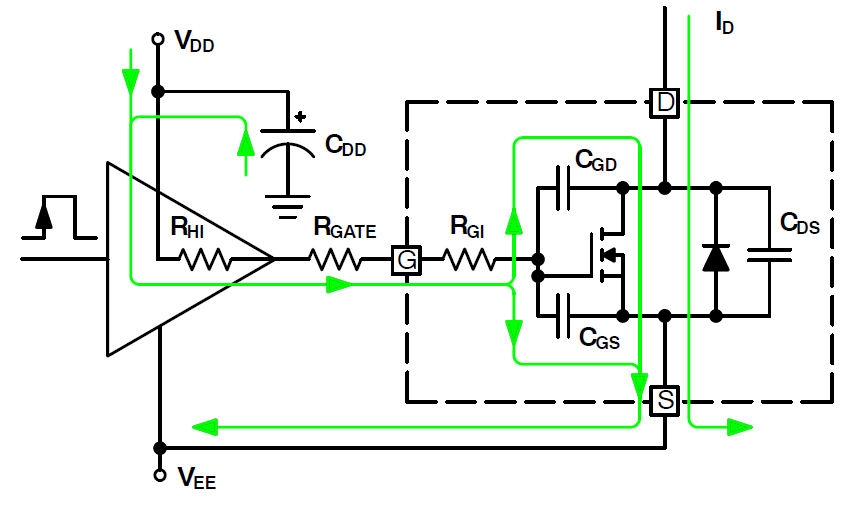

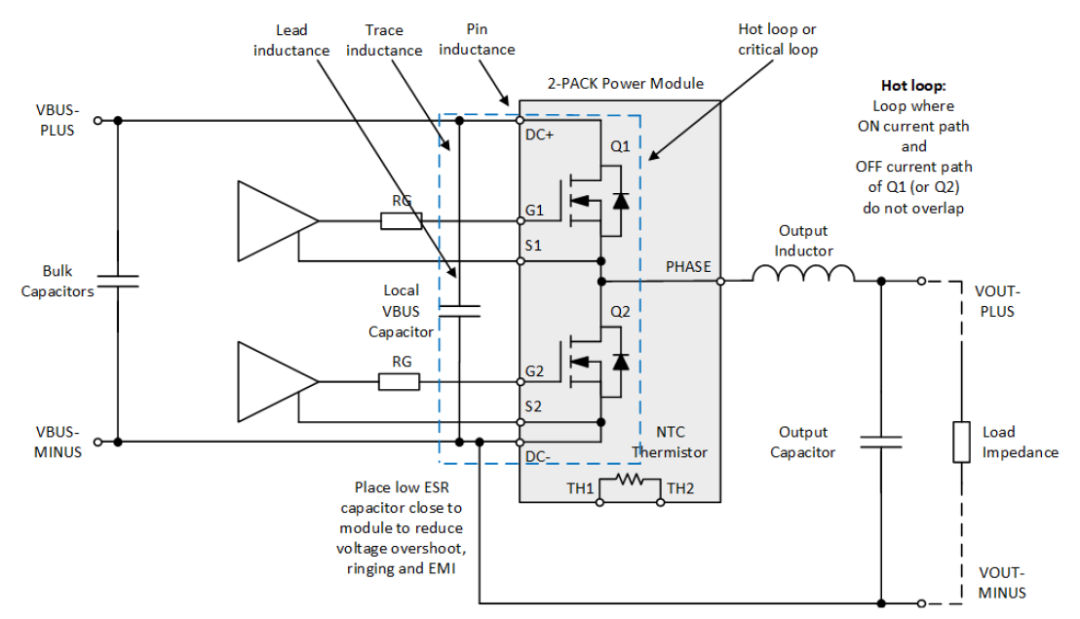

为了表征安森美 M 1 SiC MOSFET 的动态特性,使用了一个 20 m 的半桥模块,其中两个 40 m 器件并联。图 10 说明了测试设置。

图 10:动态特性测试设置框图

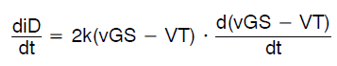

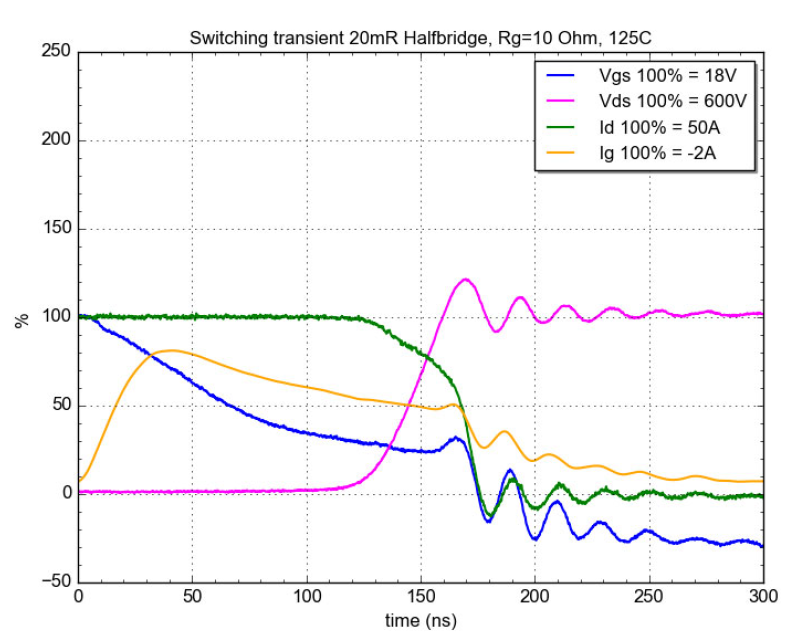

图 11 显示了上述测试设备的导通波形。品红色曲线是低压侧 MOSFET 的漏电压。绿色曲线是通过低压侧 MOSFET 的电流。

如果栅极驱动器在时间 t = 0 时被切换到 18 V,则切换序列开始。在初始缓升之后,栅极驱动电流起步很高,并随着栅极电压的增加而减小。栅极电压升高,直至达到阈值电压。电流增加,直至达到流过二极管的电流:负载电流+反向恢复电流+电容电流。

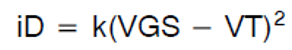

SiC MOSFET 的台阶电压高度依赖于负载电流。在图 11 中,台阶电压约为 10 V。给定 ID 的 VGS 由以下公式得出。

因此,坡度将随时间变化如下:

当栅极电压随时间呈近似线性变化时,di/dt 随时间呈线性变化。由di/dt 随时间呈线性下降引起的 Vds 压降从电流达到阈值电压时开始,到达到电流峰值时结束。

栅极电流和电压达到台阶电压。栅极电流为 QGD 充电,并且漏电压降低到几乎为零。

漏极电流向负载电流下降,并伴有一些振铃。

最后,栅极电压升高至 18 V。漏电压降低至负载电流乘以 18 V 时的 R DS(ON) 。

图 11:20 mohm、1200 V 半桥模块的导通波形

图 12:SiC MOSFET 源极电流

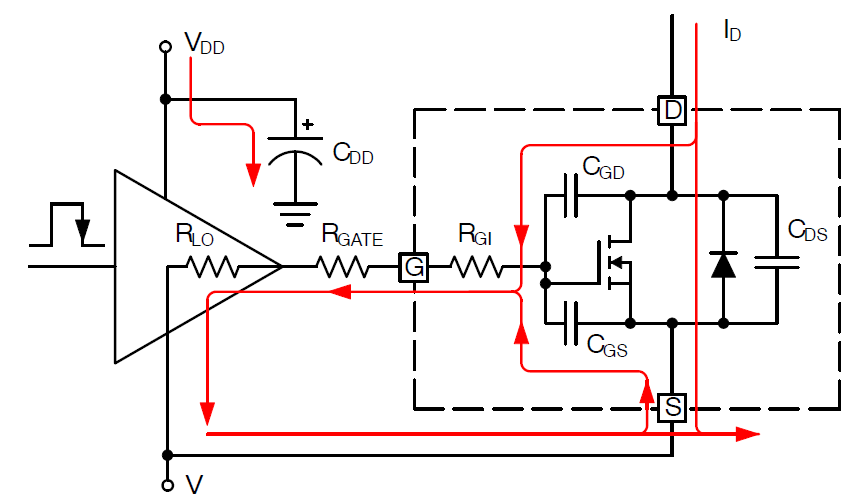

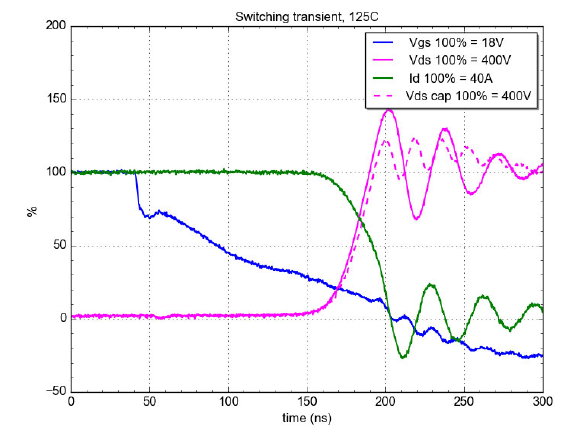

图 13 显示了使用两个 40 mohm 器件的 20 mohm、1200 V 半桥模块的关断波形。

如果栅极驱动器在时间 t = 0 时被切换到 -5 V,则开关序列开始。在初始缓升之后,栅极驱动漏极电流起步很高,并随着栅极电压的增加而减小。栅极电压下降,直至达到台阶电压。由于没有反向恢复电流,台阶电压低于导通期间的电压。QGD 放电时,电压升高。一些漏极电流用于给非线性 COSS 电容放电,其在漏极电流中表现为负斜率。

栅极电压过冲由威廉希尔官方网站 中的回路电感引起:离直流总线最近的电容–模块的直流+触点–模块的直流−触点–回到直流总线电容。模块和电容之间的连接应尽可能低电感,以最大限度地降低振铃电压。

当达到峰值电压时,栅极驱动器将栅极从台阶电压放电至阈值电压,使电流降至零。栅极驱动器继续给栅极放电,直至达到 −5 V。

图 13:20 mohm、1200 V 半桥模块的关断波形

图 14:SiC MOSFET 漏极电流

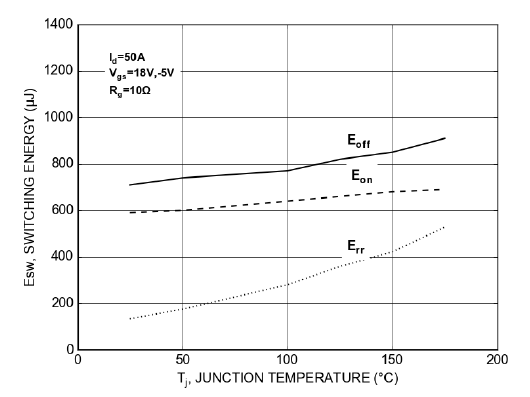

开关损耗随温度增加

与静态特性一样,SiC MOSFET 的工作温度将对开关性能产生影响。不过,如图 15 所示,EON 和 EOFF 的温度系数几乎相同,150℃ 时的开关性能将非常接近 25℃ 时的特性。反向恢复损耗 (E rr ) 却非如此,其在 25℃ 时可忽略不计,但随着温度升高,它们可能会达到损耗计算应考虑的程度。因此,如前一章所述,考虑实际工作温度下的参数至关重要,而不仅仅是 25℃。

在 Err 的情况下,值得注意的是,这些损耗的很大一部分是电容损耗,而不是 pn 结损耗。这些电容损耗看起来像示波器上的损耗,但不会导致体二极管发热。这些损耗的影响和幅度取决于电压和电流,但可能高达典型数据表中所示 Err损耗的 40%。因此,直接从数据表中获取 Err 损耗是一种保守的方法。然后,在实际应用中,只能通过比较系统输入功率和系统输出功率来测量总损耗。

图 15:20 mΩ、1200 V SiC MOSFET 模块中的开关损耗与 Tj

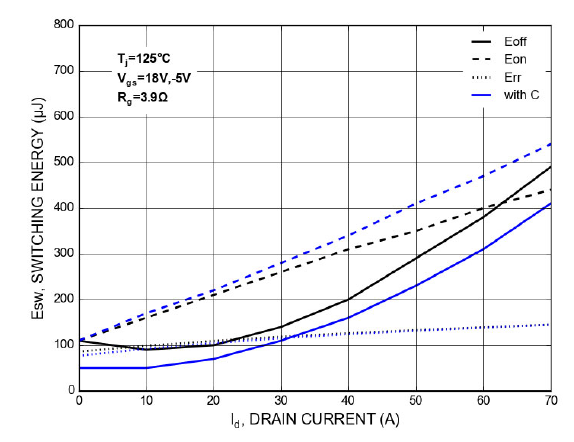

开关损耗随漏极电流 (I D ) 而增加

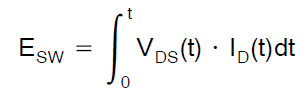

根据定义,MOSFET 的开关损耗是指任何开关事件期间电压时间积分与电流的乘积。

因此,预计损耗会随着电流的增加而增加。但在将 M 1 1200 V SiC MOSFET 的行为与 IGBT 相比时,存在一些差异。如图 16 所示,对于半桥配置的 20 mΩ、1200 V SiC 模块,EON 与 ID 的关系是线性的,这些损耗将取决于换向回路中相应二极管的恢复。体二极管的恢复损耗也表现为线性模式。另一方面,EOFF 损耗从二次增长开始,直到它们也变成线性的某一点。

图 16:20 mΩ、1200 V SiC MOSFET 模块中的开关损耗与 ID 特性

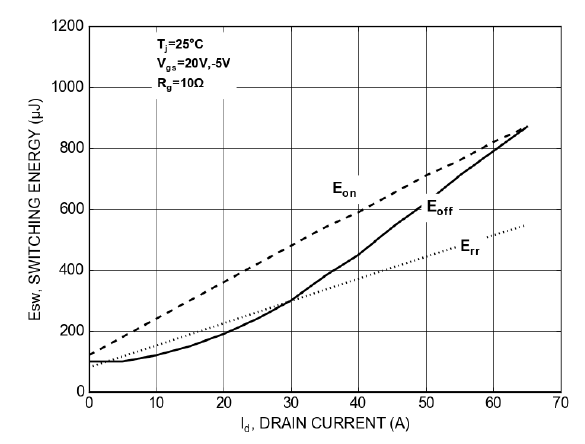

开关损耗与漏源电压 (V DS )

如前一点所述,开关损耗的另一个直接因素是 V DS ,在这种情况下,如图 17 所示,E ON 、EOFF 和 Err 以线性方式表现,但斜率不同。

图 17:20 mΩ、1200 V SiC MOSFET 模块中的开关损耗与 VD

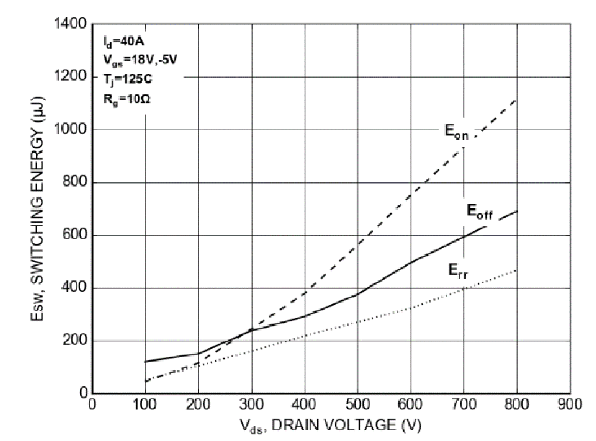

栅极电阻 (R G ) 对开关性能的影响

开关器件通过外部手段实现的可控性是威廉希尔官方网站 设计中的关键因素。在 MOSFET 或 IGBT 的情况下,尽管是电压控制器件,但影响其开关行为的最常见方式之一是修改外部栅极电阻 R G ,其中包括调节开关事件中涉及的不同电容的充电或放电速度。因此,会直接影响开关时间以及 di/dt 或 dv/dt。

在第一阶段,选择适当的值时,需要考虑 RG 对损耗的影响。RG 较高将使器件速度变慢,从而导致 EON 和 EOFF 损耗增加。图 18 显示了 20 mΩ、1200 V SiC MOSFET M 1 模块中开关损耗与 RG 的关系。RG 较高的积极影响是 Err 损耗减少,这是因为 MOSFET 体二极管在较慢的开关速度下表现更平滑。

但是,这不能补偿导通和关断损耗的增加。

图 18:20 mΩ、1200 V SiC MOSFET 模块中的开关损耗与 RG

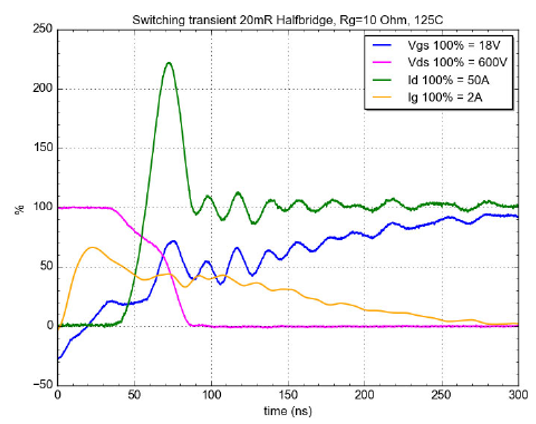

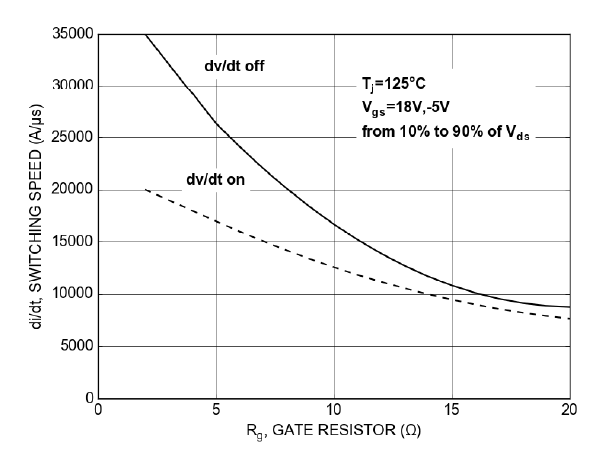

结论显而易见,应尽可能降低 R G 。另一方面,任何威廉希尔官方网站 的寄生电感和电容都可能导致临界电压过冲或振荡,如果器件太快打开,会产生潜在的电磁干扰 (EMI),这不仅涉及主电流换向路径,还涉及栅极威廉希尔官方网站 。此外,在某些应用中,出于安全原因,dV/dt 可能受到限制。因此,器件的速度必须能够通过 RG 或最终的栅极电容 (C G ) 轻松调节,但不建议使用后者,因为它可能会在栅极中造成严重的振荡。图 19 显示了在使用安森美 M 1 SiC MOSFET 的 1200 V、20 mΩ 半桥模块中 RG 对 dV/dt 的影响。此图显示,RG 的修改使用户能够对 dV/dt 产生强大的影响,从而使开关行为适应威廉希尔官方网站 和应用的要求。通过这种方式,每个用户都能轻松为自己的应用找到开关损耗和开关速度之间的最佳平衡。

图 19. 20 mΩ、1200 V SiC MOSFET 模块中 RG 的 dV/dt 可控性

VGS 对开关损耗的影响

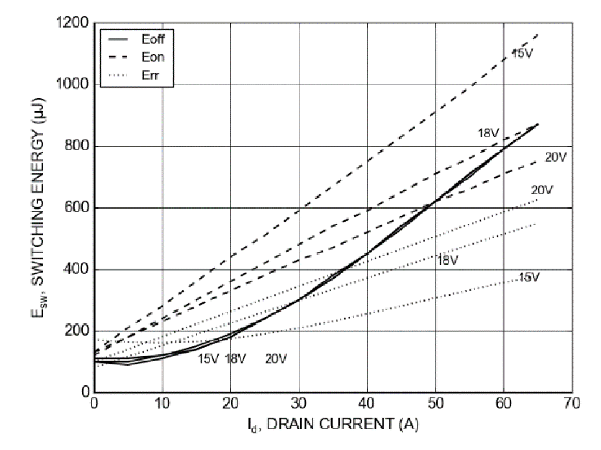

在本应用笔记的第一章中,讨论了 VGS 对安森美 M 1 1200 V SiC MOSFET 静态特性的影响。结论是,至少在 + 18 V 的电压下使用该器件,高达 + 20 V 的电压更佳。如果现在正在考虑开关性能,则结论将是相同的。图 20 显示了开关损耗与 VGS 的相关性。EOFF 与正 VGS 无关:在图中,三条 EOFF 曲线重叠。另一方面,VGS 将对 EON 和 Err 行为产生重大影响。如果 VGS 增加并且使用相同的 R G ,则电流给 CGD 和 CGS充电。结果导致器件开关变快,从而减少 EON 损耗,这对 Err 的影响正好相反,因为速度加快将在相反 MOSFET 的体二极管中引起更高的恢复损耗。

图 20:20 mΩ、1200 V SiC MOSFET 模块中正 VGS 对开关损耗的影响

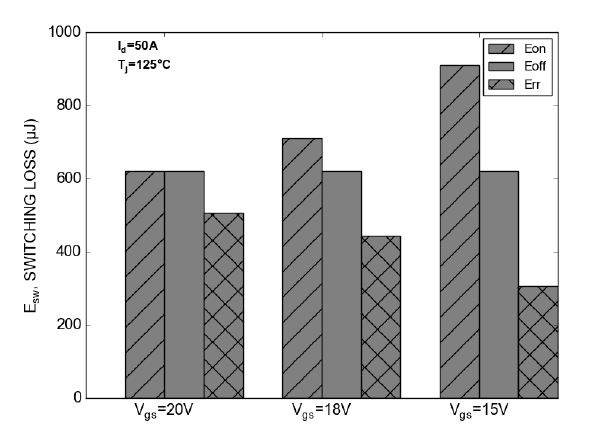

如果考虑总损耗,如图 21 所示,在 VGS 较高时,EON 损耗的减少会过度补偿 Err 的增加,能够更有效地在较高 VGS 下开关器件。当然,还应考虑其他因素,如 EMI 或 dV/dt。

图 21:20 mΩ、1200 V SiC MOSFET 模块中不同正 VGS 的总损耗

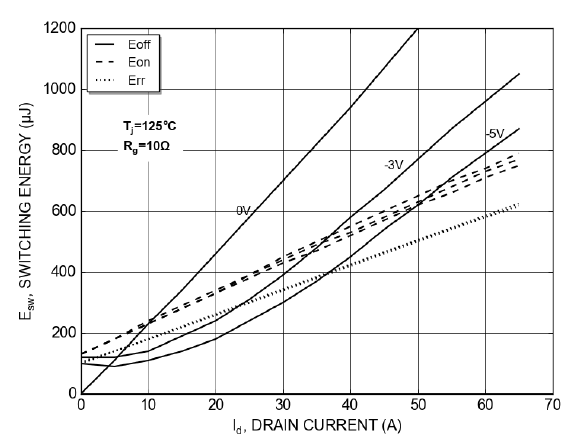

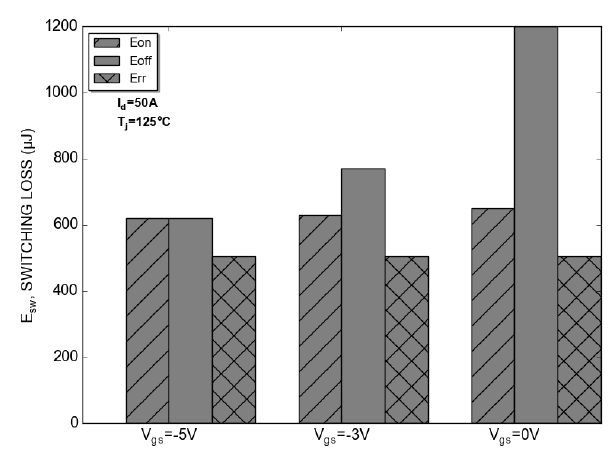

考虑到负栅极偏压,之前强调了在体二极管应导通期间使用负电压完全关闭沟道的重要性。这也会对开关损耗产生影响。如图 22 所示,虽然负栅极电压对 EON 或 Err 损耗几乎没有影响,但 EOFF 损耗可能会受到严重影响。尽管 – 5 V 和 −3 V 之间的差异约为 25%,但如果使用 0 V 负栅极偏压,则 EOFF 损耗可能会翻倍。

图 22:20 mΩ、1200 V SiC MOSFET 模块中负 VGS 对开关损耗的影响

在图 23 中也可以观察到这种影响,其中显示了总损耗。

图 23:20 mΩ、1200 V SiC MOSFET 模块中不同 VGS 的总损耗

图 23:20 mΩ、1200 V SiC MOSFET 模块中不同 VGS 的总损耗

短路耐受时间 (SCWT)

在一些应用中,SCWT 是挑选器件时需要考虑的一个重要要求。不过,此特性也会带来一些影响。SCWT 较长会对静态和动态性能产生影响。因此,在许多器件中,为了获得更好的性能,会忽略此特性。

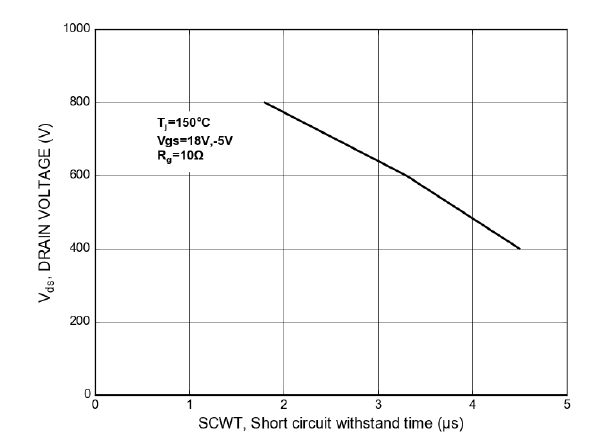

安森美 1200 V M 1 SiC MOSFET 留有一定的设计裕度,以提供短路耐受能力。器件能够在短路中存活的时间取决于许多因素,最重要的因素是 VDS 和设备可能遭受短路事件的参考温度。与本应用笔记中讨论的许多其他参数一样,必须在合适的温度下看待这些特性,虽然 125℃ 和 150℃ 之间的差异不大,但 SiC MOSFET 的 SCWT 在 25℃ 时可能会明显更好。为了提供常见工作温度的相关数据,本文选择了 150℃ 的起始温度。图 24 显示了不同 VDS 的典型 SCWT。

重要提示:这些是典型的参考值,无法保证一定会实现,请参考数据表中的值或联系您当地的技术支持人员。

图 24:20 mΩ、1200 V 半桥 SiC MOSFET 模块中的短路耐受时间

图 25 显示了 20 mΩ、1200 V SiC MOSFET 模块在 150℃ 时的实际测量短路行为。

图 25:20 mΩ、1200 V 半桥 SiC MOSFET 模块中的短路行为

体二极管的动态特性

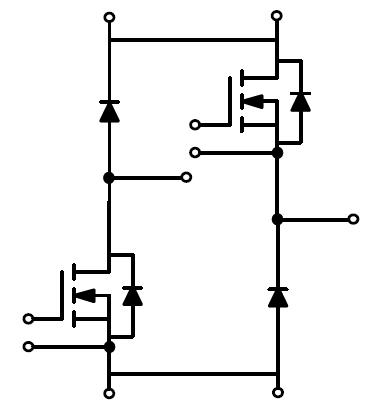

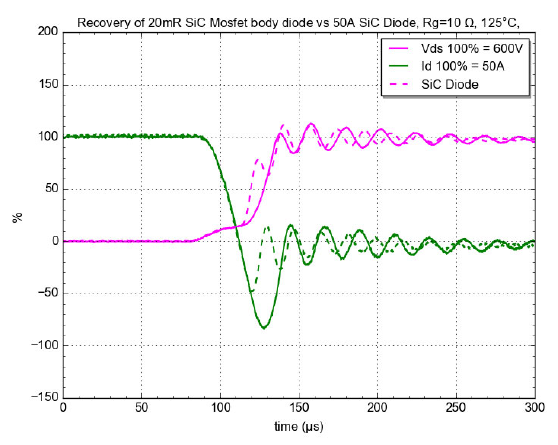

如前几章所述,即使不建议使用传导损耗较高的 SiC MOSFET 体二极管,这也不能总是避免。改善总损耗的一种可能性是激活 MOSFET 的沟道以改善静态行为,但这对动态性能的影响微乎其微。另一种方法是采用与 SiC MOSFET 并联的外部 SiC 二极管。不过,为了完全禁用体二极管,应将其与半桥的主换向路径去耦,如图 26 所示。

图 26:具有拆分输出的半桥

这种拆分不仅引入了额外的 SiC 二极管,而且增加了布局的复杂性。比较外部 SiC 二极管与体二极管的动态行为,如图 27 所示,可以看出外部 SiC 二极管确实改善了反向恢复行为。但这种改善可能微不足道;特别是考虑到部分体二极管损耗无耗散。因此,用户需要考虑在成本和复杂性都相应增加的情况下添加此附加组件是否值得。

图 27:外部 SiC 二极管(虚线)与 SiC MOSFET 体二极管(实线)的恢复行为

在电源模块内添加缓冲电容的影响

任何设计中的杂散电感都将在器件的开关性能中发挥关键作用,不仅在效率方面,而且还会导致不必要的行为,例如振铃或高压过冲。考虑到 SiC 器件主要用于快速开关应用,杂散电感产生不必要影响的风险变得更高。因此,在任何设计中,都要首先保持寄生电感尽可能低。尽管如此,即使是最有经验的设计人员也无法避免封装固有的某些寄生和所需的最少 PCB 布线。

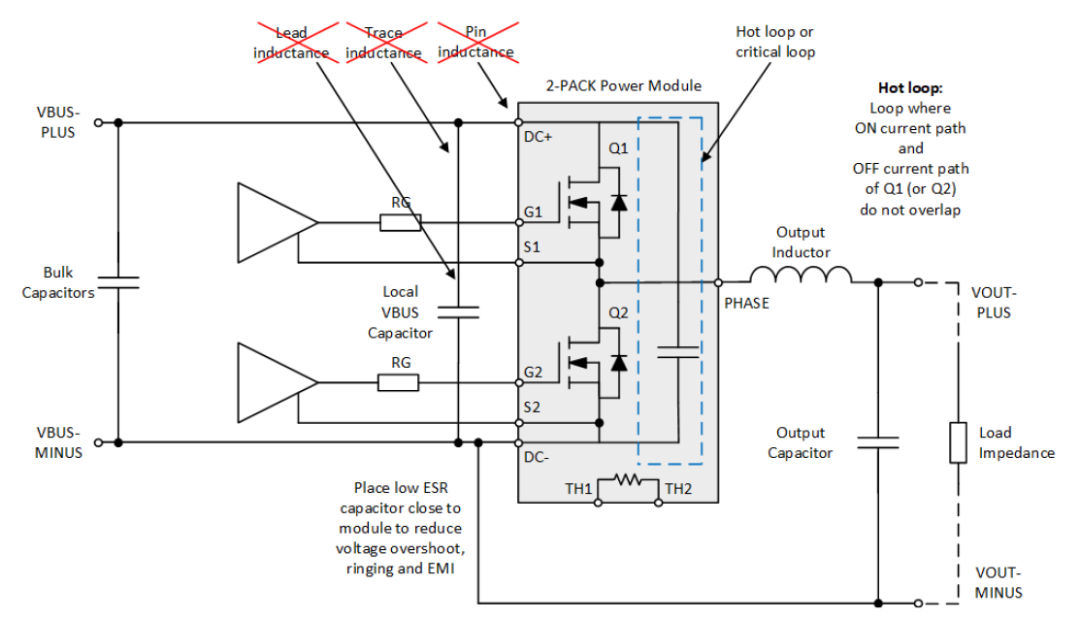

图 28 显示了标准半桥配置关键开关回路中主要组件的示意图。为了缩短临界回路的长度,应尽可能靠近模块放置低 ESR 电容。但是,这不会阻止回路中包含引脚电感、PCB 迹线和电容引线。

图 28:具有外部电容的半桥模块示意图

为了进一步缩短临界回路的长度,可以在模块内部集成一个额外的电容。如图 29 所示。这样,通过在一定程度上消除引脚、迹线和引线电感的影响,我们可以进一步减小寄生电感。集成电容的尺寸受到模块内部可用空间的限制,例如,本研究使用了 100 nF 电容。

图 29:具有集成电容的半桥模块示意图

减小临界回路电感将能改善开关行为。首先,如图 30 所示,关断时的电压过冲可从近 150% 降至 120%。

图 30:具有集成电容与外部电容的半桥关断行为

如图 31 所示,电压过冲减少的直接后果是 Eoff 损耗减少。另一方面,随着电流的增加,Eon 损耗可能会增加。在任何情况下,从总损耗来看,器件的公共电流能力都有所提高。

图 31:具有和没有集成电容的开关损耗

审核编辑:刘清

-

安森美半导体智能功率模块(IPM)及易于采用的工具和仿真支持2018-10-30 0

-

SiC-MOSFET体二极管特性2018-11-27 0

-

安森美半导体大力用于汽车功能电子化方案的扩展汽车认证的器件2018-10-25 0

-

SiC-MOSFET与Si-MOSFET的区别2018-11-30 0

-

安森美LED驱动方案2019-02-08 425

-

Ameya360:安森美推出1700V EliteSiC MOSFET,提供高功率工业应用2023-01-04 652

-

安森美推出最新一代1200 V EliteSiC 碳化硅(SiC)M3S器件2023-05-25 456

-

安森美 M 1 1200 V SiC MOSFET 静态特性分析2023-06-08 514

-

安森美 M 1 1200 V SiC MOSFET 动态特性分析2023-06-16 715

-

安森美M1 1200 V SiC MOSFET动态特性分析2023-06-16 989

-

用于 SiC MOSFET 的隔离栅极驱动器使用指南2023-06-25 829

-

一周新品推荐:ODU MEDI-SNAP连接器和安森美1200V M3S系列SiC MOSFET2023-09-06 549

-

安森美发布了第二代1200V碳化硅 (SiC) MOSFET—M3S2024-03-26 1641

-

安森美1200V碳化硅MOSFET M3S系列设计注意事项和使用技巧2024-03-28 1373

-

沟槽当道,平面型SiC MOSFET尚能饭否?2024-04-08 3984

全部0条评论

快来发表一下你的评论吧 !