芯教程|平头哥助力昊芯HX2000系列芯片专题SCI串口通讯奇偶校验(二)SCI增强FIFO

描述

自昊芯推出专题讲解SCI串口通讯奇偶校验,分为两期讲解,上期主要讲解标准SCI模式下的奇偶校验,本期主要讲解增强FIFO模式下的奇偶校验。

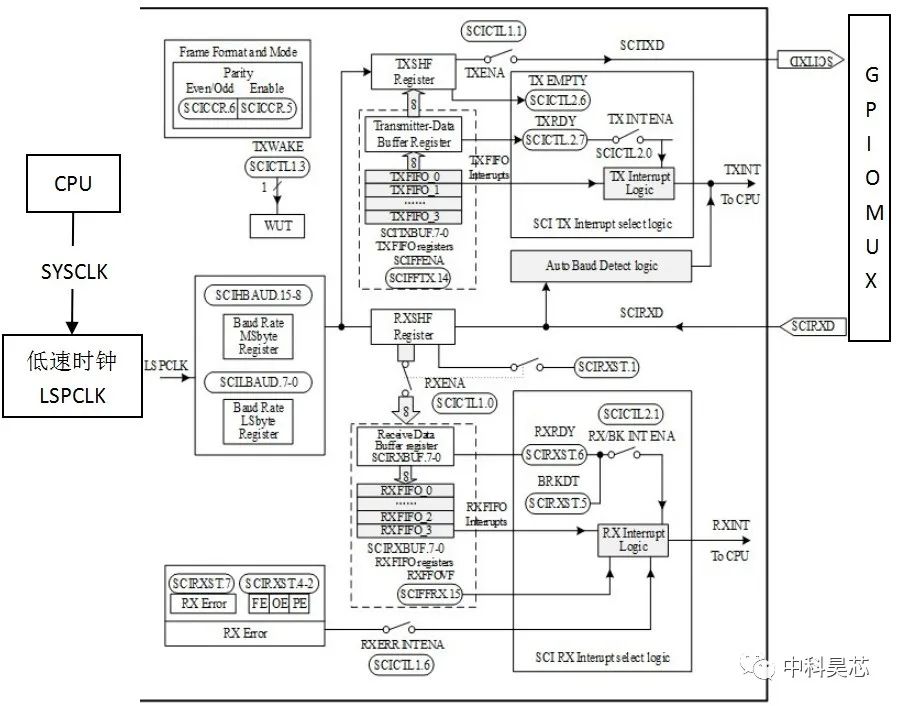

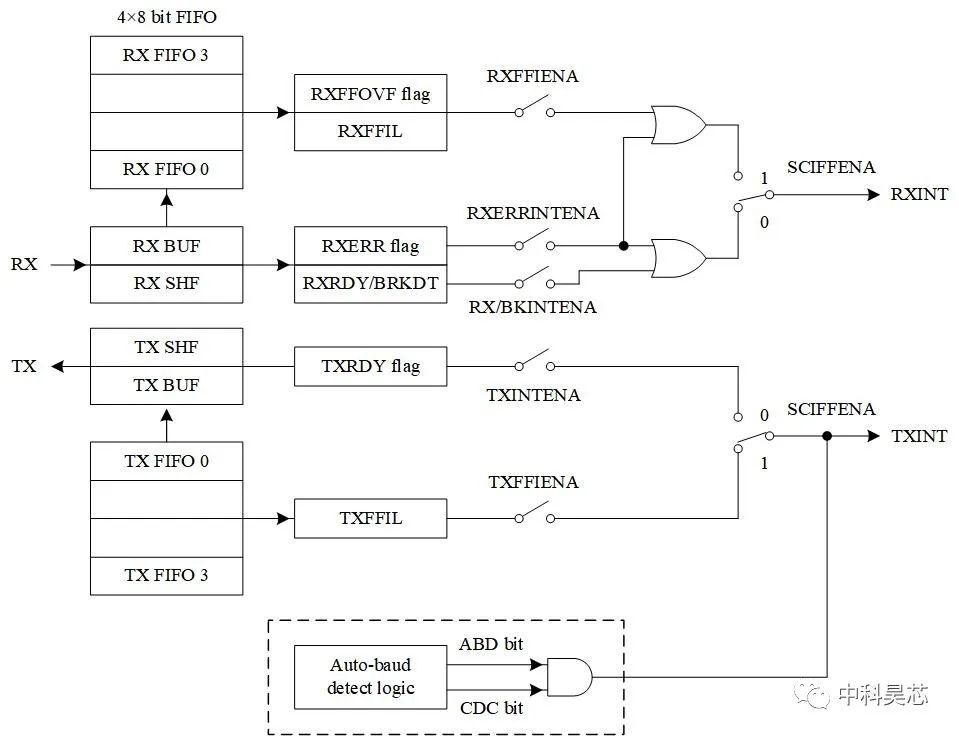

HX2000系列SCI模块与中断框图如下,可通过SCICCR[PARITYENA]使能,启动奇偶校验;采用SCICCR[PARITY]选择,使用奇或偶校验,对每个字符增加一个额外的校验位,以校验收发数据的二进制码中“1”的个数,校验收发数据的一致性;FIFO模式下校验原理与标准模式一致,但收发数据校验位不一致时,仅置位SCIRXBUF[SCIFFPE]输出错误信号。

由此设计SCI串口增强FIFO通信校验实例:采用SCI与串口CH340,通过串口调试助手,向CPU发送任意一组四字节数据,CPU接收所发送的数据,通过按键控制,选择奇或偶校验,校验收发数据的一致性,硬件连接如下图所示:

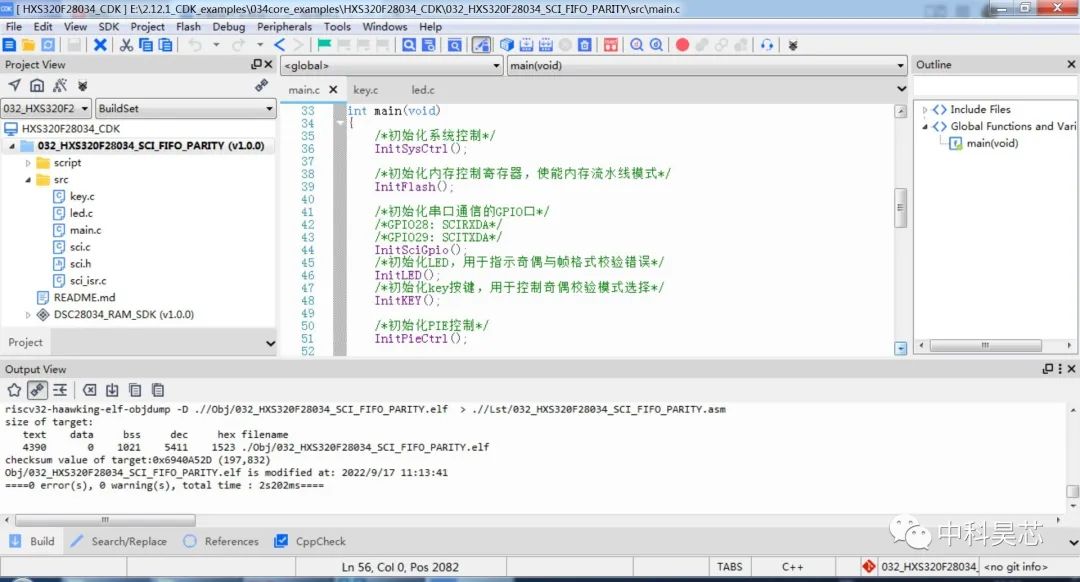

基于以上分析,在CDK上开发SCI串口增强FIFO通信校验,代码包括:SCI GPIO外设引脚配置,SCI增强FIFO功能与校验配置程序,发送、接收与校验程序,主程序调用执行。主要代码如下:

1.int main(void)2.{3. /*初始化系统控制*/4. InitSysCtrl();5. /*初始化内存控制寄存器,使能内存流水线模式*/6. InitFlash();7. /*初始化串口通信的GPIO口:GPIO28: SCIRXDA,GPIO29: SCITXDA*/8. InitSciGpio();9.10. /*初始化LED,用于指示奇偶与帧格式校验错误*/11. InitLED();12. /*初始化key按键,用于控制奇偶校验模式选择*/13. InitKEY();14.15. /*关闭PIE中断*/16. InitPieCtrl();17. /*清除中断标志位*/18. IER = 0x0000;19. IFR = 0x0000;20. /*初始化PIE中断向量表*/21. InitPieVectTable();22.23. EALLOW;24. /*中断向量表入口地址SCIRXINTA,指向执行接收中断、校验模式选择与程序*/25. PieVectTable.SCIRXINTA=&sci_rx_isr;26. EDIS;27.28. /*打开相应的PIE中断线*/29. IER |= M_INT9;30. /*PIE Group 9, SCIRXINTA*/31. PieCtrlRegs.PIEIER9.bit.INTx1=1;32.33. /*SCI增强FIFO配置:含奇偶校验*/34. Scia_Config(9600);35. /*打开全局中断*/36. EINT;37. for (;;)38. {39. }40. return 0;41.}

CDK上开发SCI串口增强FIFO通信校验程序,编译结果为:

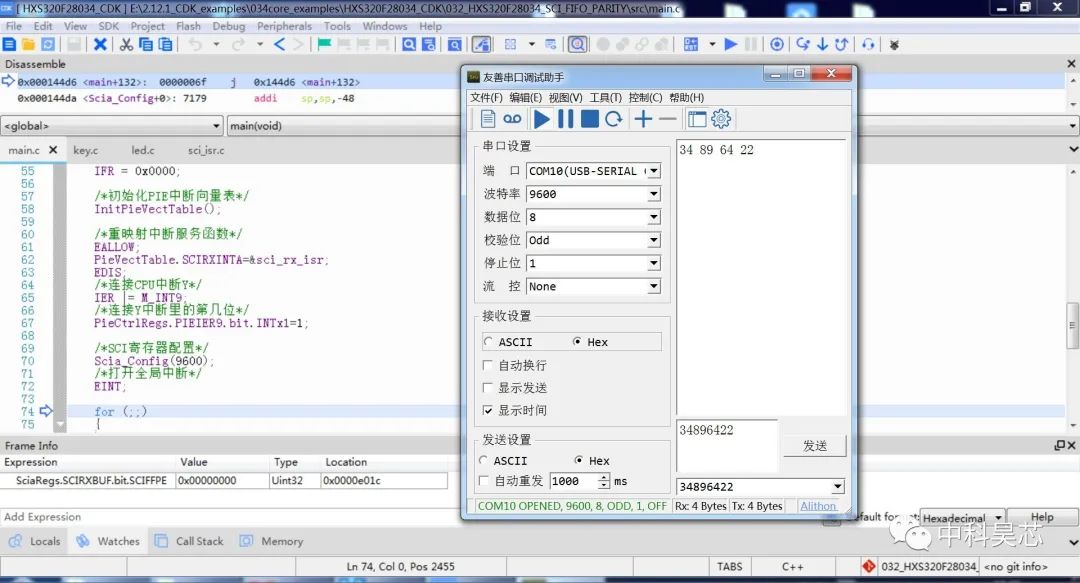

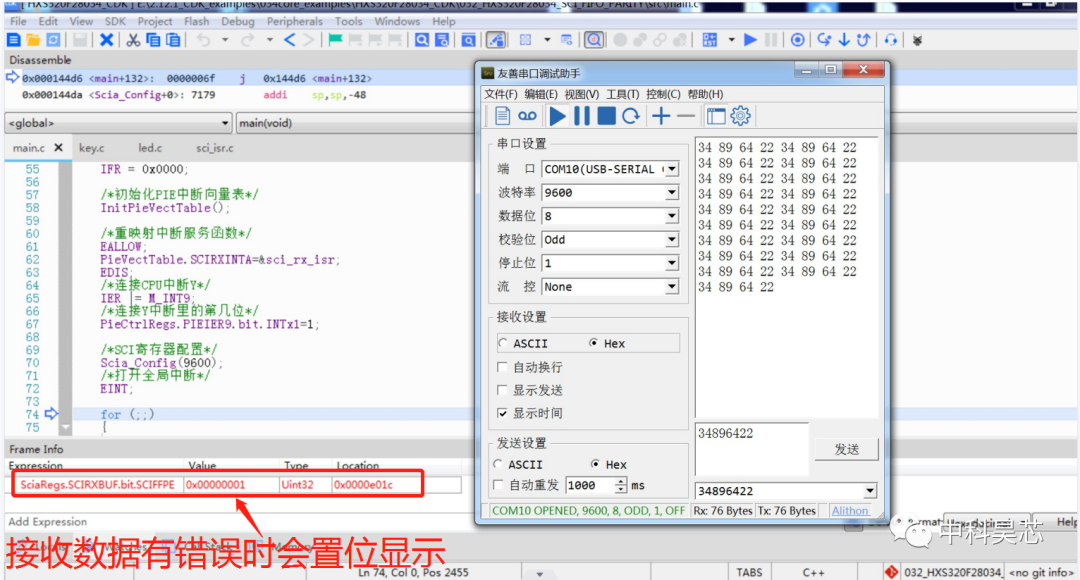

编译通过后,就可开始调试了,调试后,可通过串口调试助手查看发送与接收到的数据:

收发数据校验位不一致时,通过SciaRegs.SCIRXBUF.SCIFFPE置位输出错误信号:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

平头哥剑池CDK助力中科昊芯HX2000系列芯片系统开发与调试2022-03-09 0

-

【中科昊芯Start_DSC28027勇士开发板试用体验】SCI(UART)通讯2022-06-20 0

-

SCI串口自动波特率介绍2022-04-26 3249

-

标准SCI模式下的奇偶校验2022-10-13 1696

-

增强FIFO模式下的奇偶校验2022-11-02 1048

-

昊芯HX2000系列芯片助力电机安全在线调试保护2023-02-12 992

-

芯教程丨平头哥助力中科昊芯HX2000系列芯片之SCI串口通信专题(一)FIFO通信2022-04-24 1162

-

芯教程丨平头哥助力中科昊芯HX2000系列芯片专题SCI串口通信(二)AutoBaud自动波特率2022-04-27 846

-

芯教程丨平头哥助力中科昊芯HX2000系列芯片专题SCI串口通信(三)FIFO中断通信2022-05-26 958

-

平头哥CDK助力中科昊芯HX2000系列芯片之双电机有感FOC控制系统专题(四)永磁电机双闭环FOC控制2022-03-10 1075

-

芯教程|平头哥助力昊芯HX2000系列芯片电机过流跳闸保护专题(二)EPWM_DC数字比较2022-06-10 1137

-

芯教程|平头哥助力昊芯HX2000系列芯片电机过流跳闸保护专题(三)比较器超阈值检测2022-06-17 759

-

芯教程丨平头哥助力昊芯HX2000系列芯片QEP电机测速2022-07-01 996

-

芯教程|平头哥助力昊芯HX2000系列芯片专题SCI串口通讯奇偶校验(一)标准SCI2022-10-14 784

-

芯教程丨昊芯HX2000系列芯片助力电机安全在线调试保护2023-02-13 1536

全部0条评论

快来发表一下你的评论吧 !