FPGA布局及资源优化

可编程逻辑

描述

1.项目需求

FPGA :V7-690T两片

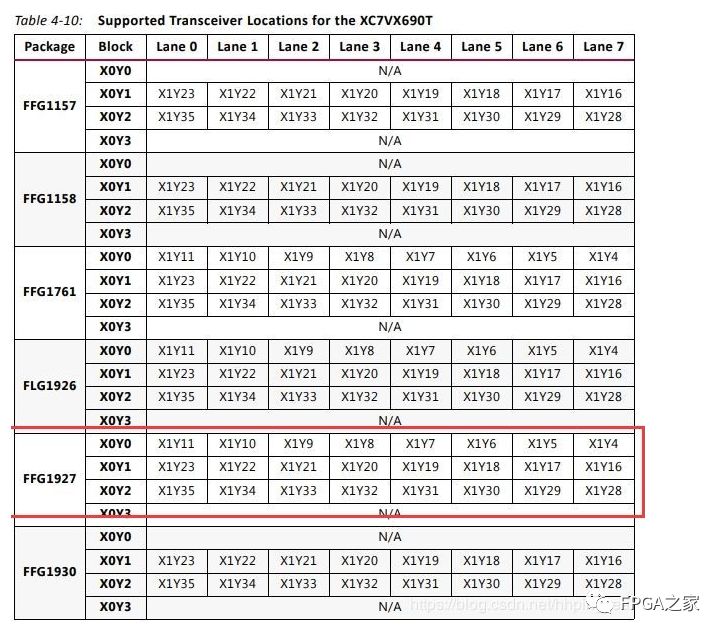

Resource:两片FPGA通过X12 gth互联;每片FPGA使用48路serdes走光口与板外连接;每片FPGA使用SIROx4通过VPX与外界互联;每片FPGA使用PCIE X8与板上CPU Intel XEON互联;每片FPGA使用20对LVDS互联;CPLD控制FPGA上电时序/CPU启动/FPGA加载;每片FPGA挂载2路4GB DDR3。

2.FPGA架构设计问题

我们知道,FPGA片上分布着各种资源,如时钟,serdes,RAM,LUT,IO等。在进行FPGA规划时候,应当需要知道项目设计需求,以及需求各模块之间的数据交织情况,这样可以避免后续FPGA RTL设计出现时序很难优化的情况。

对应这个情况,举一个简单的例子。如果一个FPGA工程中含有一个PCIE和一个DDR接口,并且,需要用到PCIE与外部设备进行大量数据块上传和下载方面的传输。那么DDR作为PCIE的一个缓存接口,最优的方案是在FPGA内部对PCIE接口和DDR接口尽量靠近放置。这样FPGA RTL设计的时候时序很容易达到最优。在V7-690T FPGA中,可以将PCIE放置的最优位置如下图。

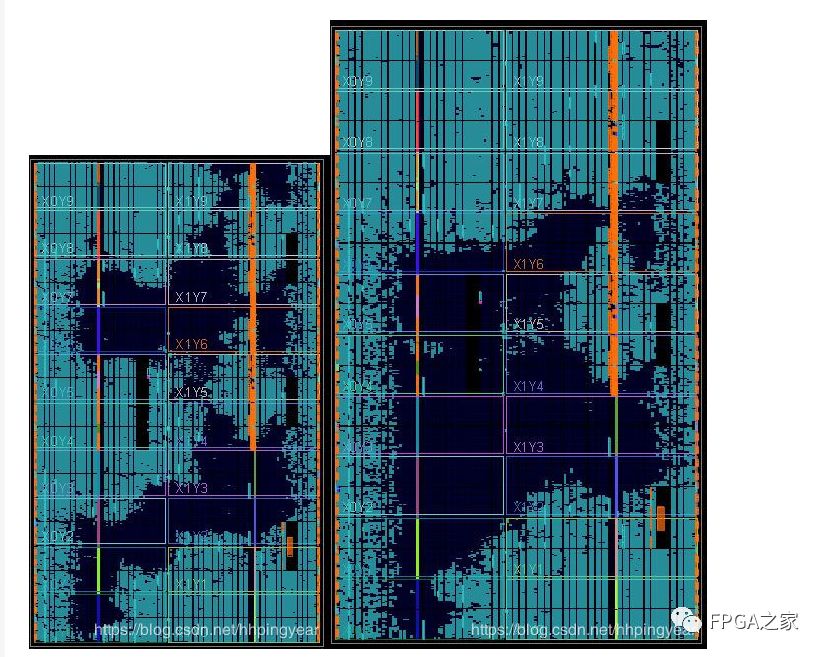

同时,我们也知道,在V7-690 FPGA中,DDR通常可以放置的位置可以是BANK34/35/36和BANK36/37/38。这时综合上述两个条件,我们可以得到最优放置PCIE和DDR的位置。使得FPGA内部编译通过率或者说时序最好。

下面是两种不同放置方式得到的example design编译结果图。

3.前期碰到的问题

1).时钟优化

在管脚验证的时候,本人将各个功能模块都用XILINX FPGA的IP生成 example design并集成到一个工程下面,但是发现上面提出的功能集成下来FPGA的BUFG资源远远不够。下图是FPGA example design各模块BUFG资源需求情况。因此做了一些资源优化。

a.前期验证中,发现SRIO是消耗BUFG资源最多的IP,因此能省出最多的BUFG。

b.DDR也消耗比较多时钟,这个项目一个FPGA用到两个DDR控制器,也能省出比较多BUFG。

2).PCIE不是在所有serdes下都能放的,对V7-690,需要放置在特殊的SERDES处,这样,实际PCIE 程序编译时候,这个特殊的serdes里PCIE 特殊资源离得最近,编译出来的时序报告是最好的。如若不然,需要设置PCIE IP内部特殊参数,才能使得PCIE DEV被CPU看到,也就是PCIE link上。

3).DDR布局也要参考数据是如何在FPGA内部交织的,劲量靠近会用到大数据流量的模块放置,这样后期设计时序会好很多。

4)FPGA功耗估计问题。

这个可以在XILINX官网下载一个XPE Excel表格,很实用的,用一两次就熟悉了。但是本人认为这个工具对很多人也有个缺点,就是实际并不知道以后自己的代码各种资源消耗有多少。所以可能评估不太准。

本人是用example design工程查看编译报告得出。当涉及到调整温度啊电流啊啥的时候,在vivado下需要打开implementation的结果后才可以改动电流/温度的值进行评估的。

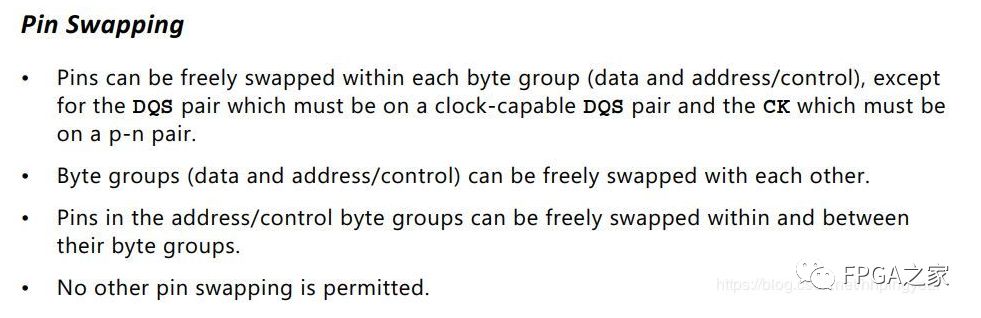

3.FPGA PCB布线时会遇到调整线序的问题。

1)这要根据项目需求看调整后的布局是否满足项目需求,调整好后一定要原理图工程师给出最新的原理图,最后FPGA根据新布局重新验证管脚等。千万不要口口相传丢失了信息。

2)DDR换线序可以参照XILINX的MIG手册,仔细核对的。

3) DDR PCB布线所需的管脚延时信息,可以通过新建一个空白工程,在空白工程的tcl下输入如下命令:

link_design -part xc7k160tfbg676

write_csv flight_time

4.CPLD调试

1)CPLD控制FPGA上电顺序,XILINX又一个check list,各位可以根据check list表格对硬件板卡进行关键信号测量确认,对上电时序进行控制等。

2)对FPGA的配置控制也可以月底 xilinx ug470等。

审核编辑:刘清

-

FPGA资源与AISC对应关系2024-02-22 0

-

优化 FPGA HLS 设计2024-08-16 0

-

FPGA面积优化经验分享2014-12-04 0

-

FPGA资源优化方法2015-04-04 0

-

FPGA-PCB优化技术降低制造成本2018-09-20 0

-

如何正确使用FPGA的时钟资源2017-01-18 744

-

FPGA并行时序驱动布局算法2018-02-26 872

-

浅析如何评估FPGA的资源2019-02-15 3913

-

如何评估FPGA的资源2020-12-28 840

-

FPGA的RAM存储资源详细资料说明2020-12-09 2735

-

FPGA布局及资源优化2021-01-07 5176

-

FPGA的BRAM资源使用优化策略2023-08-30 2869

-

fpga布局布线算法加速2023-12-20 859

-

FPGA布局布线优化技术2024-03-29 384

-

如何优化FPGA设计的性能2024-10-25 314

全部0条评论

快来发表一下你的评论吧 !