while(1)到底占了多少CPU功耗呢?这些功耗去哪里了呢?

电子说

描述

CPU耗能的基本原理

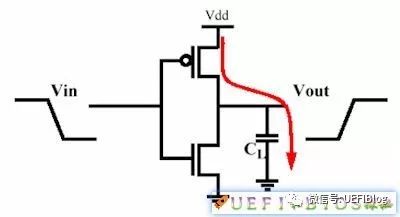

我们将CPU简单看作场效应晶体管FET的集合。这么多个FET随着每一次的翻转都在消耗者能量。一个FET的简单示意图如下:

图1

当输入低电平时,CL被充电,我们假设a焦耳的电能被储存在电容中。而当输入变成高电平后,这些电能则被释放,a焦耳的能量被释放了出来。因为CL很小,这个a也十分的小,几乎可以忽略不计。但如果我们以1GHz频率翻转这个FET,则能量消耗就是a × 10^9,这就不能忽略了,再加上CPU中有几十亿个FET,消耗的能量变得相当可观。

从这里我们可以看出CPU的能耗和有多少个晶体管参与工作有关,似乎还和频率是正相关的。我们下面分别来看一下。

指令功耗

如果我们将CPU简单看作单核的,是不是运行while(1);就能让该CPU达到TDP呢?实际上并不会。每条指令所要调动的晶体管数目不同,而功耗是被调动晶体管功耗的总和。

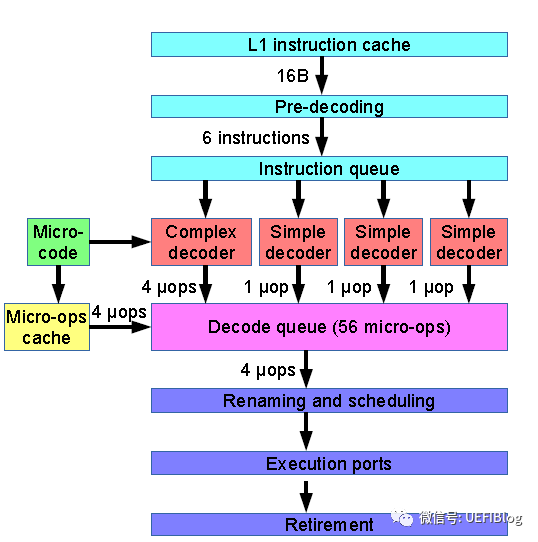

《动物庄园》有一句话很经典:“所有动物生来平等 但有些动物比其他动物更平等”。是不是指令都是平等的呢?当然不是了,有些指令更平等!每条指令需要调动的晶体管数目有很大不同,一条新指令和已经在L1指令Cache中的指令也不同。一个简化版Hesswell CPU的流水线示意图如下:

一个指令要不要调度运算器,要不要访问外存,要不要回写,在不在L1中都会带来不少的区别。综合下来,流水线中各个阶段的功耗饼图如下:

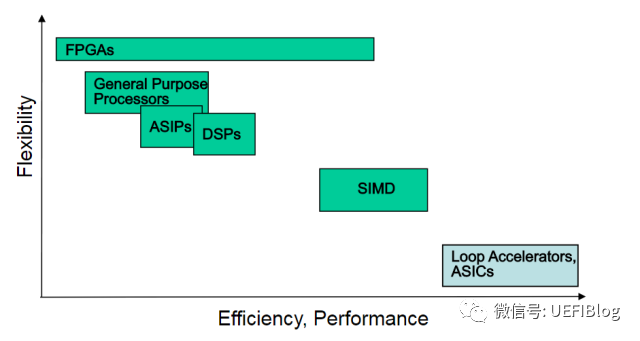

可以看到Fetch指令和decode占据了大头,而我们的执行才占据%9!!while(1);编译完的指令们,这时已经在L1中,Fetch会节省不少能耗。这也是达成同样功能,ASIC很省电,而CPU很费电的原因:

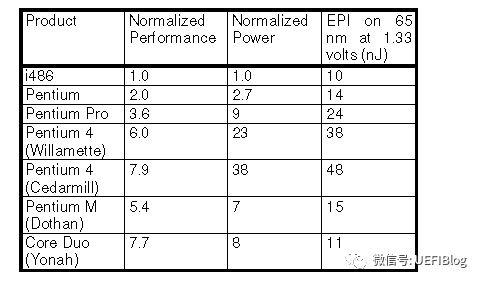

如果我们不讨论指令的差异,在平均意义上来看指令的功耗,它有个专有的名词:指令功耗(EPI,Energy per Instruction)。

EPI和CPU制程、设计息息相关。Intel的CPU在P4的EPI达到一个高峰,后来在注重每瓦功耗的情况下,逐年在下降:

Intel CPU EPI(数据较老)

耗能和频率的关系

从图1中,也许你可以直观的看出,能耗和频率是正相关的。这个理解很正确,实际上能耗和频率成线性相关。能耗关系公示是(参考资料2):

P代表能耗。C可以简单看作一个常数,它由制程和设计等因素决定;V代表电压;而f就是频率了。理想情况,提高一倍频率,则能耗提高一倍。看起来并不十分严重,不是吗?但实际情况却没有这么简单。

我们这里要引入门延迟(Gate Delay)的概念。简单来说,组成CPU的FET充放电需要一定时间,这个时间就是门延迟。只有在充放电完成后采样才能保证信号的完整性。而这个充放电时间和电压负相关,即电压高,则充放电时间就短。也和制程正相关,即制程越小,充放电时间就短。让我们去除制程的干扰因素,当我们不断提高频率f后,过了某个节点,太快的翻转会造成门延迟跟不上,从而影响数字信号的完整性,从而造成错误。这也是为什么超频到某个阶段会不稳定,随机出错的原因。那么怎么办呢?聪明的你也许想到了超频中常用的办法:加压。对了,可以通过提高电压来减小门延迟,让系统重新稳定下来。

让我们回头再来看看公式,你会发现电压和功耗可不是线性相关,而是平方的关系!再乘以f,情况就更加糟糕了。我们提高频率,同时不得不提高电压,造成P的大幅提高!我们回忆一下初中学过的y=x^3的函数图:

Y在经过前期缓慢的提高后在a点会开始陡峭的上升。这个a就是转折点,过了它,就划不来了。功耗和频率的关系也大抵如此,我们看两个实际的例子:

i7-2600K频率和功耗的关系

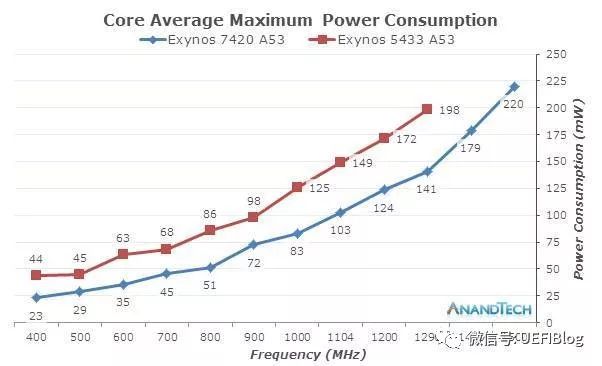

Exynos频率和功耗的关系

从ARM和X86阵营来看,他们能耗曲线是不是和幂函数图很像?

其他因素

一个while(1);最多让某个内核占有率100%,其他内核呢?CPU近期的目标是提供越来越精细的电源管理策略。原来不跑的部分就让它闲着,后来改成它降频运行,接着改成不提供时钟信号,这样犹嫌不足。现在CPU的电源管理由PMC负责,它会完全切断不用部分的威廉希尔官方网站 。

在操作系统层面,它会尽力将不用的内核设置成CState,从而让PMC等电源控制模块有足够的提示(hint)来关闭电源。

结论

拉拉杂杂的说了这许多,我们可以看出,while(1);并不会耗掉整个CPU的TDP。就算一个内核,它的耗能也不会达到该内核的能耗上线(现在都是Turbo Mode,内核能耗上限是个动态的结果)。它可以把该内核拉入Turbo Mode的最高频率,但因为指令都在L1中,耗能也不会很高。

至于消耗的能量都到哪里去了,根据能量守恒定律,一定是变成热量散发出去了。这个过程中也许会产生动能(风扇转动等等),光能(GPIO驱动LED发光),但在最后的最后,都会变成热能。

-

什么是低功耗设计呢?2023-05-15 1257

-

使用这些设计技巧降低FPGA功耗2012-01-11 0

-

关于降低功耗在编程时的建议2014-03-27 0

-

【精选】STM32功耗测试笔记2021-03-03 0

-

请问动态功耗怎么仿真呢?2021-06-24 0

-

到底该怎么去使用KEIL的这些调试方法呢2021-12-21 0

-

如何对STOP的休眠功耗模式进行调试呢2022-02-21 0

-

请问TICKLESS是如何去实现功耗降低的呢2022-02-24 0

-

DAC功耗数据计算 功耗数字到底包括什么?2012-11-30 4354

-

小米MIUI8.2你到底好在哪里?到底值不值得升级呢?2017-02-18 29753

-

从微架构设计和制造工艺低功耗CPU的实现2018-02-01 7296

-

如何知道真正的CPU功耗 功率墙问题怎么解决2020-08-26 41256

-

CPU内部到底是如何工作的呢?2021-04-04 5681

-

在Linux系统中系统变量存在哪里呢?2022-11-16 1930

-

CPU的低功耗与高功耗的区别2024-08-07 4155

全部0条评论

快来发表一下你的评论吧 !