FPGA的详细开发流程

描述

引言

FPGA 的详细开发流程就是利用 EDA 开发工具对 FPGA 芯片进行开发的过程,所以 FPGA 芯片开发流程讲的并不是芯片的制造流程,区分于 IC 设计制造流程哟(芯片制造流程多麻烦,要好几十亿的费用呢,而且国内也貌似没有哪家像样的 Foundry 厂,除了台湾的 TSMC 在世界有立足之地,Fabless 的 IC 设计公司倒是挺强的如 Hisilicon,这也是它为什么会被 USA 针对的原因)。

例如,基于标准单元与基于 FPGA 的 APR 自动布局布线的区别在于:FPGA 内部的逻辑单元以及走线资源都是固定的,布局布线工具只是完成如何使用这些资源以使得整个设计收敛;而基于标准单元的 APR 的标准单元位置以及走线资源都是自己设计调整的,所以灵活性更大,更加容易使得整个设计收敛。

如下所示,主要包括威廉希尔官方网站 设计、设计输入、综合(优化)、布局布线(实现与优化)、编程配置五大步骤,其中,还有功能仿真、静态仿真、时序仿真三大仿真,以及综合约束、布局布线约束(包括位置约束和时序约束)两大约束等等。

FPGA 的详细开发流程

一、威廉希尔官方网站 设计(FPGA Design)

Before FPGA Design:在威廉希尔官方网站 设计之前,首先要进行的是算法的设计与验证、方案论证、架构设计和 FPGA 芯片选型等等准备工作;算法工程师可以在 Python 或 Matlab 设计中完成,而至于算法是怎么来的,通常是根据市场需求来开发的,这个就不在本次讨论之中了。系统工程师根据任务要求,如系统的指标和复杂度、成本、功能性和稳定性、性能、对工作速度(延时和工作频率)和芯片本身的各种资源、功耗等等方面进行权衡(红色加粗部分也是数字电子系统的五大设计目标),选择合理的设计方案(浮点定点、设计优化)和合适的 FPGA 器件类型(如 Cylone、Spartan、Artix、Virtex、Kintex、还是 Zynq 或者是 Zynq UltraScale + 等等)。

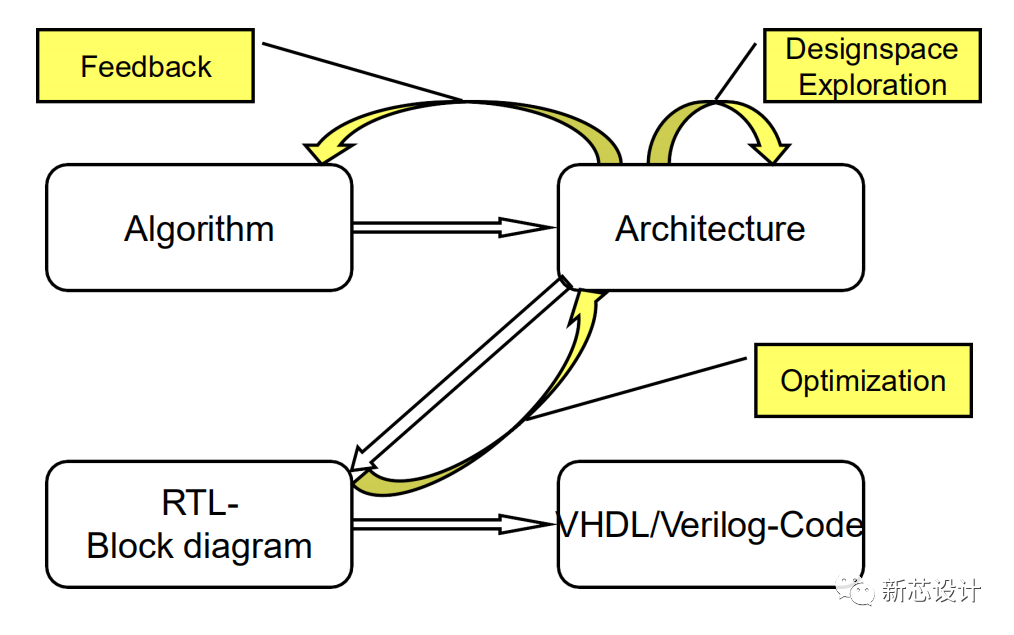

FPGA Design:威廉希尔官方网站 设计方法分为自底向上和自顶向下的设计方法;通常都采用自顶向下的设计方法:从系统设计开始,逐渐向子系统设计、模块设计、器件设计、版图设计等等更加物理的层次推进,直到可以直接使用 EDA 元件库为止,能够先勾勒出来威廉希尔官方网站 了,才开始 Coding(记住,Coding Style 也很重要哟)。

威廉希尔官方网站 设计流程

二、设计输入(Design Entry)

设计输入指的是将设计者所涉及的威廉希尔官方网站 以开发软件要求的某种形式表达出来,并输入到相应的软件中的过程。最常见的设计输入的表达方式为 IP 核、原理图(Schematic)和 HDL 文本输入。

这里的 IP 按照来源的不同可以分为三类,第一种是来自前一个设计创建的模块(Design by Yourself),第二种是 FPGA 厂家,第三种就是来自 IP 厂商。而按照产品交付的形式,IP 核又分为软核(HDL 或 Netlist 形式的功能块,如 MicroBlaze 软核)、硬核(版图形式,提供设计的最终阶段产品,即掩膜,如 Zedboard 的 ARM Cortex-A9)、固核(Netlist 形式,完成了综合与布局布线的功能块,只能基于特定芯片的 IP 核)。

FPGA 厂家和 IP 厂商可以在 FPGA 开发的不同时期提供给我们不同的 IP,我们暂且知道他们分别是未加密的 RTL 级 IP、加密的 RTL 级 IP、未经布局布线的网表级 IP、布局布线后的网表级 IP。

三、综合(Synthesis)

无论是什么样的设计输入,最终都要通过综合,生成统一的网表形式,从而与 FPGA 硬件资源互相匹配。例如,FPGA 是基于 LUT 结构的,那么就综合出一个基于 LUT 的门级网表文件(不同于 IC 的综合)。

IC 综合指的是将高级抽象层次的设计描述自动转化为较低层次描述的过程,或者说,综合器就是能够将 Schematic 或者 HDL 文本语言描述的威廉希尔官方网站 ,编译成由与或阵列、RAM、触发器、寄存器等逻辑单元组成的威廉希尔官方网站 结构的门级网表文件的工具,即 RTL - to - Netlist。

综合包括编译、映射和优化,编译就是 HDL → 门级网表,映射就是门级网表 → LUT,优化就是优化设计。

在 Altera 的开发流程中,编译和映射的过程叫做综合,而在 Xilinx 的开发流程中,由设计输入得到门级网表的过程叫做综合。

综合的形式如下所示:

- 将算法、行为描述转换到 RTL 级(Register Transfer Level)(寄存器传输级),即从行为描述到结构描述。

- 将 RTL 级描述转换到逻辑门级(包括触发器),称为逻辑综合。

- 将逻辑门表示转换到版图表示,或者 PLD 器件的配置网表表示;根据版图信息能够进行 ASIC 生产,有了配置网表可完成基于 PLD 器件的系统实现。

数字系统设计器件如下所示:

- 数字系统器件的实现从以前的 PLA(可编程逻辑阵列)、PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)发展到如今的 PLD(可编程逻辑器件 Programmable Logic Device)(包括现场可编程门阵列 FPGA(Field Programmable Gate Array)和复杂可编程逻辑器件 CPLD(Complex Programmable Logic Device))(半定制)、ASIC(专用集成威廉希尔官方网站 Application Specific Integrated Circuits)(全定制)。

- 软件程序编译器是将 C 或汇编语言等编写的程序编译为 0 1 代码流,而硬件综合器是将 Verilog HDL 等语言编写的程序转化为具体的威廉希尔官方网站 门级网表。

- 在威廉希尔官方网站 设计中,网表(Netlist)是用于描述威廉希尔官方网站 元件相互之间连接关系的,一般来说是一个遵循某种比较简单的标记语法的文本文件(百度百科 门级网表);综合就是逻辑综合器根据约束条件把 Verilog HDL 或 VHDL 描述的 RTL 级设计,转换为可与 FPGA/CPLD 的门阵列基本结构相映射的网表文件。

四、布局布线(Place & Route)

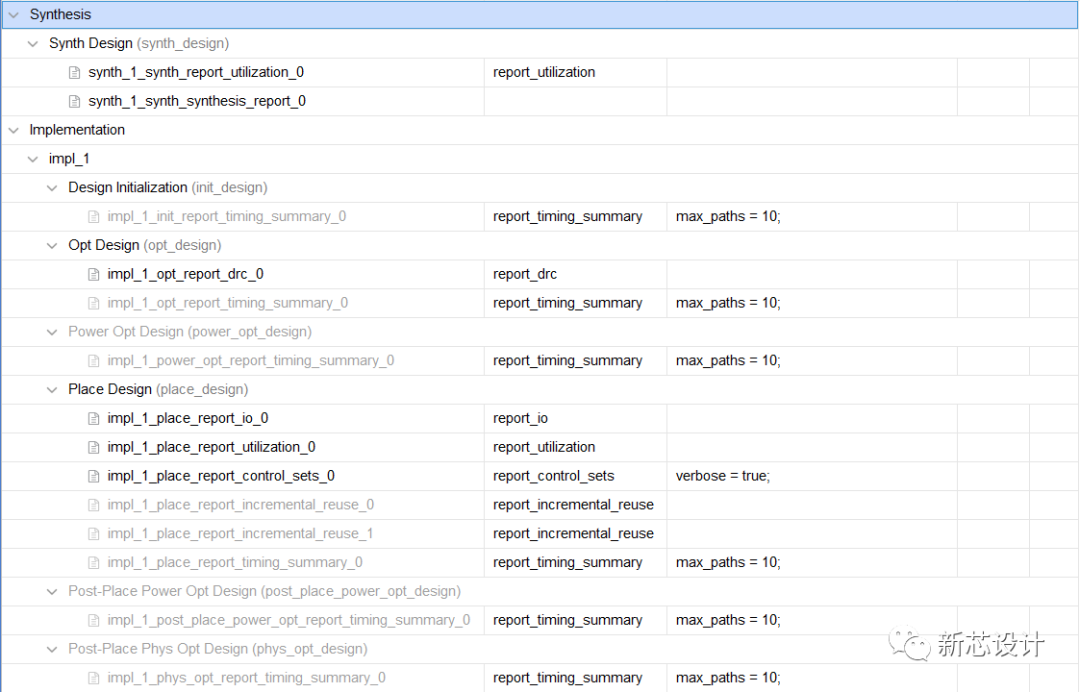

谈及布局布线之前,首先要谈到实现(Implementation)。实现就是将综合生成的门级网表配置到具体的 FPGA 芯片上,而布局布线就是其中最重要的过程。Vivado 中的实现具体如下所示,分为设计初始化(Design Initialization)、优化设计(Opt Design)、功耗优化设计(Power Opt Design)、布局设计(Place Design)、后布局功耗优化设计(Post-Place Power Opt Design)、后布局物理优化设计(Post-Place Phys Opt Design)、布线设计(Route Design)、后布线物理优化设计(Post-Route Phys Opt Design)、生成比特流(Write Bitstream)。

布局布线流程

布局布线指的是将综合生成的威廉希尔官方网站 门级网表映射到具体的目标器件中实现,并产生最终的可下载文件的过程。

- 布局是将已分割的逻辑小块放到器件内部逻辑资源的具体位置,并使它们易于连线;

- 布线则是利用器件的布线资源完成各功能模块之间和反馈信号之间的连接。

布局布线完成之后将产生如下一些重要的文件:

- 芯片资源耗用情况报告;

- 面向其他 EDA 工具的输出文件,如 EDIF 文件等;

- 产生延时网表结构,以便于进行精确的时序仿真,这时候的仿真结果能够比较精确地预测未来芯片的实际性能。如果仿真结果达不到设计要求,就需要修改源代码或者选择不同速度的器件,直至满足设计要求,例如普通加法器改为超前进位加法器,普通乘法器改为 Booth 乘法器等等,通过减少关键路径来满足时序要求;

- 器件编程文件:如用于 FPGA 配置的 SOF,JAM,BIT 等格式的文件,用于 CPLD 编程的 JEDEC,POF 等格式的文件。由于布局布线与芯片的物理结构直接相关,所以一般选择芯片制造商提供的开发工具进行此项工作。

五、约束(Constraint)

约束分为综合约束(一级约束)和布局布线约束(二级约束),综合约束如资源共享约束(不同的约束将会导致生成不同性能的威廉希尔官方网站 ),布局布线约束又可以分为位置约束、时序约束。

约束,就是对这些操作环节定制规则,定制条件,比如引脚约束和时序约束;一般开发环境会对这些约束有个默认,这些默认的设置对大部分情况下还是适用的,但是通常布局布线约束中的 I/O 约束是我们每一个工程都必须给定的。

六、仿真(Simulation)

仿真指的是对所设计威廉希尔官方网站 功能的验证。仿真包括(功能)RTL 仿真、(门级)静态仿真和时序仿真。

- RTL 仿真:就是对你的 HDL 代码仿真,对你的 RTL 级描述的设计进行测试;RTL 仿真,又叫功能仿真,也称为前仿真,是在编译之前对用户所设计的威廉希尔官方网站 进行逻辑功能验证,此时的仿真没有任何延迟信息,是处于理想化状态的,例如对于一个寄存器(Register),它的输出端(Q Port)相对它的时钟输入端(Clk Port)的延时为零延时(Delta Delay),是仅对初步的功能进行验证的。

- 静态仿真:指对综合之后的 LUT 门级网表进行仿真;静态仿真,又叫门级仿真,也称为综合后仿真,在仿真时,把综合生成的标准延时文件 SDF 反标注到综合仿真模型中去,可估计门延时带来的影响,但不能估计线延时,此时的仿真也并不是十分准确,和布局布线后的实际情况还是有一定差距的。

- 时序仿真:在选择具体器件并完成布局布线后进行的包含延时的仿真;时序仿真,又叫布局布线后仿真,是指将布局布线的延时信息反标注到设计网表中来检测有无时序违规的现象(即是否满足时序约束条件或器件固有的时序规则,如建立时间、保持时间等等;而此时,不同器件的内部延时都不太一样,不同的布局、布线方案所生成的延时也不太一样);时序仿真包含的延迟信息最全,也最精确,能较好地反映芯片的实际工作情况。

从验证完整性而言,前端仿真和后端仿真均需要在项目中实施,而它们侧重的目标也有不同。前端仿真是为了检测出功能逻辑的缺陷,而后端仿真是为了检测出实际门级威廉希尔官方网站 中由于延时问题可能导致采样失败进而产生的功能缺陷。

七、编程配置(Program & Configuration)

编程配置就是生成比特流并载入 FPGA 芯片中的一个过程。

- 把布局布线后生成的编程文件装入 PLD 器件中的过程称为下载。

- 通常将对基于 EEPROM 工艺的非易失结构 CPLD 器件的下载称为编程;一般芯片编程是指产生使用的数据文件(如比特流文件(.bit)),然后将编程数据下载到 FPGA 芯片中。

- 而将基于 SRAM 工艺结构的 FPGA 器件的下载称为配置。

-

使用QUARTUS II做FPGA开发全流程,傻瓜式详细教程2012-03-08 0

-

例说FPGA连载8:FPGA开发流程2016-07-13 0

-

FPGA基本开发流程概述2019-01-28 0

-

FPGA开发流程简介2010-06-10 1740

-

FPGA开发流程及编程思想2016-01-18 523

-

FPGA开发流程2016-01-18 427

-

FPGA开发流程详细解析2018-01-12 10268

-

FPGA的设计流程是怎么样的?FPGA设计流程指南详细资料免费下载2018-10-17 1568

-

FPGA视频教程之FPGA开发流程的详细资料概述2019-03-01 1517

-

FPGA视频教程之NIOS II开发流程的详细资料说明2019-03-22 1526

-

FPGA教程之ISE设计流程简介的详细资料说明2019-04-04 1671

-

关于FPGA它的开发流程是怎样的2019-11-06 2466

-

FPGA的开发流程以及它的适用场景2019-11-20 1793

-

FPGA的开发流程及仿真技术解析2023-01-06 1904

全部0条评论

快来发表一下你的评论吧 !