时序约束连载02~时序例外

电子说

描述

本文继续讲解时序约束的第四大步骤——时序例外。

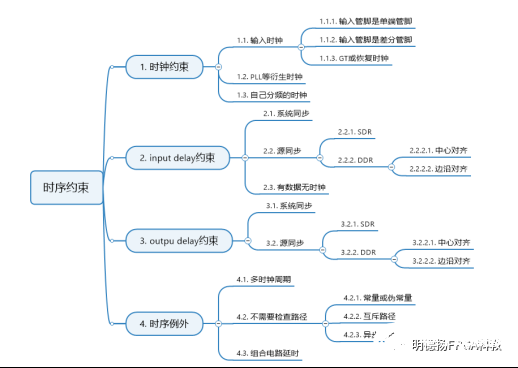

首先看一下图1,最后一步才进行时序例外的相关约束。再讲一下步骤,第一步是时钟约束,这一步会影响FPGA内部时序,第二步和第三步也会使用生成时钟的约束作为参考时钟约束输入输出端口。时钟约束完内部实际逻辑都没问题之后,第二步是input delay,第三步是output delay,这两步是对FPGA外围的接口进行约束。在外围接口约束都做好之后,才做最后一步,时序例外。

图1 时序约束步骤

时序例外就是指有些时序路径是不需要约束的,要把force掉的,或者有些情况是很特殊的。

时序例外做好之后,基本上项目就是完工的一个阶段。时序例外一般有几种情况,第一个是多周期的路径,第二个是不需要检查路径,一般要把这个路径force掉,而不需要检查路径又有三种情况,一种是常亮或伪常亮,第二种是互斥的路径或时钟,第三种是异步的时钟。最后是纯组合逻辑延时。

第1节 多周期路径

1.1、概述

第一种多周期的路径顾名思义,多周期路径其实就是指某个威廉希尔官方网站 路径不可能在一个时钟周期内完成,需要多个时钟周期才能得到正确结果,这时需要告知综合软件哪条路径需要几个时钟周期才能得到正确结果,综合软件根据约束条件对相应路径进行调整,常见的就是乘法器之类的。

1、多周期约束改变默认的setup和hold的默认检查方式。

2、设计中有些逻辑并不要求在单周期内完成稳定采样,在寄存器间不是按照连续时钟周期改变的时候就多时钟周期路径问题。

-通常出现在存在时钟使能信号的情况。

-从源寄存器、目的寄存器要求数据更新的时间是N个时钟周期

3、可以使得工具关注于更加难满足timing的path,便于时序收敛;工具更加关注于真实的关键路径。

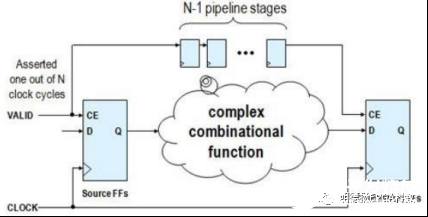

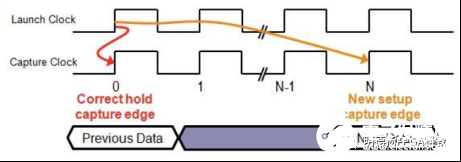

图2就是一个N个时钟周期的例子:

图2 多周期约束实例

1.2、创建多周期路径例外

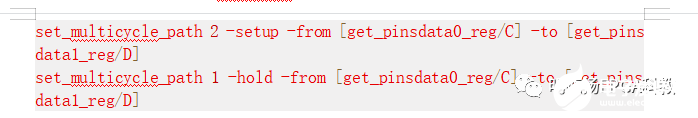

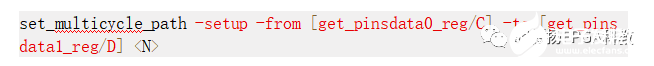

多周期路径通过set_multicycle_path命令进行定义:

set_multicycle_path

•

标志识别哪些路径使用多周期约束命令,可以使用-from、-through和-to。

• 决定静态时序检查的类型,是建立时间还是保持时间。

• 决定multicycle 路径有多少个时钟周期。

如上面两段代码,分别表示对建立时间和保持时间进行约束,其中从寄存器C到寄存器D的路径建立时间约束为需要两个时钟周期,保持时间需要1个时钟周期。

1.3、常规的建立保持时间检查

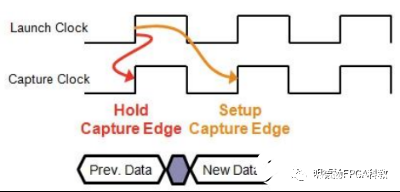

静态时序路径就是从一个时钟的元素开始和结束,并且是同一个时钟驱动的周期内,如图3所示。

图3 常见的建立时间、保持时间检查规则

—建立时间检查在启动时钟边缘后的目标1个时钟周期执行,也就是建立时间的发射沿launch edge和捕获沿capture edge一般情况下相差一个时钟周期。

—保持时间检查在启动时钟后的目标0时钟周期执行,保持时间的发射沿launch edge和捕获沿capture edge一般是重合的,后面讲保持时间概念时就清楚了。

而进行多周期约束后,这些路径的建立时间和保持时间检查规则会发生相应的改变,因为需要多个时钟周期才能完成相应的计算,那么建立时间的检查要求也就会对应的增加。

如下面约束:

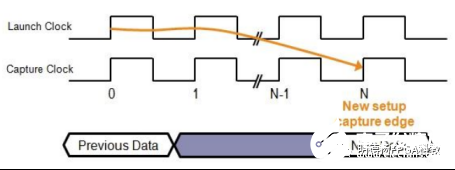

上面代码把寄存器C到寄存器D的路径设置为N个时钟周期,那么捕获沿setup capture edge 相对于发射沿launch edge会延迟N个时钟周期,如图4所示。其实不对建立时间进行多周期约束时,就是N=1。

图4 N周期建立时间多周期约束

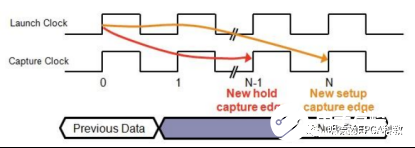

默认情况下保持时间的检查规则只会比建立时间的检查规则少一个时钟周期,这是在进行多周期约束时需要考虑的,如果寄存器C到寄存器D的路径只做了上面的N个时钟周期的建立时间约束,那么保持时间约束的检查规则将还是默认的,即保持时间的检查规则会变为N-1个时钟周期,如图5所示:

图5 不对保持时间约束的检查规则

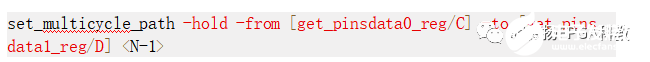

根据保持时间的概念,很明显图5的检查规则是错误的,原因是保持时间的目的是让下一个时钟的数据不会来得太快,将目前的有效数据刷新,导致数据丢失。为了弥补这个错误,还需要对相同路径的保持时间进行约束,使得保持时间的检查规则依旧为0个时钟周期。对应的命令如下:

上述命令会让该路径保持时间捕获沿提前N-1个时钟周期,与发射沿重合,如图6所示

图6 路径保持时间约束之后检查规则

上面只是一些简单的使用方式,多周期约束还可以用来调节信号的相位,比如SDRAM的接口时钟与内部工作时钟的相位关系,一般是将一个时钟经过反相器之后,相位相差90°的两个时钟分别作为接口时钟和内部工作时钟,其实这个步骤还可以使用多周期约束完成。

其实多周期约束在很多时候都是可以通过程序设计解决的,比如在程序中添加一些指示信号,或者打拍来完成多个周期的等待。所以明德扬一般不会用多周期约束,都是在程序设计时就会去考虑和解决这些问题,也推荐大家在设计时就去考虑这些延迟问题,不要等最后的时序约束才解决这些问题。

第2节 不需要检查路径

第二个不需要检查路径是重点讲解的内容,什么是不需要检查路径呢?第一种就是常量或伪常量信号。

什么叫常量或伪常量信号?比如一个单bit信号一般会有高低两种电平,会存在电平变换。但是也会存在一些信号会被赋值成常数,一直为高电平或者低电平,电平状态不会改变。所以通过其它时钟、跨时钟域处理的时候,其实是不需要处理的。因为它不会变,那在其他时钟上升沿时,该信号是不会变的,建立时间和保持时间是一直满足的,就不会有压稳态。这种情况下,该信号不会存在时序不满足的情况,常量或伪常量信号是不需要对它进行约束的,可以把它排除掉。

第二种是互斥的路径或时钟,其实就是双向端口,即双向端口inout 类型的端口,其输入路径与输出路径其实是没有关系的,故把它排除掉。

第三种是异步的时钟,是最常见的,也是FPGA肯定会用到,也一定要排除掉的。而且在任何一个项目里面,如果使用多个时钟,一定会用到的异步时钟处理。一般都会通过一些跨时钟域的处理方式之后,就可以做相关约束了。但把相关路径设置为不需要检查路径之前,一定要先对这写路径的时钟已经做跨时钟域处理。比如已经打了两拍,或者通过一个异步FIFO、双口RAM把它隔离了,否则这时候把它force 掉,就是会出现错误。

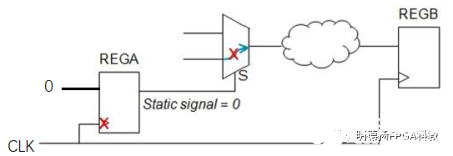

2.1 常量和伪常量信号

首先是常量或为常量信号,如图7,数据选择器的S端虽然是一个经过触发器输出的信号,但触发器REGA的输入信号一直为零,导致数据选择器的S端也一直为零。只要一直是零,那这个路径就可以把force 掉,即不用去分析该路径,包括经过这个数据选择器的路径也是不用分析的。

图7 实例

约束语句语法如下:

– set_false_path

–

表示约束的路径。

– 指定类型-setup 或者 –hold,不指定时建立setup和保持hold检查都受到影响

所以图7可以进行如下约束:

-set_false_path -from [get_cells REGA]

-set_false_path -through [get_pins_MUXA/I1]

其中第一句表示从REGA输出的信号都不需要检查时序,第二句表示综合软件对经过数据选择器的信号也不需要进行时序检查。

在一般情况下,如果是同一个时钟,可以也不用约束。但如果在跨时钟,而又没有做跨时钟域处理。其值是永远不会变的,就可以通过set false path这种约束方式来告知综合软件不用检查相关路径的时序。

2.2 互斥路径_双向端口

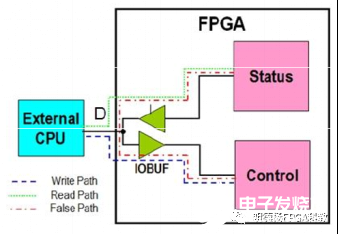

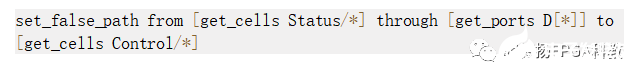

第二种是互斥路径,即双向端口。如图8的inout类型信号端口示意图,比如这个D端口是inout类型,那这种路径哪个是不需要分析的呢?

其实输入路径与输出路径对应的寄存器是不需要分析的,如图8中红色虚线所示路径是不需要分析的,绿色代表输出路径,而蓝色代表输入路径,这两条都是需要综合软件分析的,但是红色是输出经过D端口后到达输入寄存器的,所以该路径是不需要分析的。即从Status经过D端口到达Contorl的路径是不需要分析的。

图8 inout类型端口

相应的约束语句如下,从Status寄存器,经过D端口到达Control的信号都不需要检查其时序,其中*表示通配符。

2.3 异步时钟

第三个异步时钟,再强调一下,一般比较大的系统,不可避免会有多个时钟。多个时钟域下面的信号会存在交互,就会跨时钟域。综合软件在对设计进行综合和时序分析后,一般会对这些路径报错,提示开发人员这些路径存在时序违逆。这时候发现异步时钟域的信号肯定不能满足建立时间要求,但是一定要用不同的时钟,那怎么办呢?

一般会做异步时序处理,比如通过打两拍,把亚稳态出现的机率降低,或者是用异步FIFO、双口RAM把两个时钟域的信号同步。这样做了异步时钟域处理之后,综合软件仍然会报告这个时序不满足建立时间保证要求,那怎么办呢?

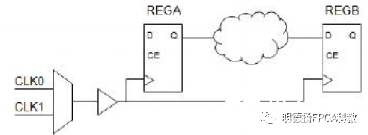

这时就可以把这个报告错误的路径给屏蔽掉,就是告知软件不要去分析了,这段路径已经人为处理过了,时序是没有问题的,如图9所示,这个系统会选择CLK0或者CLK1中的一个作为系统时钟,很显然时钟域CLK0到CLK1之间的路径是不需要进行分析的,可以使用set_false_path进行约束。

图9 多时钟域信号

这种会存在两种约束方式,方式一如下,表示综合软件从CLK0到CLK1、从CLK1到CLK0的路径都不需要分析。

set_false_path -from [get_clocks CLK0] -to [get_clocks CLK1]

set_false_path -from [get_clocks CLK1] -to [get_clocks CLK0]

方式二是通过set_clock_groups进行约束,如下所示,表示综合软件不需要检查CLK0与CLK1之间的路径。

set_clock_groups-physically_exclusive -group CLK0 -group CLK1

这样就可以正确的处理,综合软件不去对这些路径进行分析,也就会不会提示错误了。但强调一点,首先一定要做异步时序处理,然后才能把这个路径给force掉。假如没有做异步时序处理,而综合软件报告要说时序出错了,开发人员不对时序做处理,而是直接把这个报告给屏蔽掉了,这就是典型的解决不了问题就解决提出问题的人。后续系统功能出现问题,而综合软件报告的错误又被屏蔽了,这可能会出现灾难性后果。所以在使用set_false_path忽略路径的时候,特别是异步时钟,要特别小心。要确保真的做了时序处理,才能把相关路径force 掉。

语句相对简单,但非常重要,在不需要检查路径类型中,这个是最常见的,也是最重要的,也要小心处理的一种类型。

第3节 组合威廉希尔官方网站

延时

第三种情况就是组合逻辑延时。组合逻辑延时是什么情况?

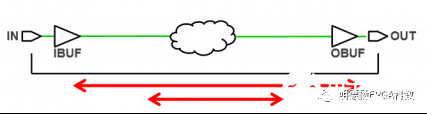

假如FPGA的两个端口,一个作为输入管脚,一个作为输出管脚。信号从输入管脚进入之后,会经过一些加法器、乘法器、减法器等组合逻辑威廉希尔官方网站 ,然直接从输出管脚输出。期间不会经过时序逻辑威廉希尔官方网站 ,即不会经过触发器,没有时钟参与,如图10所示。

图10 纯组合逻辑传输示意图

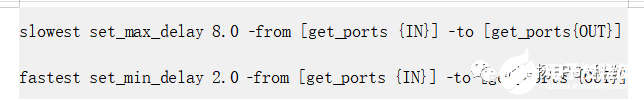

中间没有经过任何时钟的情况,此时需要告知综合软件这条路径的最大传输延迟和最小传输延迟是多少,即输入信号最快和最慢传输多久能得到输出。约束如下:

上述语句表示从IN端口到OUT端口最大延迟是8ns,即信号传输最慢的时候,需要8ns才能得到输出。最小延迟是2ns,即信号传输最快的时候,只需要2ns就能得到输出。一般这个延迟都不会很大,应该是没有影响的,也不推荐这种设计方式。

第4节 总结与建议

这是实际例外的情况,还是按照前面的顺序去找到对应情况,按要求进行约束。

内容最多的是多周期路径,做了简单的介绍。最核心是设置异步时序约束的内容,简单但重要且常用。

审核编辑:汤梓红

-

时序约束资料包2018-08-01 0

-

时序约束用户指南2010-11-02 594

-

工程师谈FPGA时序约束七步法2016-05-29 1234

-

FPGA的IO口时序约束分析2022-09-27 1744

-

时序约束之时序例外约束2018-09-21 0

-

时序约束与时序分析 ppt教程2010-05-17 773

-

FPGA时序约束方法2015-12-14 825

-

【时序约束资料包】培训课程Timing VIVADO2018-08-06 543

-

进行时序约束的方法都在这里,赶紧收藏2018-09-21 1587

-

正点原子FPGA静态时序分析与时序约束教程2020-11-11 2179

-

VIVADO时序约束及STA基础2022-03-11 9767

-

FPGA设计之时序约束2022-03-18 1667

-

浅谈时序设计和时序约束2023-07-04 1409

-

时序约束连载03~约束步骤总结2023-07-11 640

-

FPGA时序约束之时序路径和时序模型2023-08-14 808

全部0条评论

快来发表一下你的评论吧 !