基于FPGA的SPI Flash控制器的设计方案

描述

点击上方蓝字关注我们

摘要:传统的Flash读写是通过CPU软件编程实现,其读写速度较慢,且占用CPU资源,另外由于Flash芯片本身功能指令较多,使得对芯片进行直接操作变得非常困难。

本文提出一个基于FPGA的SPI Flash读写硬件实现方案,该方案利用硬件对SPI Flash进行控制,能够非常方便地完成Flash的读写、擦除、刷新及预充电等操作,同时编写的SPI Flash控制器IP核能够进行移植和复用,作为SOC芯片的功能模块。SPI Flash控制器采用VHDL语言进行编写,在Modelsim 6.5g上通过功能仿真,并且在XUPV5-LX110TFPGA开发板上通过硬件测试,实现结果表明方案的可行性。

1.引言

Flash是一种具有电可擦除的可编程ROM,按接口可以分为两大类:并行Flash和串行Flash.并行Flash存储量大,速度快;而串行Flash存储量相对较小,但体积小,连线简单,可减小威廉希尔官方网站 面积,节约成本。SPI Flash是内嵌SPI总线接口的串行Flash,它比起传统的并行总线接口Flash,节省了很多的I/O口资源,从而为系统功能的扩展提供了更多的可能。

随着SPI Flash越来越多地应用到各种领域,其传统读写方式中读写速度不够快、占用CPU资源以及操作不够简便灵活的缺点表现得更为突出,如何解决以上问题成为大家关注的焦点。利用硬件对SPI Flash进行控制,能够非常方便地完成Flash的读写、擦除、刷新及预充电等操作,且不占用CPU资源,同时编写的SPI Flash控制器IP核能够进行移植和复用,作为SOC芯片的功能模块。因此提出了一种基于FPGA的SPI Flash控制器的设计方案,并用VHDL实现。编写的SPI Flash控制器IP核在Modelsim 6.5g上进行了功能仿真,在FPGA开发板上进行了测试验证,可作为功能模块应用于SOC芯片设计。

2.SPI Flash控制器设计

2.1 SPI Flash芯片选择

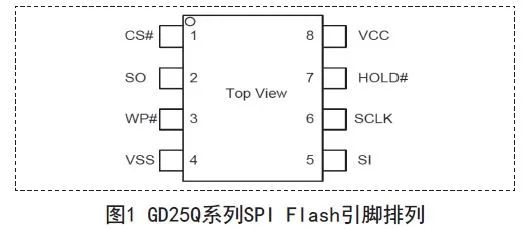

本方案SPI Flash芯片采用GigaDevice公司的GD25Q系列,GD25Q系列SPI Flash包括4Mbit的GD25Q40,2M bit的GD25Q20,1M bit的GD25Q10以及521K bit的GD25Q512,这里将采用512K bit的GD25Q512.图1为GD25Q系列SPIFlash(SOP8封装)引脚排列图。其中VCC和VSS分别为电源和地,其他6个引脚均可直接与F P G A的I / O引脚相连;写保护引脚W P #和HOLD#挂起引脚用于数据保护和空闲模式的低功耗运行,若不使用可将其置为高电平;CS#为片选信号,低电平时表示器件被选中,反之工作在待机状态;SO为串行数据输出,数据在时钟的下降沿输出到Flash器件;SI为串行数据输入,包括传输指令、地址和输入数据,输入信号在时钟的上升沿锁存到Flash器件中。SCLK为串行时钟,由FPGA提供。

2.2 SPI Flash指令操作

GDQ25系列SPI Flash指令较多,所有指令都是8位,操作时先将片选信号CS#拉低选中器件,然后输入8位操作指令字节,串行数据在片选信号CS#拉低后的个时钟的上升沿被采样,SPI Flash启动内部控制逻辑,自动完成相应操作。有些操作在输入指令后需要输入地址字节和伪字节,操作完成后再将片选信号拉高。

2.3 SPI Flash控制器设计原理

SPI Flash控制器必须能够产生SPI Flash芯片执行各操作(如写使能、刷新、预充电、读芯片ID、读取状态寄存器、写状态寄存器、扇区擦除、块擦除、整体擦除、读取数据、快速读取数据、页面编程)时所需指令时序,用户只需要输入对应操作的8位指令值及对应的操作地址值,SPI接口与SPI Flash的数据传输将由SPI Flash控制器内部状态机控制执行。

3.SPI Flash控制器实现

3.1 SPI Flash测试系统

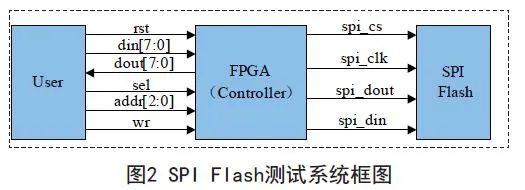

本文设计的SPI Flash测试系统由用户端、FPGA和SPI Flash构成,系统框图如图2所示,其中FPGA选用Xilinx公司Virtex5系列芯片(Virtex-5 XC5VLX110T),SPI Flash芯片采用GigaDevice公司的GD25Q系列512K bit容量的GD25Q512.

SPI Flash控制器由VHDL编写,主要为SPIFlash芯片提供串行时钟,将从用户端输入的数据(包括指令字节、地址字节和数据字节)寄存起来并在串行时钟的控制下通过spi_dout信号线逐位输出到SPI Flash芯片中,同样将从SPI Flash芯片中读出的串行数据转换成并行数据送给用户端。此外,SPI Flash控制器还必须在用户通过sel、addr以及wr组合发出的操作命令下产生一系列的控制信号,并在这些控制信号的作用下根据状态机的转换方向进行动作并且输出相应的结果。

3.2 SPI Flash控制器控制状态机

由于SPI Flash操作命令较多,并且很多操作命令之间存在相同的操作步骤,所以利用状态机进行控制能够准确有条理地完成对SPI Flash的操作。分析GDQ25系列SPI Flashdatasheet,可将SPI Flash控制器的工作状态划分为空闲状态(IDLE)、传输指令状态(TxCMD)、传输高字节地址状态(TxADD_H)、传输中间字节地址状态(TxADD_M)、传输低字节地址状态(TxADD_L)、传输伪字节状态(TxDummy)、传输数据状态(TxDATA)和接收数据状态(RxDATA)。除此以外,由于所有接收到的指令值都寄存在指令寄存器内,当一条指令执行完毕时需要将指令寄存器清空,以便接收下一条用户指令,所以设定一个清除指令状态(CLR_CMD)作为每一操作完成后的收尾状态。当状态机进入CLR_CMD状态后,表示当前操作已经完成,正将指令寄存器指令值清空;当状态机进入IDLE状态时,用户可输入下一操作指令,对SPI Flash进行下一操作。考虑到SPI Flash的响应时间,在以上工作状态中间插入了一些等待状态(WAIT)。

4.SPI Flash控制器验证

SPI Flash控制器IP核在Modelsim 6.5g上能够通过功能仿真,下面分析一下SPI Flash页面编程操作及数据读取操作的功能仿真。

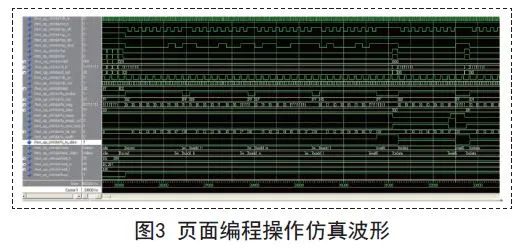

4.1 页面编程操作

页面编程操作仿真波形如图3所示,图中截取输入00H和01H数据的波形,多可连续输入一页256字节数据。当用户输入页面编程指令02H,状态机进入txcmd状态,页编程指令02H通过spi_dout传输给SPI Flash.当tx_bit_cnt计数到8时,指令传输完毕,状态机在等待后进入txadd_h状态,同时tx_bit_cnt被清零,需写入数据的对应存储空间的起始地址高字节值89H被传输。当tx_bit_cnt计数到8时,高字节地址值89H被传输完毕,状态机在等待后进入txadd_m状态,同时tx_bit_cnt被清零,同上,地址中间字节67H和45H被传输。当add_h、add_m和add_l寄存器的值依次传输完毕,状态机进入wait6状态,等待用户输入需写入SPI Flash的数据。当用户设定{sel,addr,wr}为10001b,状态机进入txdata状态,同时tx_new_data被置高,表示要传输新写入的数据。在txdata状态下,控制器将传输写入的第1字节数据00H,当tx_bit_cnt计数到8时,第1字节数据00H被传输完毕,tx_new_data被拉低,tx_empty被拉高,表示当前没有可传输的数据,状态机进入wait6状态,等待新数据写入。直到用户再次设定{sel,addr,wr}为10001b,状态机再次进入txdata状态,同时tx_new_data被置高,表示写入的第2字节数据01H将要传输。当tx_bit_cnt计数到8,第2字节数据传输完毕,tx_new_data被拉低,tx_empty被拉高,状态机进入wait6状态。由于GDQ25系列SPI Flash页面编程多可写入256字节数据,所以用户在写入数据时,应注意多写入256次数据,否则超过的数据将覆盖开始的数据。当状态机处于wait6状态而用户想结束页面编程时,可向控制器输入NOP指令强制结束当前页面编程操作。状态机在接收到NOP指令后将进入clr_cmd状态和idle空闲态,等待下一条指令的到来。当页面编程操作还没结束时,busy将一直被置高。

4.2 数据读取操作

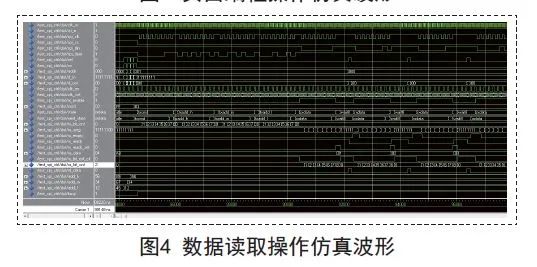

读数据指令仿真波形如图4所示。当用户输入读数据指令03H,状态机进入txcmd状态,读数据指令通过spi_dout传输给SPI Flash.

当tx_bit_cnt计数到8时,指令传输完毕,状态机等待后进入txadd_h状态,传输要读出数据所在存储空间起始地址的高字节,同时tx_bit_cnt清零,以为下一个传输作准备。地址高字节寄存器add_h数值56H通过spi_dout传输给SPI Flash,当tx_bit_cnt计数到8时,状态机进入txadd_m状态,传输地址中间字节,同理,控制器在状态txadd_m和状态txadd_l状态下完成传输地址中间字节34H和地址低字节12H.当24位地址传输完毕,状态机在等待后进入rxdata状态,接收从spi_din输入的字节数据01H.当rx_bit_cnt计数到8时,控制器完成第1字节数据的接收,rx_data显示为01H,状态机状态转换为wait8状态,等待用户设定{sel,addr,wr}以接收第2字节。当用户设定{sel,addr,wr}为10000b时,状态机再次进入rxdata状态,接收从spi_din输入的第2字节数据02H,同时rx_ready被拉低,rx_empty被拉高,rd_data被拉高,表示将要读出新输入的数据。当rx_bit_cnt计数到8时,第2字节数据接收完毕,rx_ready被拉高,rx_empty为低,rd_data显示新接收的字节数据02H,状态机经等待后重新进入wait8状态,等待用户再次设定{sel,addr,wr}值,接收第3字节数据值,同理,可读出SPI Flash内部所有数据。

当状态机处于wait8状态而用户想退出读数据操作时,可向控制器输入NOP指令强制结束当前读数据操作。状态机在接收到NOP指令后将进入clr_cmd状态和idle空闲态,等待下一条指令的到来。当读数据操作还没结束时,busy将一直置高。

5.结语

目前SPI Flash控制器IP核已经在XUPV5-LX110T FPGA开发板上通过硬件测试,并且将作为功能模块应用于SOC芯片设计。实践证明,基于FPGA的SPI Flash控制器能够简化SPI Flash读写操作流程,从而提高SPI Flash的读写速度,而操作时不占用CPU资源的特点,将使SPIFlash的读写更有优势

有你想看的精彩 至芯科技-FPGA就业培训来袭!你的选择开启你的高薪之路!7月12号北京中心开课、欢迎咨询! 解析高速ADC和DAC与FPGA的配合使用 FPGA管脚调整的注意事项

扫码加微信邀请您加入FPGA学习交流群

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:基于FPGA的SPI Flash控制器的设计方案

文章出处:【微信公众号:FPGA设计william hill官网 】欢迎添加关注!文章转载请注明出处。

- 相关推荐

- FPGA

-

求一种基于FPGA的HDLC协议控制器设计方案2021-04-30 0

-

求一种基于FPGA的永磁同步电机控制器的设计方案2021-05-08 0

-

分享一种基于Actel Flash FPGA的高可靠设计方案2021-05-10 0

-

采用Actel FPGA的TFT控制器技术设计方案2010-04-19 1147

-

SPI方式FPGA配置和SPI flash编程2011-05-16 963

-

基于DSP+FPGA的磁铁电源控制器的设计2012-07-27 961

-

基于FPGA的SPI Flash控制器的设计方案2013-09-24 6156

-

磁铁电源控制器的设计方案分析2017-10-21 1058

-

基于FPGA的FLASH控制器设计2017-11-13 774

-

基于FPGA 的SPI Flash 控制器设计及验证2017-11-22 13438

-

基于FPGA三相正弦波pwm控制器的设计方案资料下载2018-04-08 1474

-

基于MOS管的箭载时序控制器设计方案2021-06-29 698

-

ADI-ADuM隔离DCDC控制器参考设计方案2021-09-17 1036

-

ADIDAuM隔离DCDC控制器参考设计方案2021-09-17 874

全部0条评论

快来发表一下你的评论吧 !