如何充分利用Emulation和FPGA效果才能翻倍呢?

EDA/IC设计

描述

随着芯片规模和系统代码越来越复杂庞大,产品的上市时间不断面临挑战。这导致原本应在硅后进行的工作不得不在硅前就要开始,也就是设计策略的“左移”。尤其在最近几年,随着亚马逊、苹果、腾讯、阿里等系统厂商放弃通用芯片,转而开始制造符合自己系统需求的芯片,尽早对系统进行验证的需求也越来越高。

当系统验证 “左移”到RTL设计阶段,设计团队利用硬件仿真加速(以下统称Emulation)和FPGA原型验证(以下统称FPGA)可以提前进行系统验证。虽然同为验证,这两种验证方法在原理上还是有一些差异,但使用起来彼此互补,增加了整个验证流程的完备性。本文将主要介绍二者各自的优势和局限性,以及设计团队应如何充分利用Emulation和FPGA,发挥其协同效应。

Emulation和FPGA的优势和局限

不同于FPGA,硬件加速器的容量是非常大的 ,可以做大规模芯片的验证。以Palladium为例,它的最小粒度是等价的四百万逻辑门,而最大的容量可达到上百亿门。同时,它的查错定位能力较强,类似Simulation的形式,所有的信号、逻辑层级都是可见的,查错定位过程中支持关联一些其它工具做联合debug,它抓的波形长度也是百万cycle级的。

然而,Emulation也有其局限性,比如其运行速度依然无法跟原型验证相比,另外还有其高昂的硬件和维护费用。 威尔逊研究小组的调查发现从2012到2020年,在所有ASIC芯片流片失败的案例中,近一半原因是逻辑和功能性的缺陷。

相比工程师依靠软件模拟来验证其硬件设计是否正确,在FPGA真实环境上运行是确保其功能正确的可靠方法。

同时,FPGA也是系统验证(systemvalidation)和软件调试的必用工具,其运行速度比硬件仿真加速器快,而且硬件价格也远远低于市面上主流的加速器,但FPGA也有其明显的局限性,在复杂芯片设计中,不可替代其他验证手段而单独使用。

首先,单片FPGA的容量较小,即便使用最新型号,可容纳的逻辑门规模大概是几千万门左右。如果芯片设计非常大,就需要多片FPGA互联,然而这样会涉及到分割即partition。有一些原型验证的产品是可以支持自动化的partition,但是很多时候还是需要人工去做partition,这个过程虽然可以提高性能和布局布线成功率,但是非常耗时。

其次,原型验证的查错定位能力是比较弱的,在FPGA上做全面的查错定位需要预埋信号,预埋的信号有限且每次修改需要重新布局布线,整个过程迭代时间是非常长的。

在实际验证执行过程中,这两种验证方式互为补充。FPGA速度快,可能达到几兆或者几十兆的速度,更适合于RTL比较成熟之后,做系统验证和软硬件协同验证。

硬件仿真加速器容量大,可以做大规模芯片的仿真,而且由于其查错定位能力强,适用于早期代码还不是特别稳定的时候,可以做快速迭代,迭代速度甚至可以做到一天迭代两三次,这样就可以更早开展软硬件协同验证。

强强联合,优势互补

Emulation和FPGA目前已经成为主流验证方式,然而,在验证人员和验证经验不足的情况下,厂家依然会面临如何选型?是自己开发FPGA board,还是用商用平台?验证团队如何搭建等问题。针对这些疑问,英诺达推出的EnCitiusSVS系统验证平台可以帮助客户克服挑战,推进项目进度。

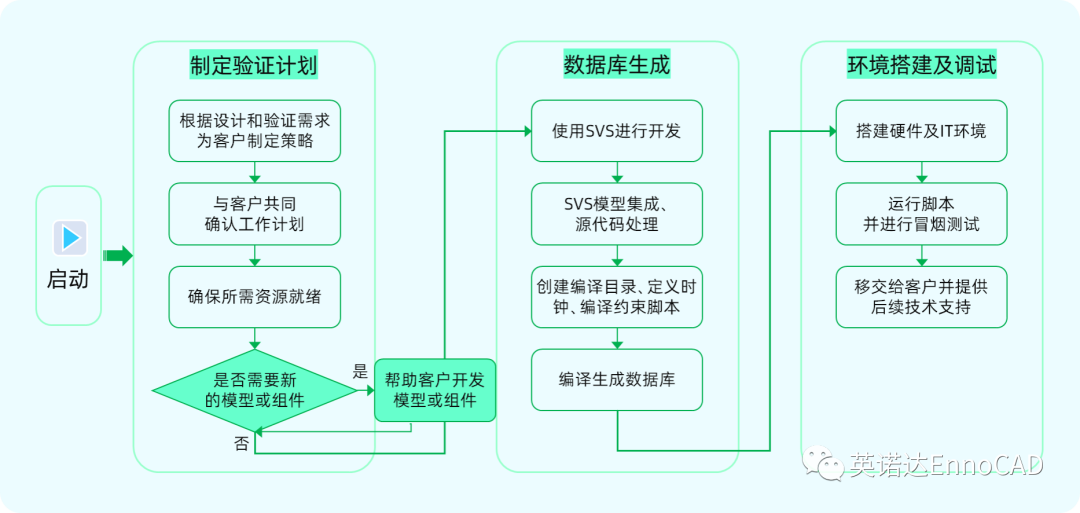

SVS系统验证平台是SoC及系统相关验证的集成式全栈解决方案,该云平台采用业界领先的通用高性能服务器、硬件仿真加速器和原型验证平台,通过英诺达自主研发的验证流程和专业的设计验证服务团队,可以为客户提供全流程搭建,加速仿真验证效率,提高硬件利用率。对于从未接触过硬件仿真加速或者原型验证平台的客户,英诺达还可以提供从早期验证策略制定,到整个环境构建方案的一站式服务,客户只需要专注于威廉希尔官方网站 和代码设计。

SVS平台一次集成即可快速切换

基于重用性实现的快速移植

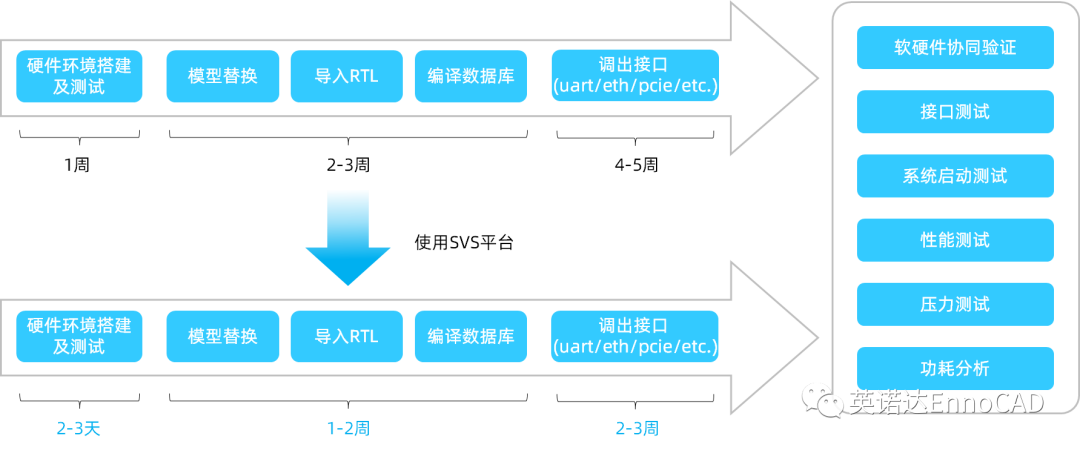

重用性(reuse)是验证中提到的高频词,可以大大增加验证的效率,节省人力资源。工程师们希望环境开发出来以后可以在Simulation、Emulation和FPGA平台上做快速移植。SVS平台在这方面做了自动化处理,提高了环境的重用性,比如在Emulation和FPGA的切换过程中,通过SVS平台只做一次开发的组件集成,编译过程中可以通过简单的option切换Emulation或FPGA的代码,客户可以在两个平台上进行快速切换。同时,英诺达在编译脚本上也增加了重用性,生成的编辑脚本的目录结构、编译命令都是高度统一的。举例来说,从Emulation移植到FPGA的时候,客户只需要做很小的改动,就可以拿去编译了。

充分利用资源,发挥综合优势 SVS平台综合了仿真加速和原型验证的优势,通过快速移植,可以提高硬件的利用效率,从而提高整个工程师团队的效率。举例来说,为了充分利用Emulation的查错定位能力,SVS可以把FPGA的环境移植到Emulation上,问题可以很快复现出来,然后利用Emulation的信号全可见去查错定位。

SVS平台缩短环境调试时间

扩充验证的组件和解决方案

此外,SVS平台通过统一和简化组件集成接口,实现了不同验证平台组件快速集成,结合易用的集成工具和转换脚本,快速完成组件集成,减少了验证环境构建的时间。通过SVS工具可以生成golden的各类接口组件,实现Emulation环境和FPGA环境的快速搭建,可以有效缩短bring up的时间。SVS做了很多自动化处理,客户使用过程中不需要担心底层具体的环境实现。

而对于使用平台前的一些操作,比如不可综合模型的替换,环境组件的集成和porting等,这些客户可以自己做,也可以交由英诺达做相关设计服务。另外,英诺达也会给客户提供SVS平台完整的培训,包括如何做网络接入、如何加载、编译、查错定位等等。

当前芯片规模越来越大,周期越来越紧,SVS平台旨在提供完整可靠的解决方案,提高客户的效率,将宝贵的验证人力资源投入到验证执行阶段而非环境搭建及调试阶段。

审核编辑:刘清

-

让你的内存每秒都能充分利用:内存释放专家2009-06-01 0

-

如何充分利用光纤配线箱?2016-09-13 0

-

如何充分利用这些频谱资源2019-07-11 0

-

怎么才能发挥FPGA设计的无限潜力呢?2019-08-01 0

-

在XC7K325T FPGA中如何充分利用GTX资源?2020-07-22 0

-

开关电源转换器中如何充分利用SiC器件的性能优势?2021-02-22 0

-

如何充分利用电子设计工具呢2021-12-31 0

-

并行编程无进展使多核芯片未能充分利用2010-04-01 733

-

充分利用超级大写电脑2021-05-21 504

-

超级电容器完全耗尽电能如何得到充分利用2022-02-06 1972

-

APS排程助动力电池企业充分利用产能2022-10-20 750

-

IGBT厂商扩产,APS生产排产帮助企业充分利用设备产能2022-11-03 757

-

充分利用电位计 — 别让旋转乱套!2022-11-07 542

-

在MCU开发中如何充分利用各种类型的断点?2023-09-18 647

-

如何充分利用单片机(MCU)的非易失性存储器呢?2023-12-15 1505

全部0条评论

快来发表一下你的评论吧 !