什么是CoWoS?CoWoS的应用发展

制造/封装

512人已加入

描述

过去数十年来,为了扩增芯片的晶体管数量以推升运算效能,半导体制造技术已从1971 年10,000nm制程进步至2022年3nm 制程,逐渐逼近目前已知的物理极限,但随着人工智能、AIGC等相关应用高速发展,设备端对于核心芯片的效能需求将越来越高;在制程技术提升可能遭遇瓶颈,但是运算资源需求持续走高的情况下,透过先进封装技术提升芯片之晶体管数量就显得格外重要。

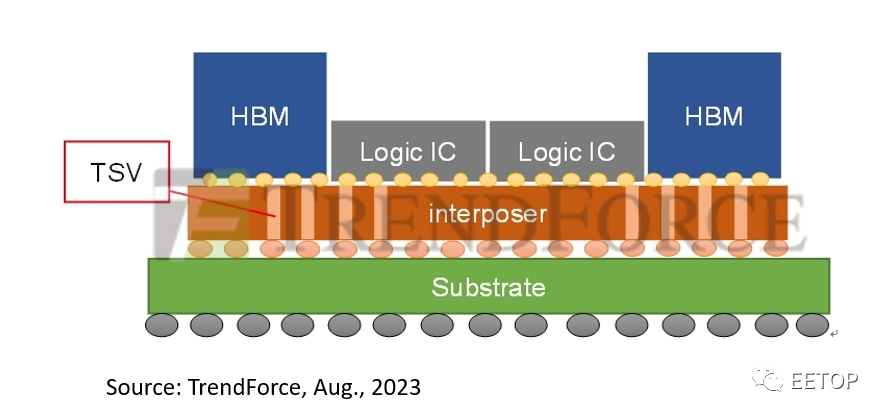

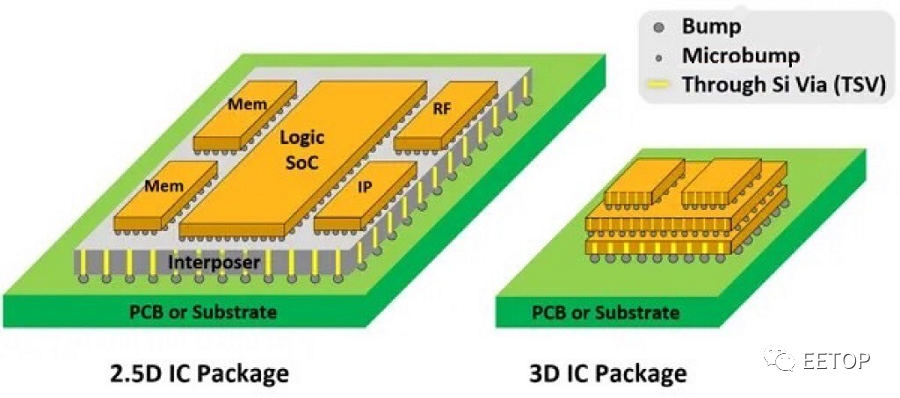

而2.5D 与3D 封装技术则是差别在堆叠方式。2.5D 封装是指将芯片堆叠于中介层之上或透过硅桥连结芯片,以水平堆叠的方式,主要应用于拼接逻辑运算芯片和HBM;3D 封装则是垂直堆叠芯片的技术,主要面向高效能逻辑芯片、SoC 制造。

▲2.5D和3D封装的差异(图片来源:Ansys)

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

什么是CoWoS封装技术?2024-08-08 3399

-

润欣科技与奇异摩尔签署CoWoS-S封装服务协议2024-10-30 980

-

台积电CoWoS订单增加 生产线满载运行2020-04-12 2785

-

如何区分Info与CoWoS封装?2023-06-20 3130

-

如何区分Info封装与CoWoS封装呢?2023-06-20 6520

-

全面详解CoWoS封装技术特点及优势2023-07-11 8883

-

CoWoS和HBM的供应链分析2023-07-30 2339

-

CoWoS先进封装是什么?2023-07-31 3843

-

chiplet和cowos的关系2023-08-25 3495

-

报告称台积电改机增CoWoS产能 预估明年倍增2023-11-08 690

-

AMD寻求CoWoS产能,以拓展AI芯片市场2024-01-03 631

-

CoWoS封装产能限制AI芯片出货量2024-01-19 917

-

什么是 CoWoS 封装技术?2024-06-05 529

-

CoWoS工艺流程说明2024-10-18 469

-

CoWoS先进封装技术介绍2024-12-17 338

全部0条评论

快来发表一下你的评论吧 !